Visão geral

Com um fluxo de projeto simplificado, o Vivado Design Suite permite que os desenvolvedores de FPGA tradicionais obtenham fechamento de projeto rapidamente com os SoCs adaptativos Versal

Atenda às metas FMAX

Os novos algoritmos de P&R e clocking permitem que os projetistas atendam aos prazos dos projetos mais complexos.

Compilação rápida e inicialização flexível

Reduza o tempo de compilação1,2 e inicialize o PS primeiro para fechamento rápido do projeto e ativação do sistema.

Fluxos de RTL de nível superior

Use fluxos de RTL tradicionais para desbloquear o desempenho do sistema em dispositivos Versal.

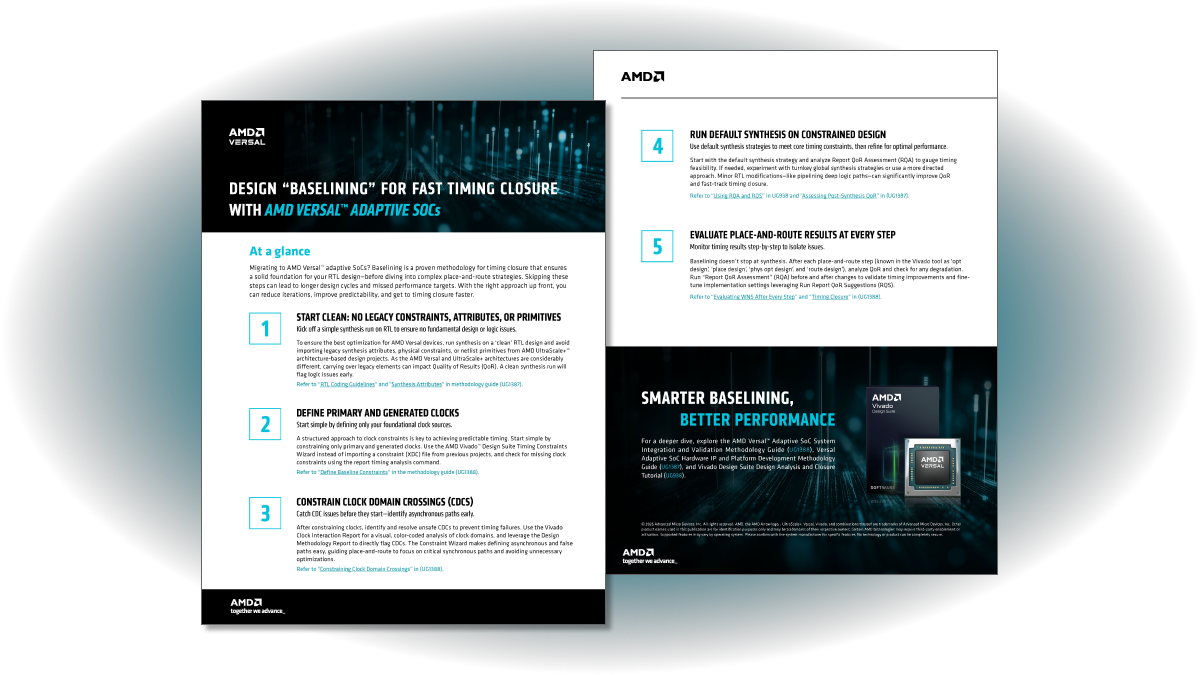

Melhore a qualidade dos resultados com os SoCs adaptativos AMD Versal™

Melhorias no Vivado para o Versal

Melhoria média de desempenho em 2024.1 3,4

Atenda às metas FMAX

Os SoCs adaptativos Versal™ permitem um novo paradigma de projeto de sistema ao mesmo tempo em que desenvolvem metodologias comprovadas de FPGA. Os recursos da arquitetura Versal e do Vivado Design Suite para alcançar o encerramento de temporização incluem:

- Fluxos de compilação que reduzem o congestionamento de roteamento

- Calibração automática das regiões do clock para minimizar a distorção do clock

- Nova tecnologia de buffer de clock para redução da distorção direcionada

- Conectividade avançada de matriz para matriz para dispositivos baseados em SSIT

As mais recentes melhorias nas ferramentas do Vivado, juntamente com recursos de chips incorporados, permitem que a automação e o controle do usuário atendam ao encerramento de temporização.

Aprimoramentos no tempo de compilação1,2

Compilação rápida

Os SoCs adaptativos Versal™ fornecem recursos lógicos maiores e IP rígido para projetos mais complexos. Mas, com o aumento da complexidade, os tempos de compilação são potencialmente longos. O Vivado Design Suite™ agora apresenta o Advanced Flow para acelerar a compilação em até 2 vezes em relação às versões anteriores com aprimoramentos em cada estágio de implementação:

- Particionamento automático para local e rota paralelos

- Posicionamento mais inteligente para reduzir o congestionamento

- Algoritmos avançados de roteamento para um fechamento de tempo mais rápido

Fluxos de RTL de nível superior

Com os SoCs adaptativos Versal, os desenvolvedores de hardware podem mapear seus projetos usando uma abordagem de sistema baseada em blocos usando o integrador de IP ou permanecer em seu RTL de nível superior para facilitar a migração de projetos de FPGA da geração anterior usando dois novos recursos:

- O fluxo NoC modular facilita a entrada do projeto, permitindo a instanciação por meio de ambientes integradores RTL e IP usando uma abordagem no nível do sistema.

- O novo assistente de transceptores Versal fornece um RTL wrapper criado em torno dos GTs primitivos e permite a personalização básica.

Embora o integrador de IP ainda seja aproveitado para vários blocos de IP no fluxo do SoC adaptativo Versal, o fluxo de RTL de nível superior permite flexibilidade na importação de projetos com topologias complexas.

Inicialização flexível do processador

O Vivado Design Suite oferece opções para configurar o sistema de processamento para inicializar primeiro para aplicativos que precisam de inicialização rápida do sistema operacional, controle de sequenciamento de potência estrito ou reconfiguração dinâmica do PL sem interromper o tempo de execução do software. O novo fluxo de configuração segmentada:

- Inicializa primeiro os processadores, a memória e o sistema operacional

- Transfere a configuração do PL para um estágio posterior

- Fornece um PL PDI (arquivo de configuração) via Linux® ou U-Boot em tempo de execução

A configuração segmentada está disponível na versão 2025.1. Consulte os tutoriais do GitHub para obter mais detalhes.

Recursos

Webinars e tutoriais em vídeo

Tutoriais do GitHub

Cursos de treinamento

Documentação

Vivado Design Suite

Baixe a versão mais recente do Vivado Design Suite para acessar os recursos mais recentes

Power Design Manager

Baixe a versão mais recente para garantir dados precisos de potência para dispositivos UltraScale+ e Versal

Fale conosco

Inscreva-se para receber as últimas notícias sobre ferramentas de hardware ou entre em contato com um especialista do Vivado Design Suite para tirar dúvidas ou receber feedback

Notas de rodapé

- Com base em um cenário de teste único realizado pela AMD em dezembro de 2024, medindo os tempos médios de compilação (horas/minutos) em mais de 124 projetos direcionados a dispositivos com a tecnologia SSI (Stacked Silicon Interconnect) da Versal usando o Vivado Design Suite 2024.2 em comparação com o Vivado Design Suite 2024.1. Os resultados de tempo de compilação variam de acordo com o dispositivo, o projeto, a configuração e outros fatores (VIV-011)

- Com base em um cenário de teste único realizado pela AMD em dezembro de 2024, medindo os tempos médios de compilação (horas/minutos) em mais de 151 projetos direcionados a dispositivos monolíticos Versal usando o Vivado Design Suite 2024.2 em comparação com o Vivado Design Suite 2024.1. Os resultados de tempo de compilação variam de acordo com o dispositivo, o projeto, a configuração e outros fatores. (VIV-010)

- Com base no teste de desempenho do pior slack negativo da AMD em abril de 2025, usando o Vivado Design Suite 2024.2 em comparação ao 2024.1. Os resultados declarados são uma média geométrica de 153 projetos monolíticos. Os resultados podem variar de acordo com o dispositivo, o projeto, a configuração, o software e outros fatores (VIV-013)

- Com base no teste de desempenho do pior slack negativo da AMD em abril de 2025, usando o Vivado Design Suite 2024.2 em comparação ao 2024.1. Os resultados declarados são uma média geométrica de 125 projetos de SSI. Os resultados podem variar de acordo com o dispositivo, o projeto, a configuração, o software e outros fatores (VIV-014)

- Com base em um cenário de teste único realizado pela AMD em dezembro de 2024, medindo os tempos médios de compilação (horas/minutos) em mais de 124 projetos direcionados a dispositivos com a tecnologia SSI (Stacked Silicon Interconnect) da Versal usando o Vivado Design Suite 2024.2 em comparação com o Vivado Design Suite 2024.1. Os resultados de tempo de compilação variam de acordo com o dispositivo, o projeto, a configuração e outros fatores (VIV-011)

- Com base em um cenário de teste único realizado pela AMD em dezembro de 2024, medindo os tempos médios de compilação (horas/minutos) em mais de 151 projetos direcionados a dispositivos monolíticos Versal usando o Vivado Design Suite 2024.2 em comparação com o Vivado Design Suite 2024.1. Os resultados de tempo de compilação variam de acordo com o dispositivo, o projeto, a configuração e outros fatores. (VIV-010)

- Com base no teste de desempenho do pior slack negativo da AMD em abril de 2025, usando o Vivado Design Suite 2024.2 em comparação ao 2024.1. Os resultados declarados são uma média geométrica de 153 projetos monolíticos. Os resultados podem variar de acordo com o dispositivo, o projeto, a configuração, o software e outros fatores (VIV-013)

- Com base no teste de desempenho do pior slack negativo da AMD em abril de 2025, usando o Vivado Design Suite 2024.2 em comparação ao 2024.1. Os resultados declarados são uma média geométrica de 125 projetos de SSI. Os resultados podem variar de acordo com o dispositivo, o projeto, a configuração, o software e outros fatores (VIV-014)