400G IEEE 802.3bs Reed Solomon Forward Error Correction

发布者: AMD

LogiCORE™ 400G IEEE 802.3bs Reed-Solomon Forward Error Correction IP 核可实现 Reed-Solomon Forward Error Correction (RS-FEC) 子层。

- 产品编号:

- EF-DI-400G-RS-FEC-PROJ

- EF-DI-400G-RS-FEC-SITE

- 设计工具支持: Vivado Software

- 许可: Core License Agreement

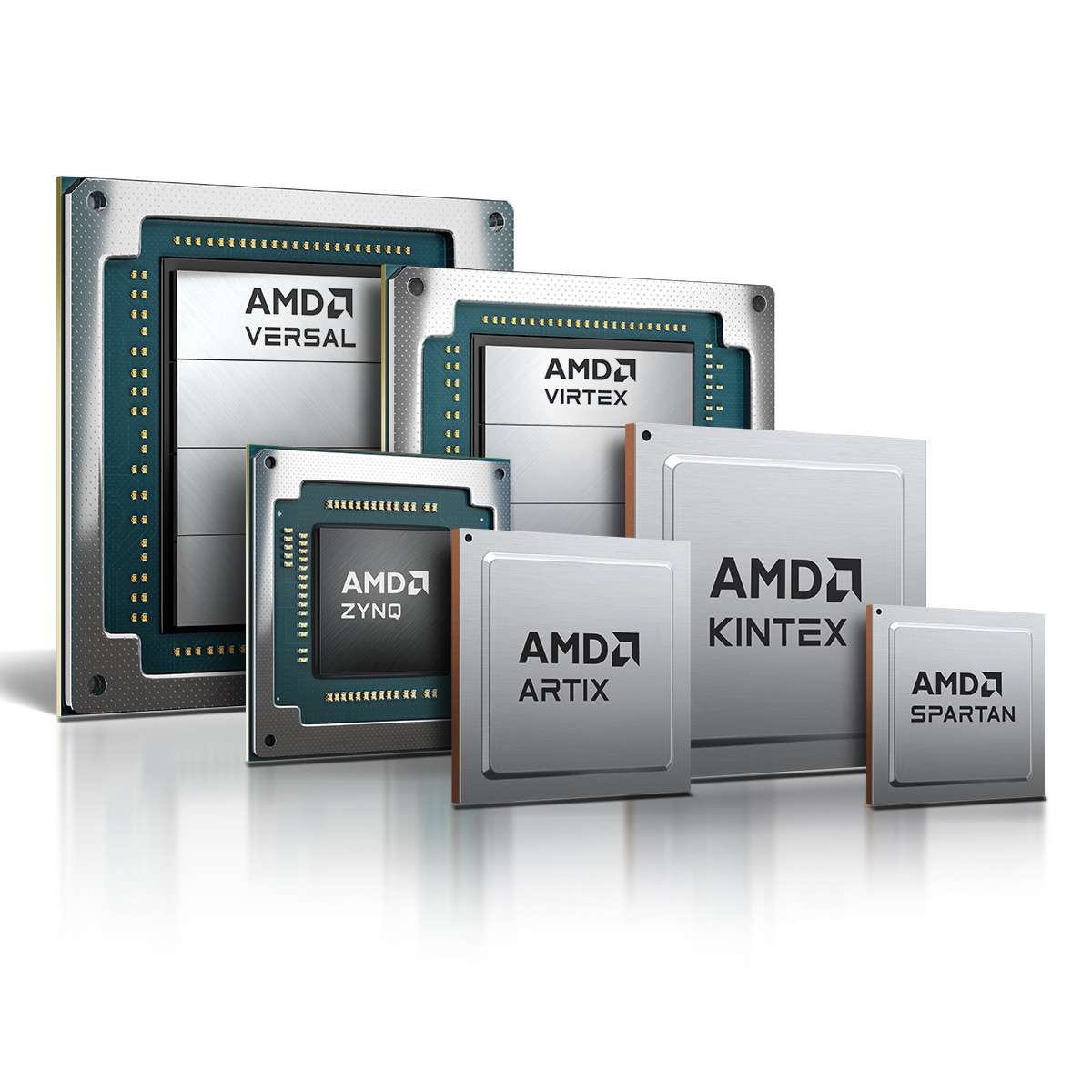

- 器件支持: Kintex UltraScale, Kintex UltraScale+, Virtex UltraScale, Virtex UltraScale+, Versal AI Core, Versal Prime