Versal™ Adaptive SoC Programmable Network on Chip and Integrated Memory Controller

发布者: AMD

AMD Versal™ Programmable Network on Chip (NoC) 是一种 AXI 互连网络,用于在可编程逻辑 (PL)、处理系统 (PS) 和硬化 DDR4/LPDDR4 存储器控制器的 IP 端点之间共享数据。

- 设计工具支持: Vivado Software

- 捆绑产品: Vivado Software

- 许可: End User License Agreement

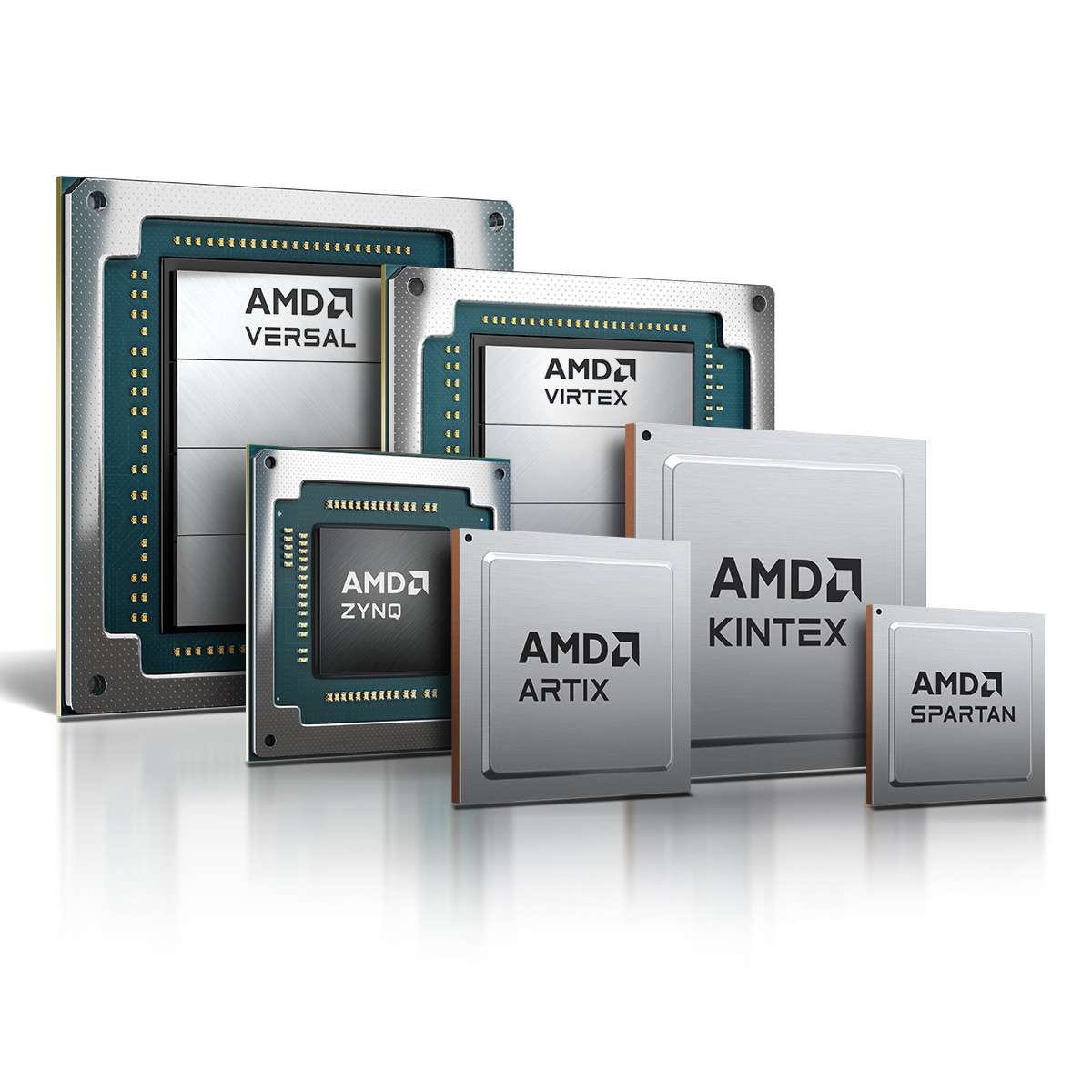

- 器件支持: Versal AI Core, Versal Prime