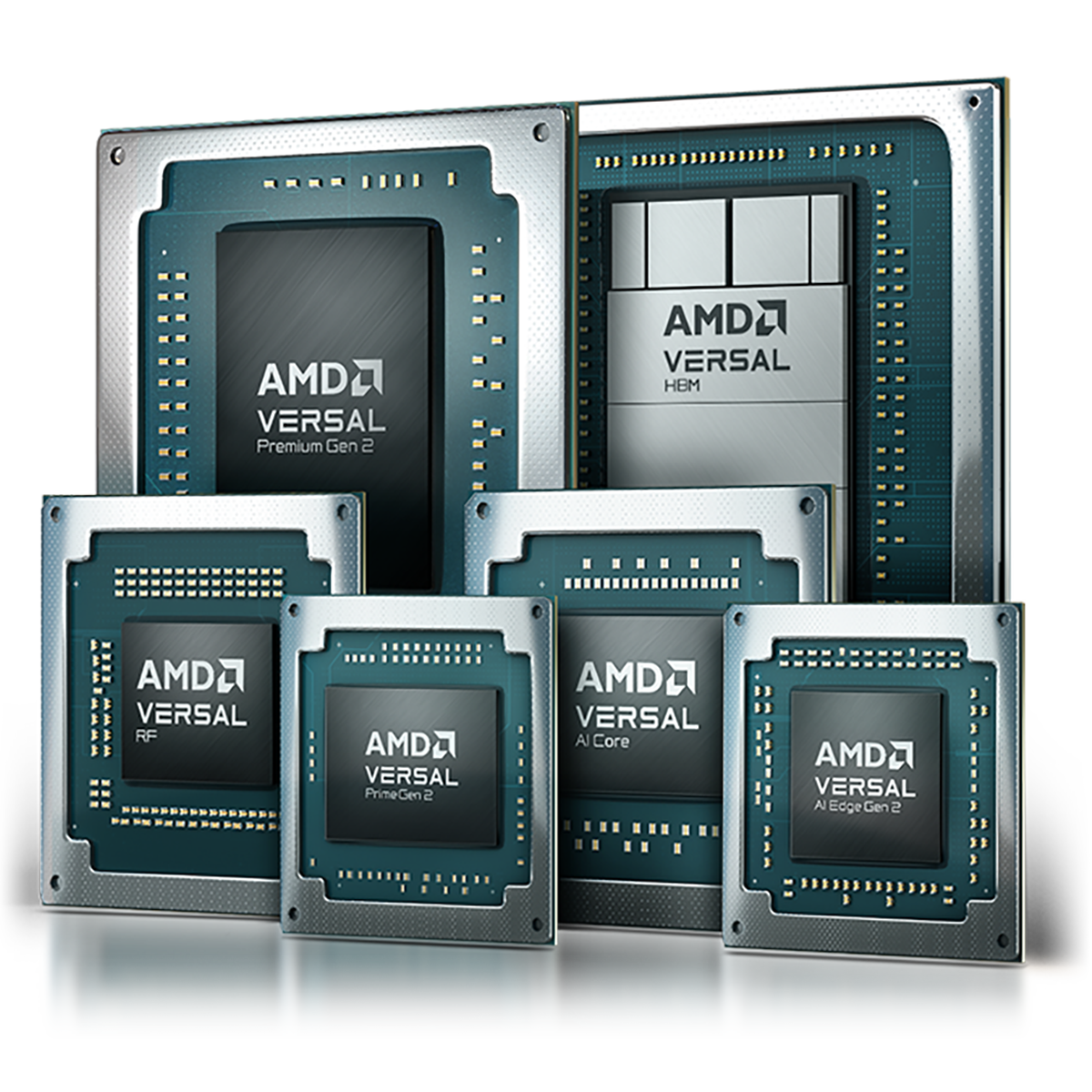

面向各类应用的自适应 SoC

AMD Versal™ 自适应 SoC 集成的功能远远超过常规 CPU、GPU 和 FPGA,可实现面向特定领域的自适应架构,助力加速各类应用的整体性能。

卓越性能与超低功耗

本白皮书着眼边缘和云端应用、有线网络以及 5G/6G 无线基础设施等多个市场,全方位分析 Versal 自适应 SoC 的系统级功能。

基于可通过公共工具进行验证的可靠数据,了解 Versal 架构与传统 10nm FPGA 架构相比,如何在 AI 推理、海量 MIMO、网络加速、存储以及多太比特 SmartPHY 等终端应用中实现卓越的性能功耗比。

AMD Versal 自适应 SoC 虽然采用经过实践检验的 FPGA 方法,但开创了一种全新的系统设计范式。Versal 架构是一种完全软件可编程的异构计算架构,具有广泛的硬核 IP。

AMD 既提供通用型自适应 SoC 器件,也提供具有专用功能的 SoC 器件,包括用于 DSP 和机器学习工作负载的 AI 引擎、集成式 RF-ADC/RF-DAC、众多 DSP 硬核 IP 或高带宽存储器。

内置芯片功能结合优化的设计流程以及 Vivado™ 工具的全新增强功能,助力实现自动化和用户控制,从而达成突破性的系统级性能功耗比。

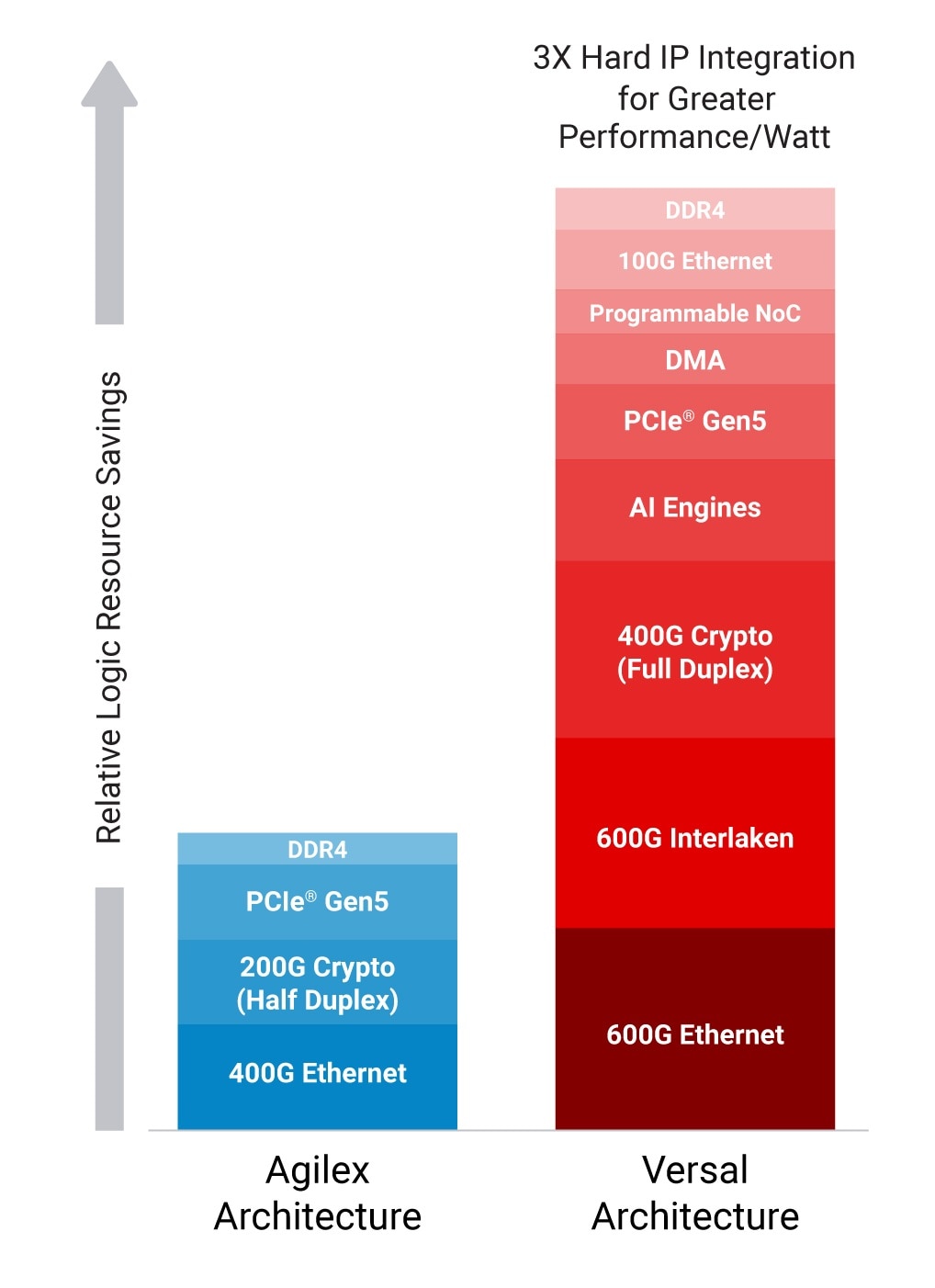

Versal 自适应 SoC 的硬核 IP 数量是传统 10nm FPGA 的 3 倍之多,一方面所有器件采用通用基础设施(如可编程 NoC)以便于编程和代码移植,另一方面则针对不同市场提供领域专用的硬核 IP。

在可编程逻辑与硬核 IP 之间取得良好平衡,不仅可为云端、网络和边缘的高级应用实现卓越的性能功耗比,同时还可保持硬件灵活性以适应不断变化的需求和市场动态。

验证白皮书 WP539 中引用的 AMD Versal 与传统 FPGA 基准测试数据,对比两者的表现情况

*注册申请需符合相关条件

加入 Versal 产品组合通知列表,即可第一时间获取最新信息。