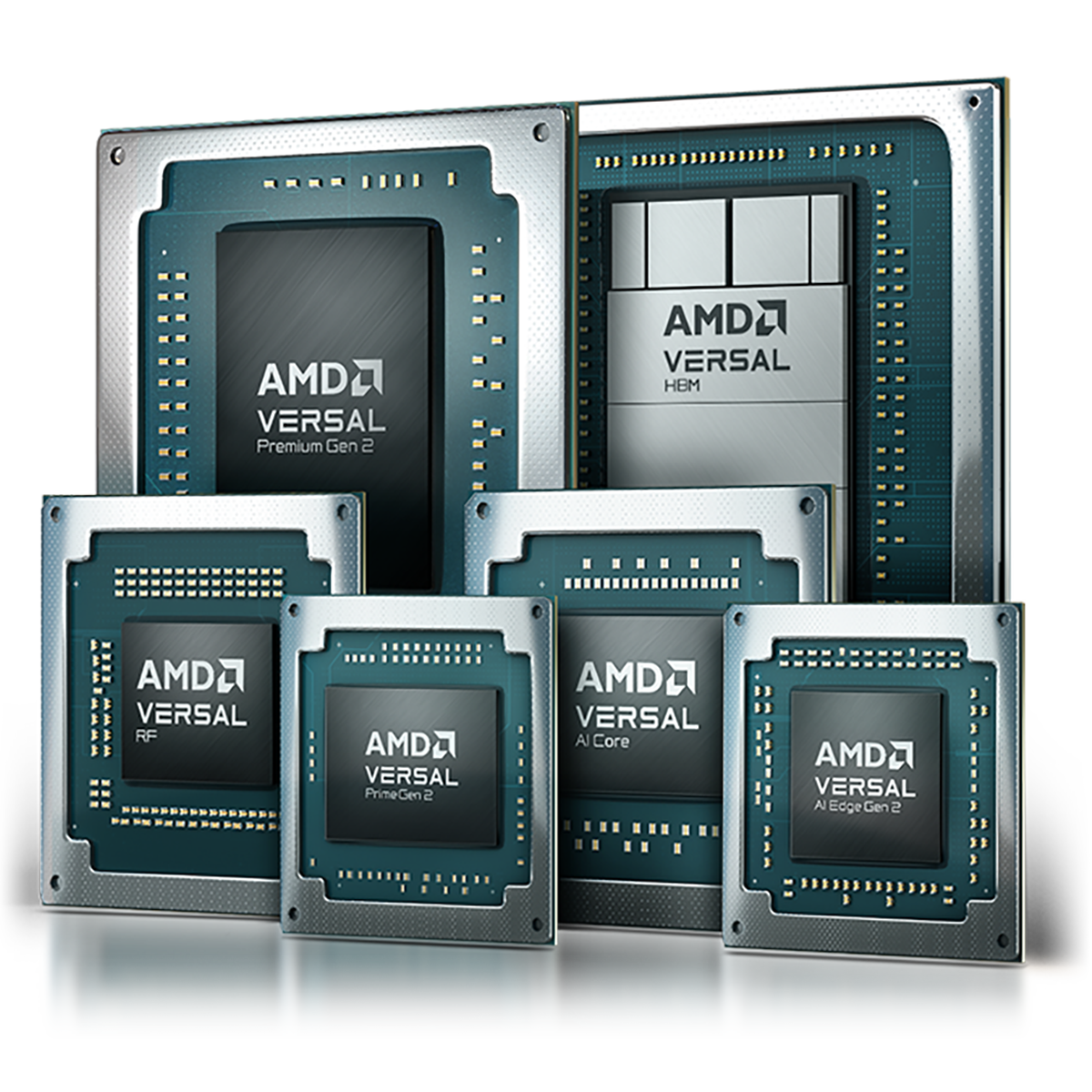

適合任何應用的自適應 SoC

AMD Versal™ 自適應 SoC 整合的功能遠超越傳統處理器、顯示卡和現場可程式化閘陣列 (Field-Programmable Gate Array, FPGA),實現針對特定領域的自適應架構,達到加速整個應用的效果。

無與倫比的效能與能效

此白皮書針對從邊緣及雲端到有線網路和 5G/6G 無線基礎架構等眾多市場,提供 Versal 自適應 SoC 的系統層級功能分析。

瞭解 Versal 架構如何為 AI 推論、Massive MIMO、網路加速、儲存裝置及多 Tb SmartPHY 等終端應用,提供超越競爭對手 10 nm FPGA 架構的世界級每瓦效能,且這一切均有可透過公開工具驗證的資料佐證。

AMD Versal 自適應 SoC 奠基於經實證的 FPGA 設計方法,成就系統設計的全新典範。Versal 架構是完全軟體可程式化、異構運算的架構,具備多種硬核 IP。

此產品組合中有通用的自適應 SoC,以及具備特殊功能的器件,例如用於 DSP 和機器學習工作負載的 AI 引擎、整合式 RF-ADC/RF-DAC、擴充 DSP 硬核 IP 或高頻寬記憶體。

內建的晶片功能搭配簡化的設計流程,以及 Vivado™ 工具的最新增強功能,使自動化和使用者控制都能實現突破性的每瓦系統效能。

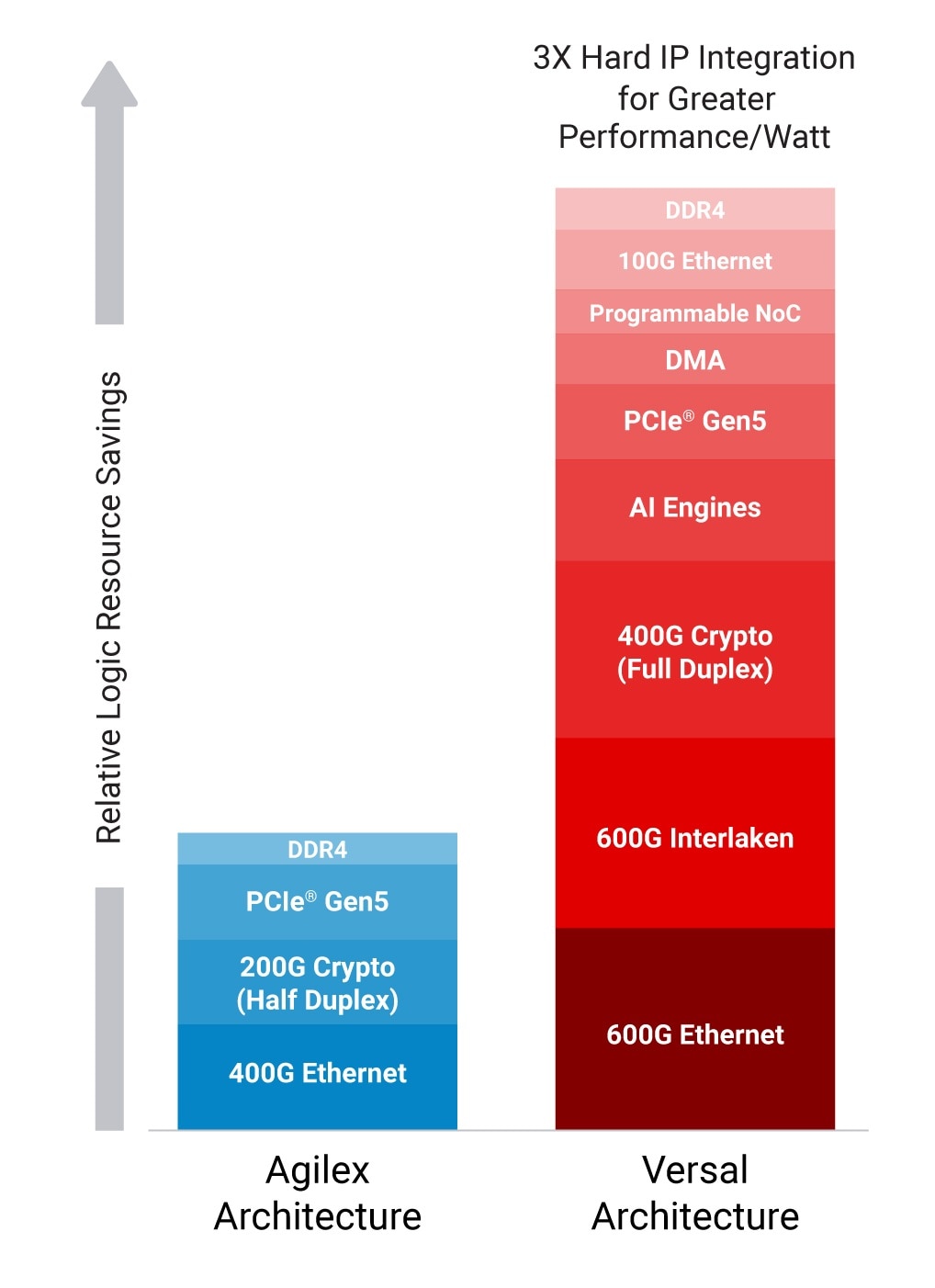

Versal 自適應 SoC 具有比競爭對手的 10 nm FPGA 多 3 倍的硬核 IP,並提供適用於所有裝置的共通基礎架構,例如可程式化 NoC,以實現程式設計便利性和程式碼可攜性,以及為多種市場提供特定領域的硬核 IP。

在可程式化邏輯與硬核 IP 之間取得平衡,於雲端、網路與邊緣的先進應用提供領先的每瓦效能,同時保留硬體彈性,因應不斷變化的需求與市場動態。

見證白皮書 WP539 中引用的 AMD Versal 對比競爭對手 FPGA 的基準測試結果

*註冊要求需符合相關條件

加入 Versal 產品組合通知清單,搶先收到最新消息。