选择 AMD 开发基于 FPGA 的原型设计系统的优势

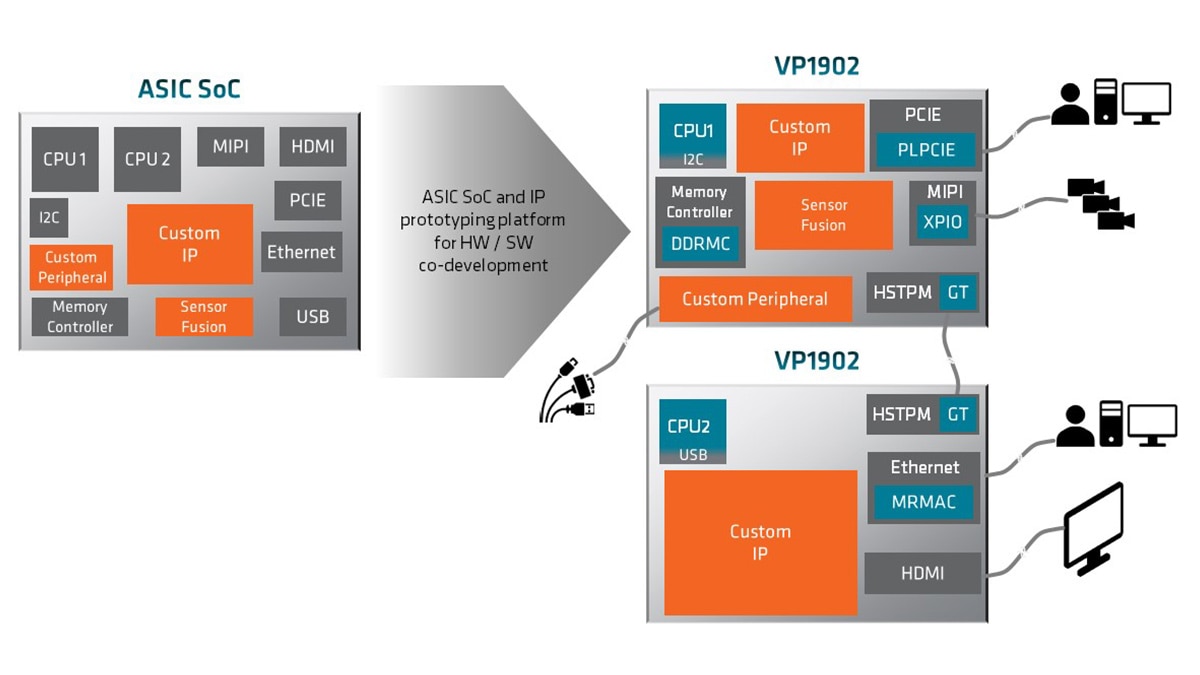

基于 FPGA 的原型设计是指在一个或多个自适应 SoC 或 FPGA 上对系统的部分或全部进行调试、验证和确认的过程。FPGA 辅助原型设计可在物理部件生产出来之前实现软硬件协同验证,从而缩短上市时间。

AMD 打造超大容量的自适应 SoC 和 FPGA1,支持更高 I/O、更低收发器时延,可充分提升系统性能。

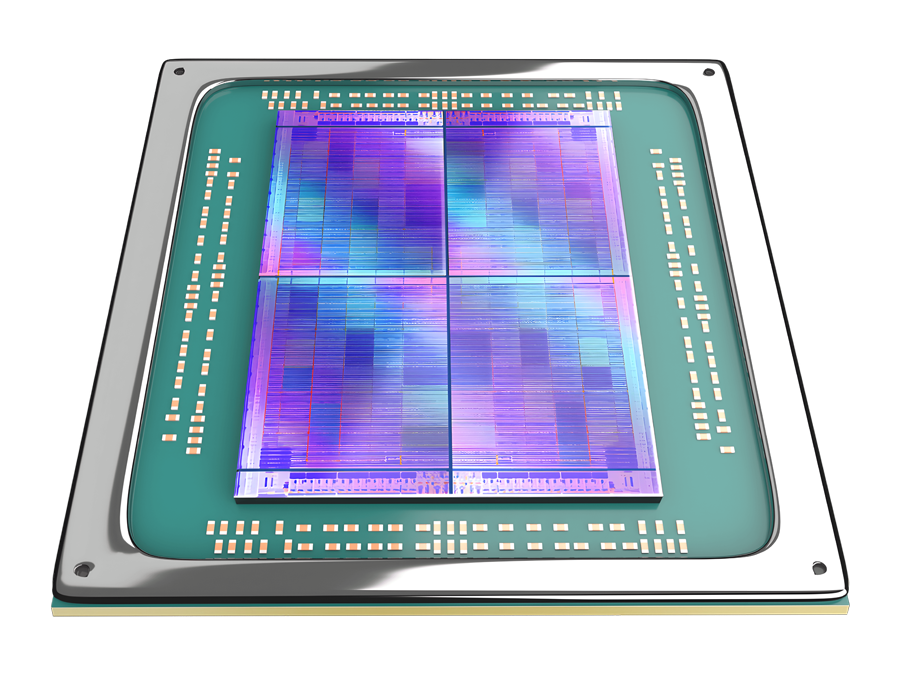

超大逻辑容量自适应 SoC1

- 不仅可减少区块数量,而且还可简化电路板布局

- 使平台容量提升到 2 倍2

- 使系统性能提升到 2 倍3

AMD Vivado™ ML 实现工具

- 减少编译时间

- 优化 QoR

- 堪比 ASIC 的时钟性能有效地映射复杂的 ASIC 和 SoC 时钟树

高带宽、低时延的 I/O 与收发器

- 自适应 SoC 之间的高效管脚复用

- 减少分区间的时延,提升系统性能

- 通过高速收发器管脚复用 IP 实现行业支持

完全可见的调试解决方案

- 可重入调试探针修改助力实现快速调试

- 支持基于配置的回读、写回及状态捕获

- 通过 PCIe® 进行高速调试

- 深度存储 ILA,可将捕获数据分载至外部存储器

产品系列

AMD Versal™ Premium VP1902 器件:超大自适应 SoC4

AMD Versal™ Premium VP1902 自适应 SoC 是创新采用片上标量处理子系统的仿真级器件,可为软硬件固件开发及系统初始化提供各种控制和激励生成使用模式。

与 Virtex™ UltraScale+™ VU19P 器件相比,VP1902 器件将器件容量2 提升一倍,以适应更大的 IP 及设计子系统。片上 A72 Arm® 处理器可为软硬件协同开发实现各种原型设计使用案例。我们的 XPIO 和 MIPI D-PHY 可实现各种高速外设激励。所有这些融合打造的出色解决方案可充分满足先进 ASIC、 IP 及 SoC 开发的原型设计需求。

精选 AMD 自适应计算合作伙伴

支持和资源

联系销售人员

我们的销售团队将根据您的具体需求帮助您做出明智的技术决策。

附注

- 基于 AMD 2023 年 5 月的内部分析。(VER-009)

- 基于 AMD 在 2023 年 5 月进行的内部分析,比较 Versal Premium VP1902 器件与 Virtex UltraScale+ VU19P 器件的系统逻辑单元数量。(VER-001)

- 基于 AMD 2023 年 5 月的内部系统时钟性能分析,通过一系列不同尺寸的设计方案对 Versal Premium VP1902 器件和 Virtex UltraScale+ VU19P 器件进行了比较。(VER-006)

-

- 基于 AMD 实验室测试,使用 A6865 封装来仿真 AMD Versal Premium VP1902 器件的 XPIO 数据速率性能,并与 AMD Virtex UltraScale+ VU19P FPGA 的公布数据速率进行了对比。实际结果会有所不同。(VER-003)

- 基于 AMD 实验室在 2023 年 5 月对 Versal Premium VP1902 器件 B6865 封装与 Virtex UltraScale+ VU19P 器件 B3824 封装的总收发器带宽的计算,假设 GTY/GTYP 以 32G 运行、GTM 以 56G 运行。(VER-005)

附注

- 基于 AMD 2023 年 5 月的内部分析。(VER-009)

- 基于 AMD 在 2023 年 5 月进行的内部分析,比较 Versal Premium VP1902 器件与 Virtex UltraScale+ VU19P 器件的系统逻辑单元数量。(VER-001)

- 基于 AMD 2023 年 5 月的内部系统时钟性能分析,通过一系列不同尺寸的设计方案对 Versal Premium VP1902 器件和 Virtex UltraScale+ VU19P 器件进行了比较。(VER-006)

-

- 基于 AMD 实验室测试,使用 A6865 封装来仿真 AMD Versal Premium VP1902 器件的 XPIO 数据速率性能,并与 AMD Virtex UltraScale+ VU19P FPGA 的公布数据速率进行了对比。实际结果会有所不同。(VER-003)

- 基于 AMD 实验室在 2023 年 5 月对 Versal Premium VP1902 器件 B6865 封装与 Virtex UltraScale+ VU19P 器件 B3824 封装的总收发器带宽的计算,假设 GTY/GTYP 以 32G 运行、GTM 以 56G 运行。(VER-005)