FPGA ベースのプロトタイピング システム開発における AMD テクノロジの主要な利点

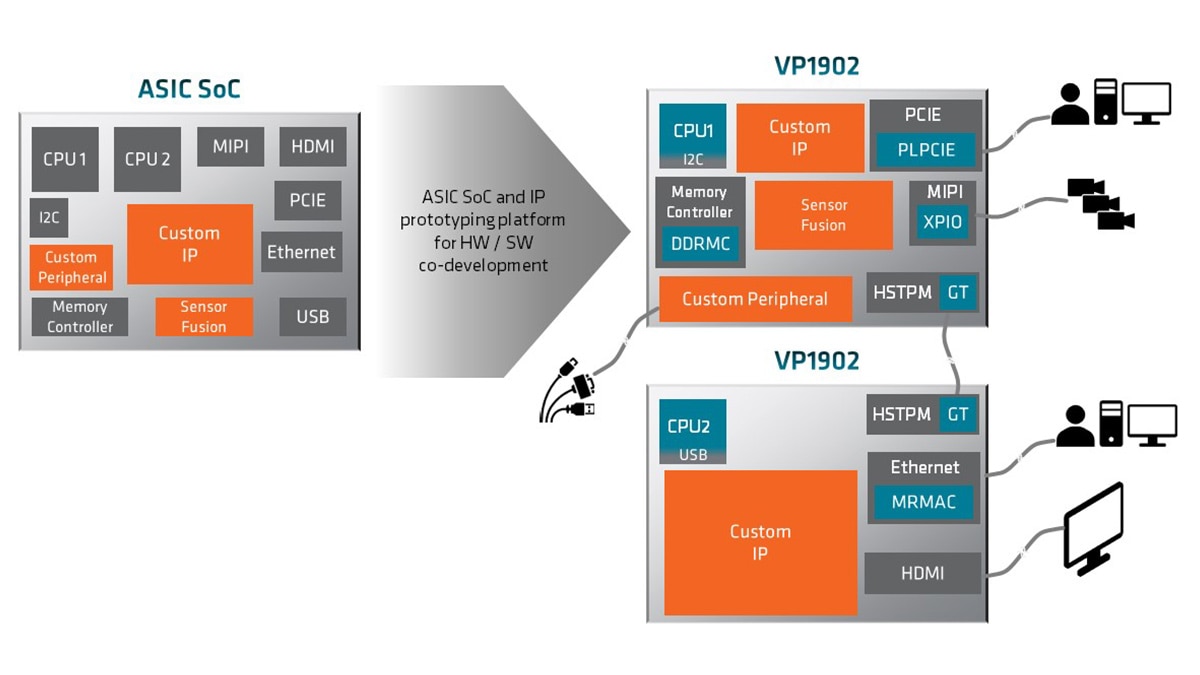

FPGA ベースのプロトタイピングは、1 つまたは複数のアダプティブ SoC または FPGA を搭載したシステム全体または一部をデバッグおよび検証するプロセスです。FPGA 機能を活用したプロトタイピングでは、物理的なデバイスが完成する前にハードウェアとソフトウェアの協調検証を行うことで開発期間を短縮できます。

AMD は、システムの性能を最大限に引き出すために I/O とトランシーバーのレイテンシを改善した業界最大容量のアダプティブ SoC および FPGA1 を提供しています。

世界最大容量を誇るアダプティブ SoC1

- デザインのパーティション数を削減し、ボード レイアウトを簡素化

- 2 倍の容量を備えたプラットフォームを実現2

- 2 倍のシステム性能を実現3

AMD Vivado™ ML インプリメンテーション ツール

- コンパイル時間の短縮

- QoR の向上

- ASIC のようなクロッキングにより、複雑な ASIC および SoC のクロック ツリーを効率的にマップ

高帯域幅かつ低レイテンシの I/O およびトランシーバー

- アダプティブ SoC 間で効率的にピンを多重化

- パーティション間のレイテンシ削減によるシステム性能向上

- AMD の HSTPM (High-Speed Transceiver Pin Multiplexing) IP の利用による業界サポート

可視性が高いデバッグ ソリューション

- デバッグを効率化する再入可能なデバッグ プローブ機能

- 設定に基づくリードバック、ライトバック、ステート キャプチャをサポート

- PCIe® を利用する高速デバッグ

- ディープ ストレージ ILA でキャプチャしたデータを外部メモリに転送

製品ポートフォリオ

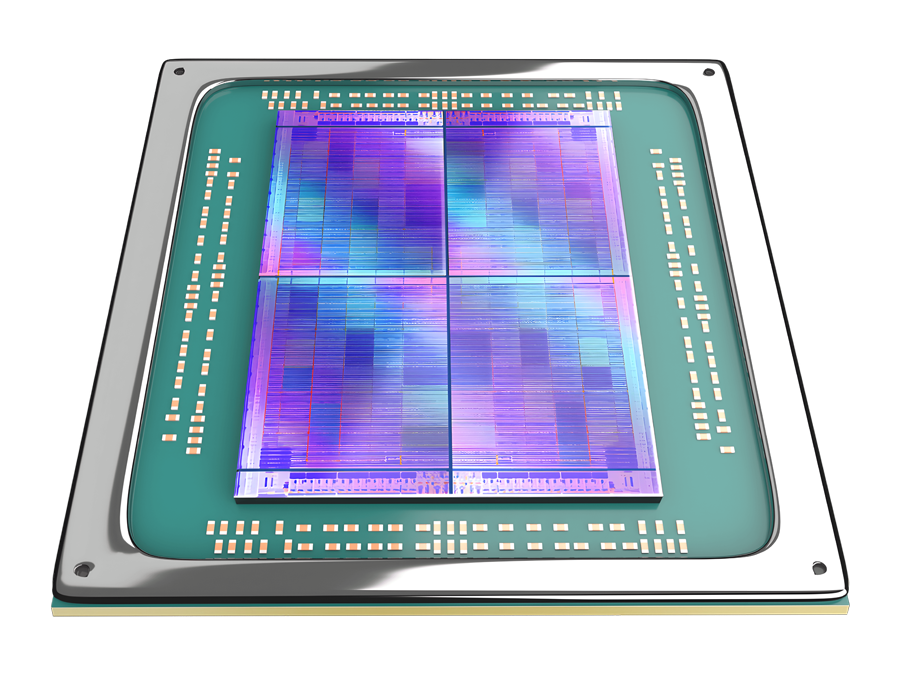

AMD Versal™ プレミアム VP1902 デバイス: 世界最大容量のアダプティブ SoC4

AMD の Versal™ プレミアム VP1902は、オンチップにスカラー プロセッシング サブシステムを搭載した初めてのエミュレーション クラス デバイスであり、SW/HW ファームウェアの開発やシステムの立ち上げにおいて多様な制御やスティミュラスの生成を可能にするモードを提供します。

VP1902 デバイスは、Virtex™ UltraScale+™ VU19P デバイスと比較してデバイス容量が 2 倍に拡大しており2、より大きな IP と設計サブシステムに対応。オンチップの A72 Arm® プロセッサは、ソフトウェアとハードウェアの協調開発においてさまざまなプロトタイピングのニーズに対応できます。AMD の XPIO および MIPI D-PHY を利用することで、高速動作するペリフェラルに合わせてスティミュラスを生成できます。これらのシリコン機能は、最先端の ASIC、IP、および SoC 開発におけるさまざまなプロトタイピング要求に応えることができる最適なソリューションを提供します。

主な AMD アダプティブ コンピューティング パートナー

開発を開始

AMD Versal プレミアムを使用してプロトタイプを作成

AMD Versal™ プレミアム VP1902 デバイス: 世界最大容量のアダプティブ SoC

- AMD Virtex™ UltraScale+™ VU19P デバイスと比較してロジック集積度 2 倍2

- I/O の総帯域幅は 2 倍5、トランシーバー帯域幅は 2.3 倍6

- I/O レイテンシの短縮と 2x2 SLR アレイによるシステム性能の向上

AMD VivadoTM ML Design Suite

AMD の Vivado™ ML Design Suite は、コンパイル時間と QoR を改善する新しいインプリメンテーション機能を備えた最先端の開発環境を提供します。

サポートとリソース

営業に問い合わせ

AMD のセールス チームがお客様のニーズに合ったベストな技術的判断ができるようお手伝いいたします。

脚注

- AMD の社内解析に基づく (2023 年 5 月実施)。(VER-009)

- AMD 社内解析に基づく (2023 年 5 月実施) - Versal プレミアム VP1902 デバイスと Virtex UltraScale+ VU19P デバイスのシステム ロジック セル数を比較。(VER-001)

- AMD 社内で実施したシステム クロック性能解析に基づく (2023 年 5 月実施) - さまざまなデザイン サイズと配線で Versal プレミアム VP1902 デバイスと Virtex UltraScale+ VU19P デバイスの性能を比較。(VER-006)

- AMD の社内解析に基づく (2023 年 5 月実施) - 6 入力 LUT を使用して、Versal プレミアム VP1902 デバイスとインテル Stratix 10 GX 10M FPGA を比較。(VER-002)

- AMD のラボ テストに基づく - A6865 パッケージを使用して、AMD Versal プレミアム VP1902 デバイスの XPIO データレート パフォーマンスをシミュレーションし、AMD Virtex UltraScale+ VU19P FPGA の公表されているデータレートと比較。実際の結果は異なる場合があります。(VER-003)

- AMD のラボ解析結果に基づく (2023 年 5 月実施) - GTY/GTYP が 32G で動作し、GTM が 56G で動作する場合を想定し、Versal プレミアム VP1902 デバイス B6865 パッケージと Virtex UltraScale+ VU19P デバイス B3824 パッケージのトランシーバーの総帯域幅を比較。(VER-005)

- AMD の社内解析に基づく (2023 年 5 月実施)。(VER-009)

- AMD 社内解析に基づく (2023 年 5 月実施) - Versal プレミアム VP1902 デバイスと Virtex UltraScale+ VU19P デバイスのシステム ロジック セル数を比較。(VER-001)

- AMD 社内で実施したシステム クロック性能解析に基づく (2023 年 5 月実施) - さまざまなデザイン サイズと配線で Versal プレミアム VP1902 デバイスと Virtex UltraScale+ VU19P デバイスの性能を比較。(VER-006)

- AMD の社内解析に基づく (2023 年 5 月実施) - 6 入力 LUT を使用して、Versal プレミアム VP1902 デバイスとインテル Stratix 10 GX 10M FPGA を比較。(VER-002)

- AMD のラボ テストに基づく - A6865 パッケージを使用して、AMD Versal プレミアム VP1902 デバイスの XPIO データレート パフォーマンスをシミュレーションし、AMD Virtex UltraScale+ VU19P FPGA の公表されているデータレートと比較。実際の結果は異なる場合があります。(VER-003)

- AMD のラボ解析結果に基づく (2023 年 5 月実施) - GTY/GTYP が 32G で動作し、GTM が 56G で動作する場合を想定し、Versal プレミアム VP1902 デバイス B6865 パッケージと Virtex UltraScale+ VU19P デバイス B3824 パッケージのトランシーバーの総帯域幅を比較。(VER-005)