Soluciones de SoC adaptable AMD Versal

Los sistemas que utilizan las implementaciones de la especificación PCI Express® son de acceso generalizado en centros de datos, comunicaciones y aplicaciones integradas. Las múltiples opciones de conectividad disponibles en la arquitectura Versal™ respaldan directamente las necesidades de los usuarios de centrarse en su competencia principal al tiempo que aprovechan las interfaces avanzadas basadas en estándares. Los bloques integrados para PCI Express en la arquitectura Versal ofrecen niveles de rendimiento superiores con facilidad de uso y eficiencia frente a las soluciones de IP totalmente blanda. La arquitectura Versal integra cinco tipos de bloques integrados para PCI Express:

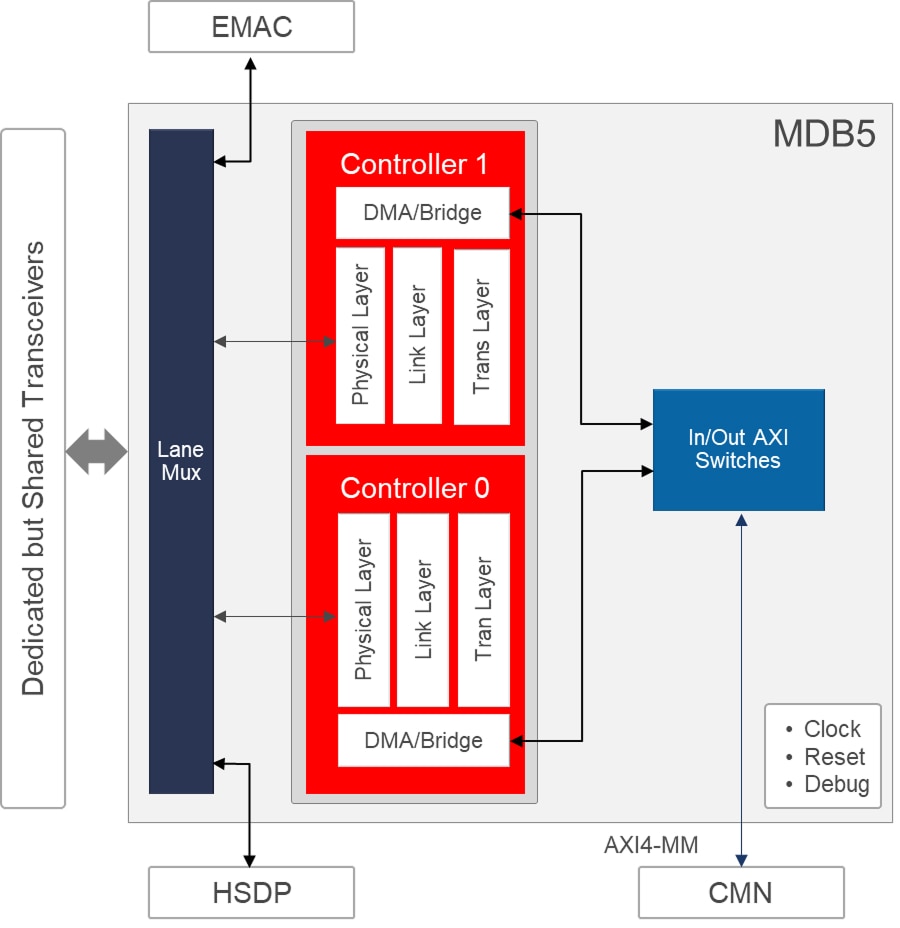

- MDB5: bloque integrado para PCI Express Rev. 5.0 con DMA/puente

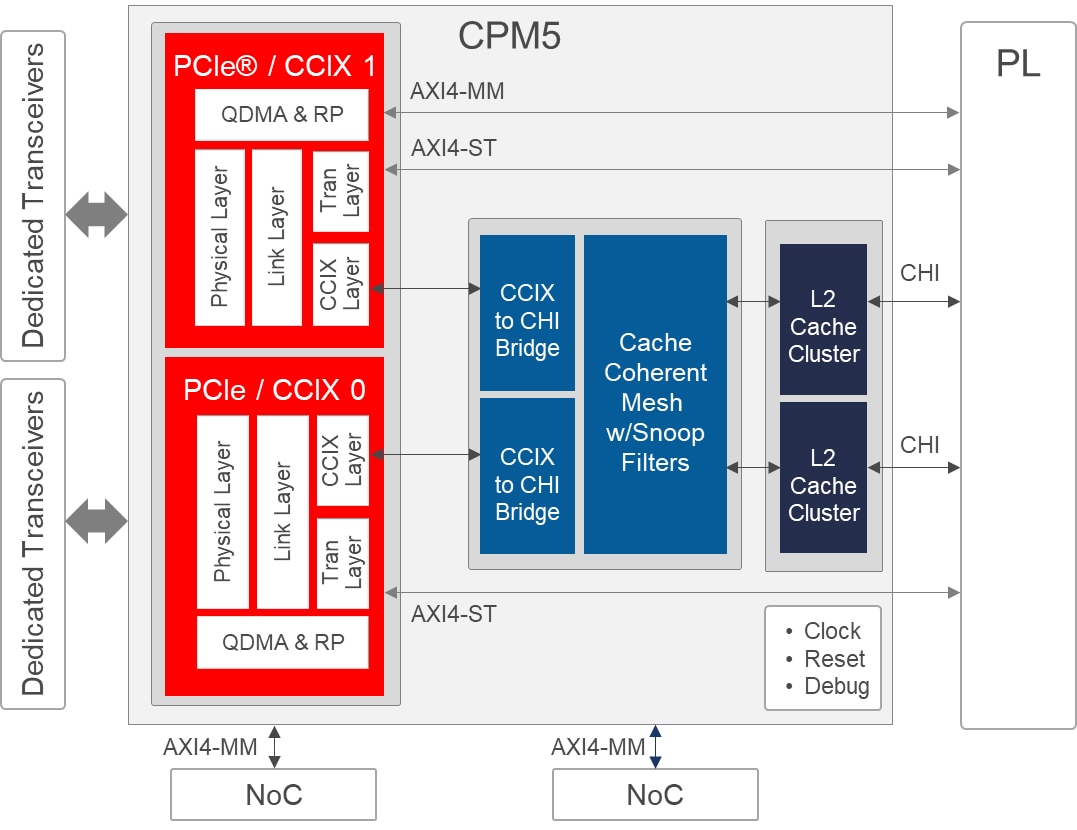

- CPM5: bloque integrado para PCI Express Rev. 5.0 con DMA/puente

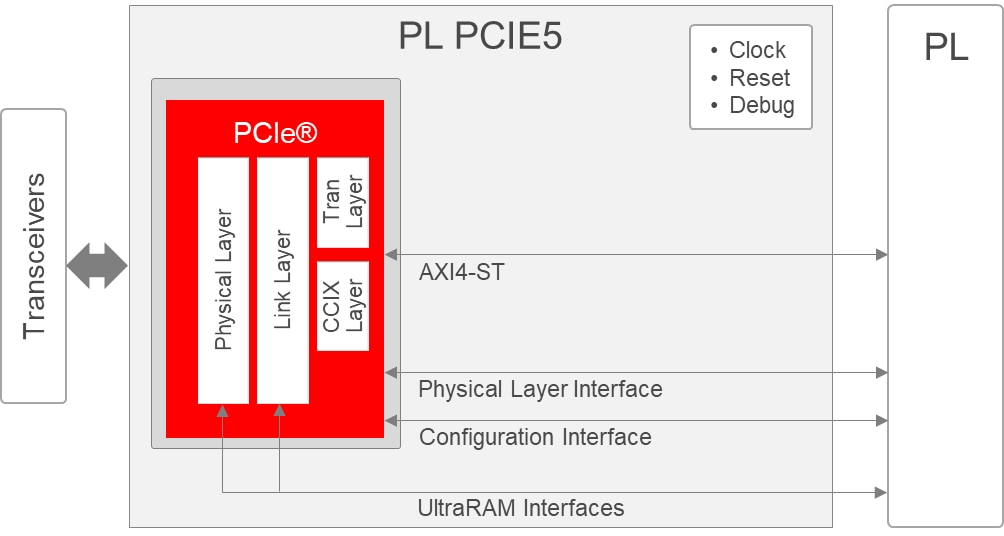

- PL PCIE5: bloque integrado para PCI Express Rev. 5.0

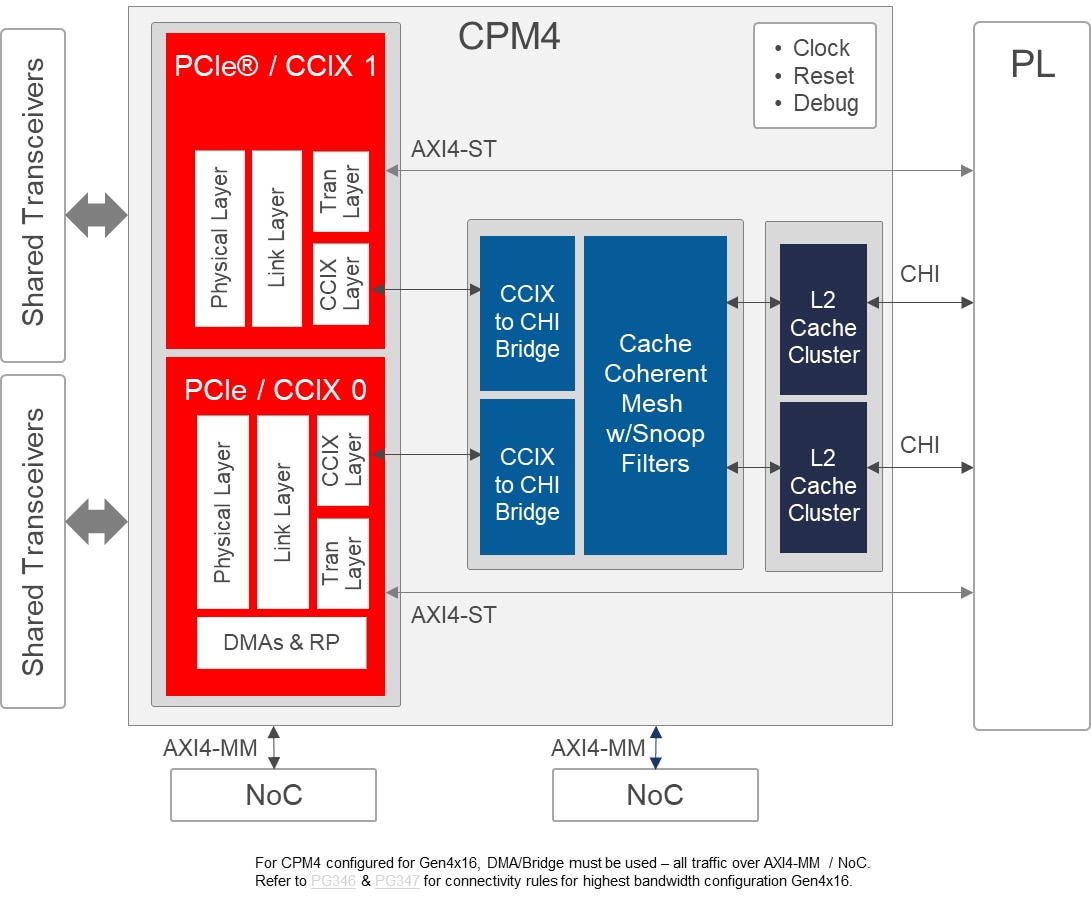

- CPM4: bloque integrado para PCI Express Rev. 4.0 con DMA/puente

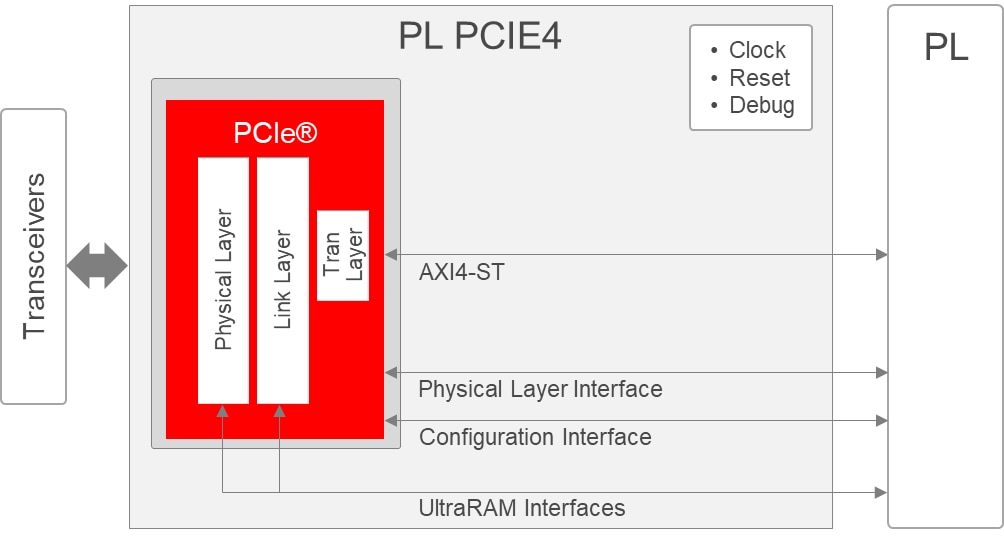

- PL PCIE4: bloque integrado para PCI Express Rev. 4.0

MDB5, CPM5, PL PCIE5, CPM4 y PL PCIE4, junto con los transceptores GTYP y GTY disponibles, permiten el funcionamiento de la interfaz a velocidades de datos definidas por especificaciones. Estas varían desde 2,5 GT/s por carril con un carril (Gen1x1) hasta sus configuraciones de enlace máximo nominal, con algunos bloques integrados que alcanzan los 32 GT/s por carril con 8 carriles (Gen5x8) y 16 GT/s por carril con 16 carriles (Gen4x16).

En la siguiente tabla, se brinda un resumen de las características clave de los bloques integrados para PCI Express en la arquitectura Versal. Consulta la Ficha técnica de arquitectura y productos Versal: Descripción general (DS950) para obtener información adicional sobre recursos y capacidades disponibles en función de combinaciones de nivel de velocidad/voltaje, paquete y dispositivos que pueden pedirse.

|

Bloques integrados de arquitectura Versal para PCI Express |

|---|

MDB5

Ver diagrama

|

CPM5

Ver diagrama

|

PL PCIE5

Ver diagrama

|

CPM4

Ver diagrama

|

PL PCIE4

Ver diagrama

|

|---|

Especificaciones

asociadas |

PCIe Rev. 5.0 |

PCIe Rev. 5.0 |

PCIe Rev. 5.0

|

PCIe Rev. 4.0

|

PCIe Rev. 4.0 |

|---|

PCIe máx.

Configuraciones de enlaces |

Gen5x4

Dos unidades Gen5x2

Gen5x2 |

2 unidades Gen5x8

Gen4x16

2 unidades Gen4x8 |

Gen5x4

Gen4x8

Gen3x16 |

Gen4x16

2 unidades Gen4x8 |

Gen4x8

Gen3x16 |

|---|

Compatibilidad de tipo

de puerto PCIe |

PE, RP |

PE, RP,

Conmutador |

PE, RP,

Conmutador |

PE, RP,

Conmutador |

PE, RP,

Conmutador |

|---|

Funciones

PCIe clave |

SR-IOV

8PF/64VF |

SR-IOV

16PF/4KVF |

SR-IOV

8PF/4KVF |

SR-IOV

4PF/252VF |

SR-IOV

4PF/252VF |

|---|

| DMA/puente integrado |

Se necesitan dos puentes

2 DMA opcionales |

2 opcionales

QDMA/puente |

- |

1 opcional

QDMA/puente o XDMA/puente |

- |

|---|

MDB5, CPM5, PL PCIE5, CPM4 y PL PCIE4 se pueden utilizar en configuraciones de enlace reducidas para optimizar los diseños de productos en función del costo, admitir nuevos formatos, aliviar la complejidad de la placa y reducir los presupuestos de energía. Además, las configuraciones de enlace reducidas pueden admitir una menor utilización de recursos lógicos programables, dependiendo de la naturaleza de cualquier solución de IP blanda utilizada para expandir las capacidades a nivel de aplicación de estos bloques integrados. CPM5, PL PCIE5, CPM4 y PL PCIE4 se pueden configurar como tipos de puertos de EP (endpoint, punto de conexión), RP (Root Port, puerto raíz) y conmutador. Se puede configurar MDB5 como tipos de puertos de punto de conexión (EP) y puerto raíz (RP).

Los subsistemas DMA/puente preverificados de alto rendimiento para los bloques integrados de PCI Express en la arquitectura Versal permiten que los usuarios enfoquen la inversión de diseño en las áreas de mayor valor. Los subsistemas DMA/puente incluyen las siguientes opciones:

- MDB5 contiene dos controladores para PCI Express e integra dos instancias de un subsistema DMA/puente. El uso del DMA integrado es opcional, y cada instancia es personalizable de forma independiente. Los subsistemas DMA proporcionan un acoplamiento estrecho a los procesadores integrados y AXI Interconnect. Los subsistemas también incluyen funcionalidad de puente. Los datos se pueden mover con técnicas de asignación en memoria, incluida la NoC (network on chip, red en chip) programable.

- CPM5 contiene dos controladores para PCI Express y también integra dos instancias de un subsistema QDMA/puente. El uso del DMA integrado es opcional, y cada instancia es personalizable de forma independiente. Los subsistemas QDMA proporcionan un DMA escalable basado en colas para mover enormes volúmenes de datos con baja latencia, además de compatibilidad con múltiples funciones físicas y virtuales que normalmente requieren los productos de clase empresarial. Los datos se pueden mover con técnicas de asignación en memoria, incluida la red en chip (NoC) programable, o con técnicas de streaming, a la lógica programable del SoC adaptable Versal. Los subsistemas también incluyen la funcionalidad de puente a AXI Interconnect.

- CPM4 contiene dos controladores para PCI Express y también integra una instancia de un subsistema QDMA/XDMA/puente. El uso del DMA integrado es opcional y, cuando se utiliza, se puede configurar como un subsistema QDMA como el del CPM5 o como un subsistema XDMA. Los datos se pueden mover con técnicas de asignación en memoria, incluida la NoC programable, o con técnicas de streaming, a la lógica programable del SoC adaptable Versal. El subsistema también incluye la funcionalidad de puente a AXI Interconnect.

- PL PCIE5 y PL PCIE4 son controladores individuales para PCI Express y son compatibles con implementaciones de IP blanda de subsistemas DMA/puente disponibles de AMD a través del catálogo de IP de Vivado™ Design Suite; además, hay soluciones adicionales disponibles de los socios de AMD Embedded Computing.

Para la mayoría de los usuarios, los subsistemas DMA/puente disponibles pueden proporcionar una infraestructura que ahorra tiempo, lo que permite un movimiento de datos inmediato de alto rendimiento. Consulta la Guía de producto de modo DMA y puente CPM de SoC adaptable Versal para PCI Express (PG347), la Guía de producto de Versal Adaptive SoC DMA and Bridge Subsystem for PCI Express (PG344), y la solución puente AXI con DMA para PCIe de los socios de AMD Embedded Computing Smartlogic GmbH.

Para los usuarios que quieran adjuntar su propio subsistema DMA/puente, a fin de preservar su inversión en software de controlador y aplicación o para personalizar u optimizar la funcionalidad con un conocimiento detallado de la aplicación final, hay opciones disponibles para diseñar directamente a los controladores para PCI Express en los bloques CPM5, PL PCIE5, CPM4 y PL PCIE4. Consulta la Guía de producto de modo CPM de SoC adaptable Versal para PCI Express (PG346) y la Guía de producto de bloque integrado de SoC adaptable Versal para PCI Express de IP LogiCORE (PG343). Para obtener la máxima libertad de implementar soluciones totalmente personalizadas, AMD ofrece un núcleo de IP blanda PHY para PCI Express, lo que permite a los diseñadores conectar sus propios controladores para PCI Express a los transceptores GTYP y GTY disponibles. Los socios de AMD Embedded Computing, incluido Fidus Systems, Inc., prestan servicios de desarrollo y consultoría con propuestas de valor únicas para diferenciar y acelerar el diseño con los SoC adaptables Versal.