Solutions de SoC adaptatif AMD Versal

Les systèmes qui mettent en œuvre la spécification PCI Express® sont omniprésents dans les centres de données, les communications et les applications intégrées. Les nombreuses options de connectivité disponibles dans l'architecture Versal™ répondent directement aux besoins des utilisateurs qui souhaitent se concentrer sur leur cœur de métier tout en tirant parti d'interfaces avancées basées sur des normes. Les blocs intégrés pour PCI Express dans l'architecture Versal offrent des niveaux de performance supérieurs, avec une facilité d'utilisation et une efficacité supérieures aux solutions entièrement soft IP. L'architecture Versal comprend cinq types de blocs intégrés pour PCI Express :

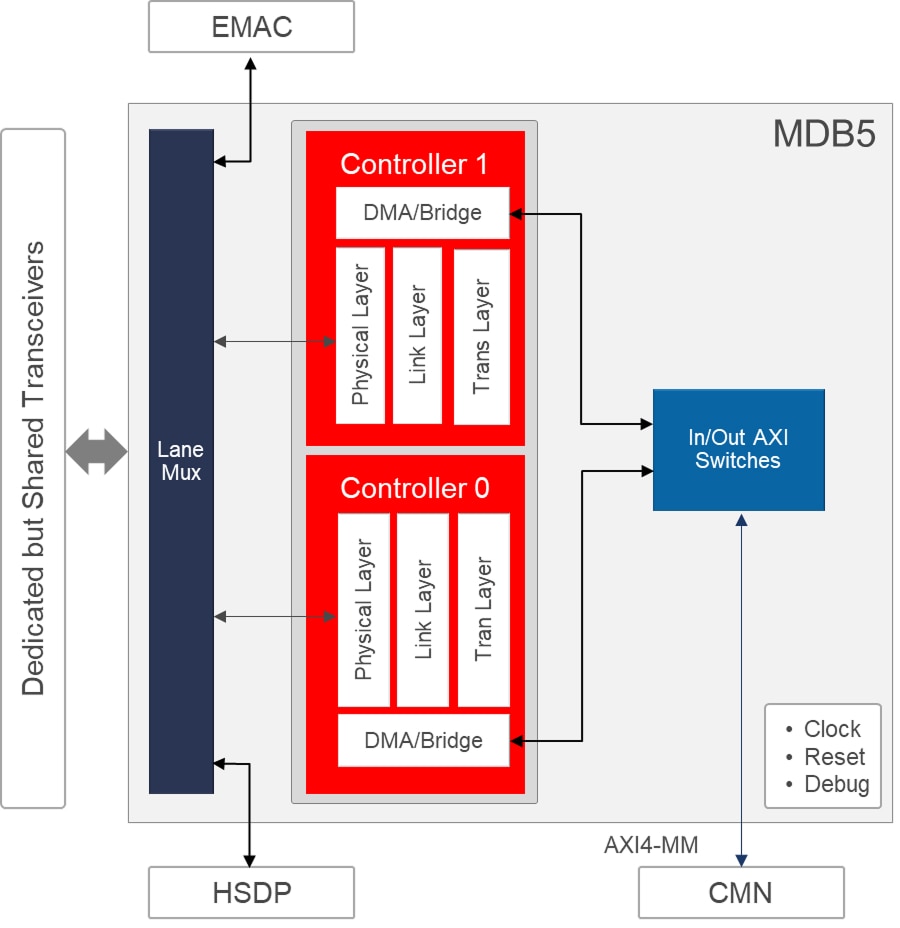

- MDB5 : bloc intégré pour PCI Express Rév. 5.0 avec DMA/pont

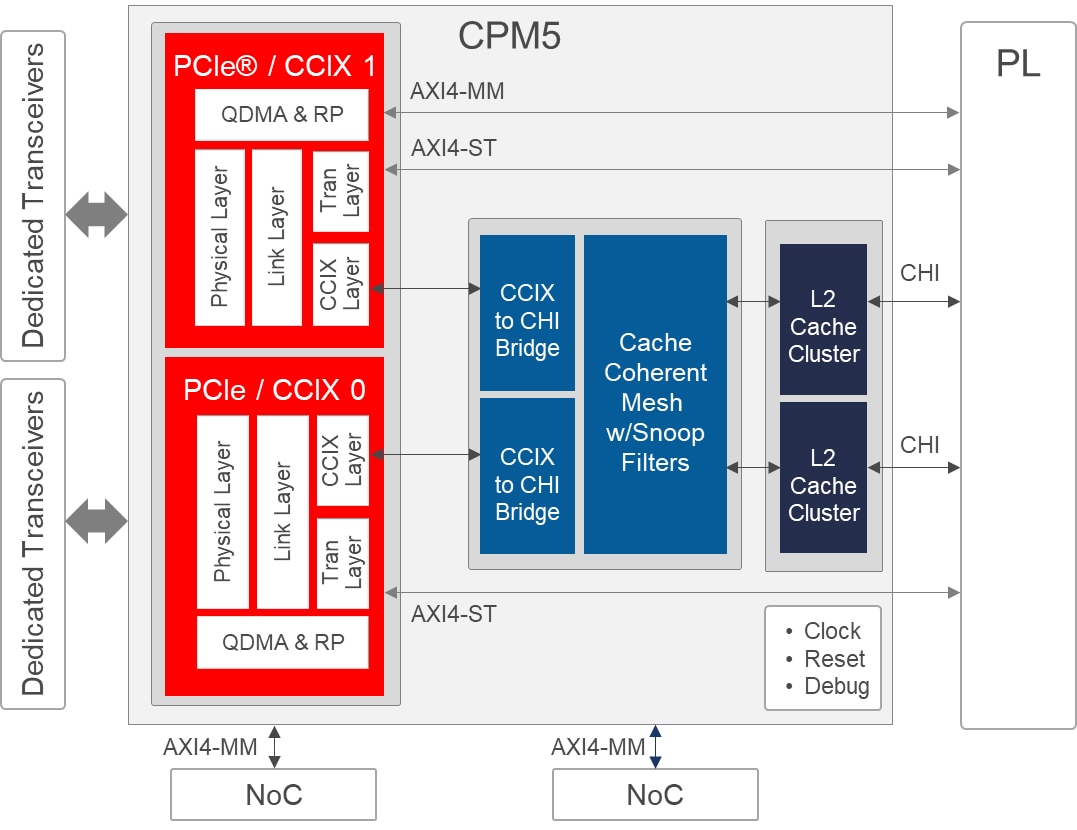

- CPM5 : bloc intégré pour PCI Express Rev. 5.0 avec DMA/pont.

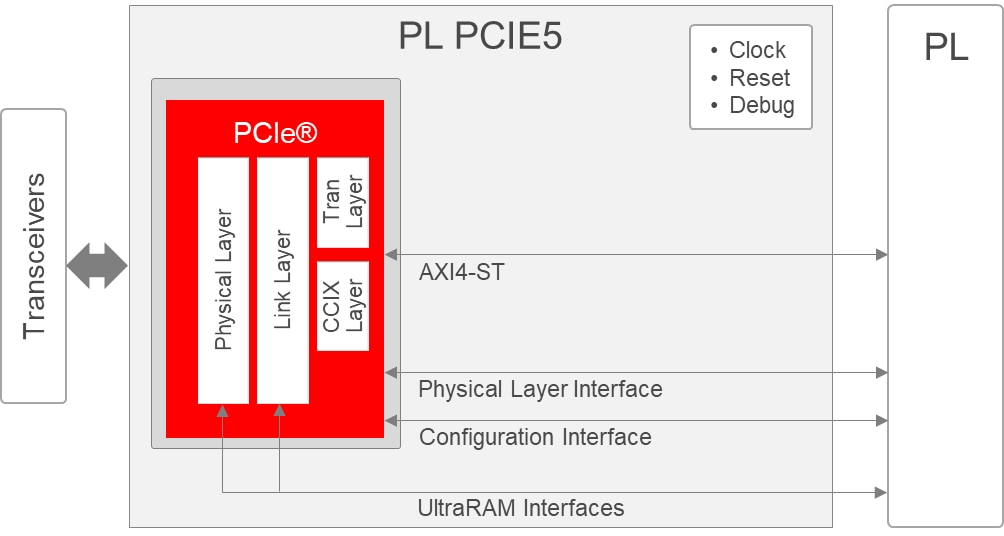

- PL PCIE5 : bloc intégré pour PCI Express Rév. 5.0

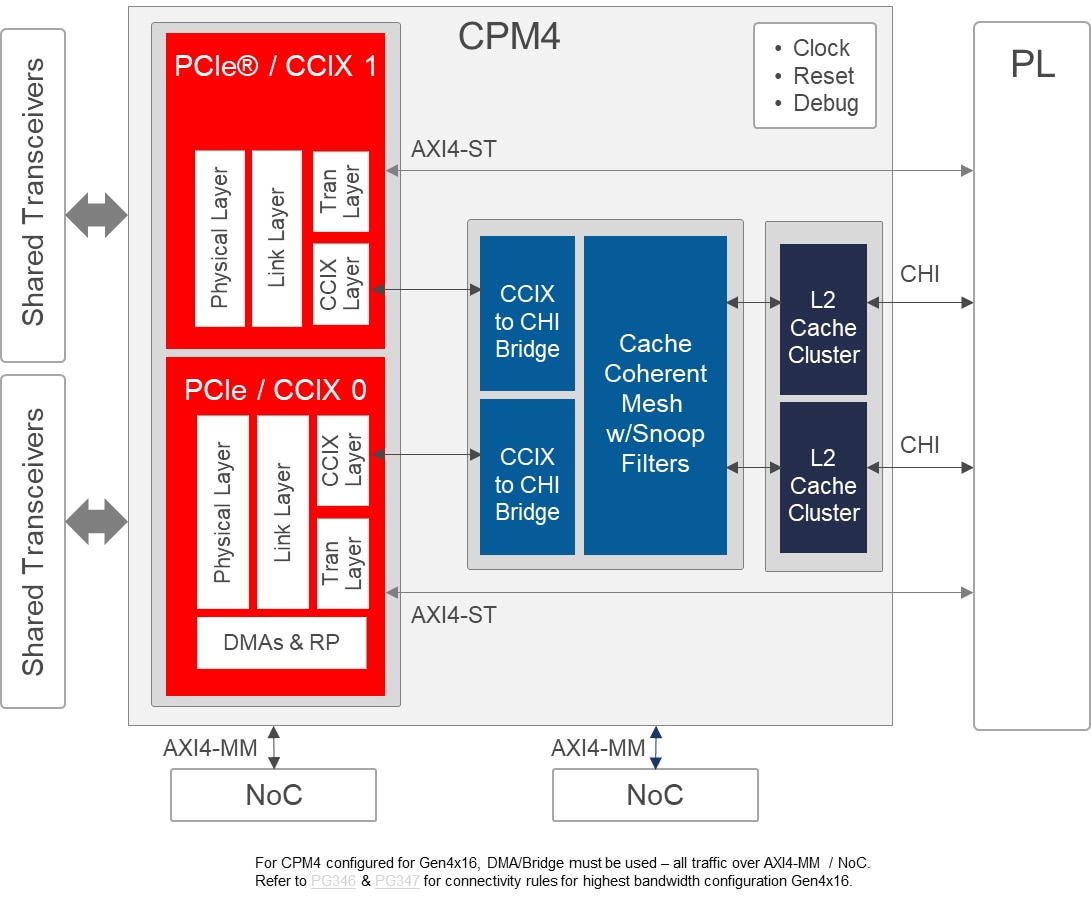

- CPM4 : bloc intégré pour PCI Express Rev. 4.0 avec DMA/pont.

- PL PCIE4 : bloc intégré pour PCI Express Rév. 4.0

MDB5, CPM5, PL PCIE5, CPM4 ET PL PCIE4, associés aux transceivers GTYP et GTY disponibles, permettent un fonctionnement de l'interface à des débits binaires définis par les spécifications. Celles-ci vont de 2,5 GT/s par voie avec une voie (Gen1x1) jusqu'à leurs configurations de liaisons maximales nominales, certains blocs intégrés atteignant 32 GT/s par voie avec 8 voies (Gen5x8) et 16 GT/s par voie avec 16 voies (Gen4x16).

Le tableau ci-dessous résume les principales caractéristiques des blocs intégrés pour PCI Express dans l'architecture Versal. Reportez-vous à la Fiche technique du produit et de l'architecture Versal : Présentation (DS950) pour en savoir plus sur les ressources et capacités disponibles en fonction des combinaisons de composants, de packages et de niveaux de tension/vitesse.

|

Blocs intégrés de l'architecture Versal pour PCI Express |

|---|

MDB5

Afficher le schéma

|

CPM5

Afficher le schéma

|

PL PCIE5

Afficher le schéma

|

CPM4

Afficher le schéma

|

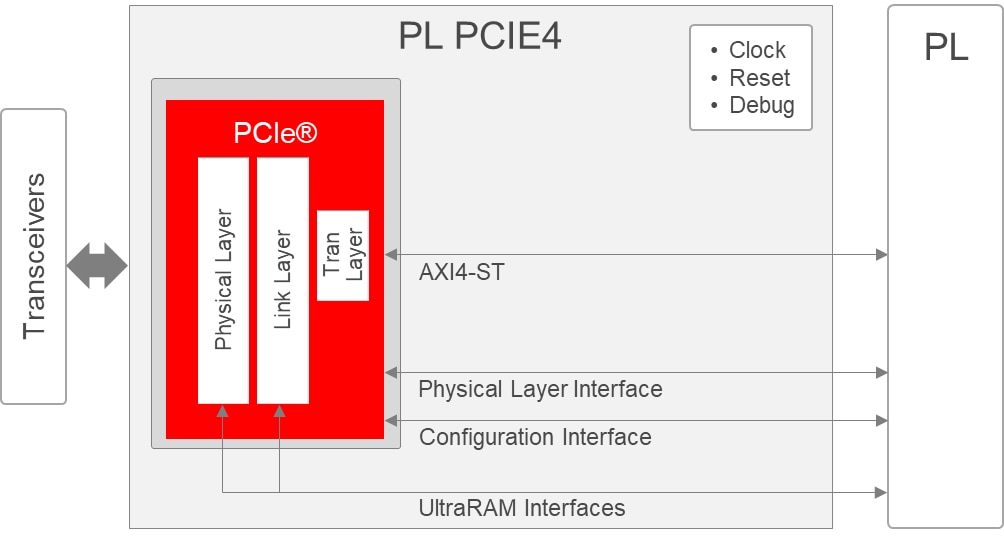

PL PCIE4

Afficher le schéma

|

|---|

Caractéristiques

associées |

PCIe Rév. 5.0 |

PCIe Rév. 5.0 |

PCIe Rév. 5.0

|

PCIe Rév. 4.0

|

PCIe Rév. 4.0 |

|---|

Configuration des liaisons

PCIe max. |

Gen5x4

2 x Gen5x2

Gen5x2 |

2 x Gen5x8

Gen4x16

2 x Gen4x8 |

Gen5x4

Gen4x8

Gen3x16 |

Gen4x16

2 x Gen4x8 |

Gen4x8

Gen3x16 |

|---|

Prise en charge du type

de port PCIe |

EP, RP |

EP, RP,

Commutateur |

EP, RP,

Commutateur |

EP, RP,

Commutateur |

EP, RP,

Commutateur |

|---|

Fonctionnalités

Fonctionnalités |

SR-IOV

8PF/64VF |

SR-IOV

16PF/4KVF |

SR-IOV

8PF/4KVF |

SR-IOV

4PF/252VF |

SR-IOV

4PF/252VF |

|---|

| DMA/pont intégré |

Deux ponts requis,

Deux DMA en option |

Deux

QDMA/ponts en option |

- |

Un

QDMA/pont ou XDMA/pont en option |

- |

|---|

MDB5, CPM5, PL PCIE5, CPM4 et PL PCIE4 peuvent être utilisés dans des configurations de liaison réduites pour optimiser la conception des produits en matière de coût, prendre en charge de nouveaux formats, réduire la complexité des cartes et diminuer les budgets énergétiques. De plus, les configurations de liaison réduites favorisent une utilisation moindre des ressources logiques programmables, selon la nature des solutions soft IP utilisées pour étendre les capacités applicatives de ces blocs intégrés. Les blocs CPM5, PL PCIE5, CPM4 et PL PCIE4 peuvent être configurés en tant que types de point de terminaison (Endpoint, EP), de port racine (Root Port, RP) et de port de commutation. Le bloc MDB5 peut être configuré en tant que type de port de point de terminaison (Endpoint, EP) ou de port racine (Root Port, RP).

Les sous-systèmes DMA/pont hautes performances pré-vérifiés pour les blocs intégrés PCI Express dans l'architecture Versal permettent aux utilisateurs de concentrer leurs investissements en matière de conception dans les domaines les plus avantageux. Les sous-système DMA/pont disponibles sont les suivants :

- Le bloc MDB5 contient deux contrôleurs PCI Express et intègre deux instances d'un sous-système DMA/pont. L'utilisation du DMA intégré est facultative et chaque instance est personnalisable indépendamment. Les sous-systèmes DMA assurent un couplage étroit avec les processeurs intégrés et l'interconnexion AXI. Les sous-systèmes incluent également une fonctionnalité de pont. Le déplacement des données s'effectue par des techniques de mappage mémoire, notamment le Network on Chip (NoC) programmable.

- CPM5 contient deux contrôleurs pour PCI Express et intègre également deux instances d'un sous-système QDMA/pont. L'utilisation du DMA intégré est facultative et chaque instance est personnalisable indépendamment. Les sous-systèmes QDMA fournissent un DMA évolutif basé sur des files d'attente pour déplacer d'énormes volumes de données avec un faible temps de latence, ainsi qu'une prise en charge de plusieurs fonctions physiques et virtuelles couramment requises par les produits d'entreprise. Les données peuvent être déplacées à l'aide de techniques de mappage mémoire, y compris le Network-on-Chip (NoC) programmable, ou de techniques de streaming, dans la logique programmable du SoC adaptatif Versal. Ces sous-systèmes comprennent également une fonctionnalité de pont vers l'interconnexion AXI.

- Le CPM4 comprend deux contrôleurs pour PCI Express et intègre également une instance d'un sous-système QDMA/XDMA/pont. L'utilisation du DMA intégré est facultative et, le cas échéant, il peut être configuré comme un sous-système QDMA tel que celui du CPM5 ou comme un sous-système XDMA. Les données peuvent être déplacées à l'aide de techniques de mappage mémoire, y compris le NoC programmable, ou de techniques de streaming, dans la logique programmable du SoC adaptatif Versal. Ce sous-système inclut également une fonctionnalité de pont vers l'interconnexion AXI.

- Les contrôleurs individuels PCI Express PL PCIE5 et PL PCIE4 sont pris en charge par des implémentations soft IP de sous-systèmes DMA/pont proposés par AMD dans le catalogue IP de Vivado™ Design Suite. Des solutions complémentaires sont également proposées par les partenaires AMD Embedded Computing.

Pour la plupart des utilisateurs, les sous-systèmes DMA/pont disponibles fournissent une infrastructure qui leur permet de gagner du temps et de réaliser des transferts de données rapides et performants. Consultez le Guide produit Versal Adaptive SoC CPM DMA and Bridge Mode for PCI Express (PG347), le Guide produit Versal Adaptive SoC DMA and Bridge Subsystem for PCI Express (PG344) et la solution AXI Bridge with DMA for PCIe du partenaire AMD Embedded Computing Smartlogic GmbH.

Les utilisateurs souhaitant connecter leur propre sous-système DMA/pont (afin de préserver leur investissement software dans les pilotes et les applications, de personnaliser ou d'optimiser les fonctionnalités grâce à une connaissance parfaite de l'application finale) disposent d'options pour concevoir directement avec les contrôleurs PCI Express dans les blocs CPM5, PL PCIE5, CPM4 et PL PCIE4. Consultez le Guide produit Versal Adaptive SoC CPM Mode for PCI Express (PG343) et le Guide produit Versal Adaptive SoC Integrated Block for PCI Express LogiCORE IP (PG346). Pour une liberté totale dans la mise en œuvre de solutions entièrement personnalisées, AMD fournit également un noyau soft IP PHY pour PCI Express, permettant aux concepteurs de connecter leurs propres contrôleurs PCI Express aux transceivers GTYP et GTY disponibles. Les partenaires AMD Embedded Computing, notamment Fidus Systems, Inc., offrent des services de développement et de conseil ainsi que des propositions de valeur uniques permettant de différencier et d'accélérer la conception avec les SoC adaptatifs Versal.