Soluções de SoCs adaptativos Versal AMD

Os sistemas que aproveitam as implementações da especificação PCI Express® estão presentes em aplicações de data center, comunicações e incorporadas. As várias opções de conectividade disponíveis na arquitetura Versal™ atendem diretamente às necessidades dos usuários de se concentrarem em sua competência principal e, ao mesmo tempo, de aproveitarem as interfaces avançadas baseadas em padrões. Os blocos integrados para PCI Express na arquitetura Versal oferecem níveis de desempenho premium com facilidade de uso e eficiência em relação às soluções de IP totalmente flexíveis. A arquitetura Versal integra cinco tipos de blocos integrados para PCI Express:

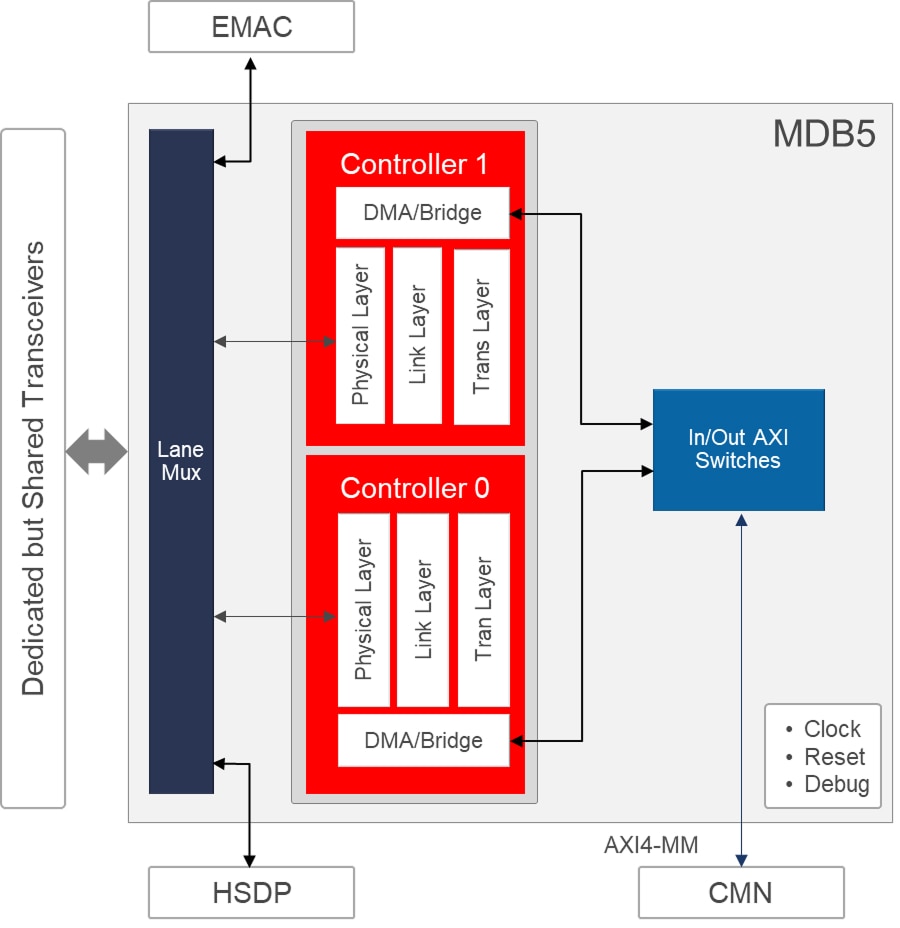

- MDB5: bloco integrado para PCI Express Rev. 5.0 com DMA/ponte

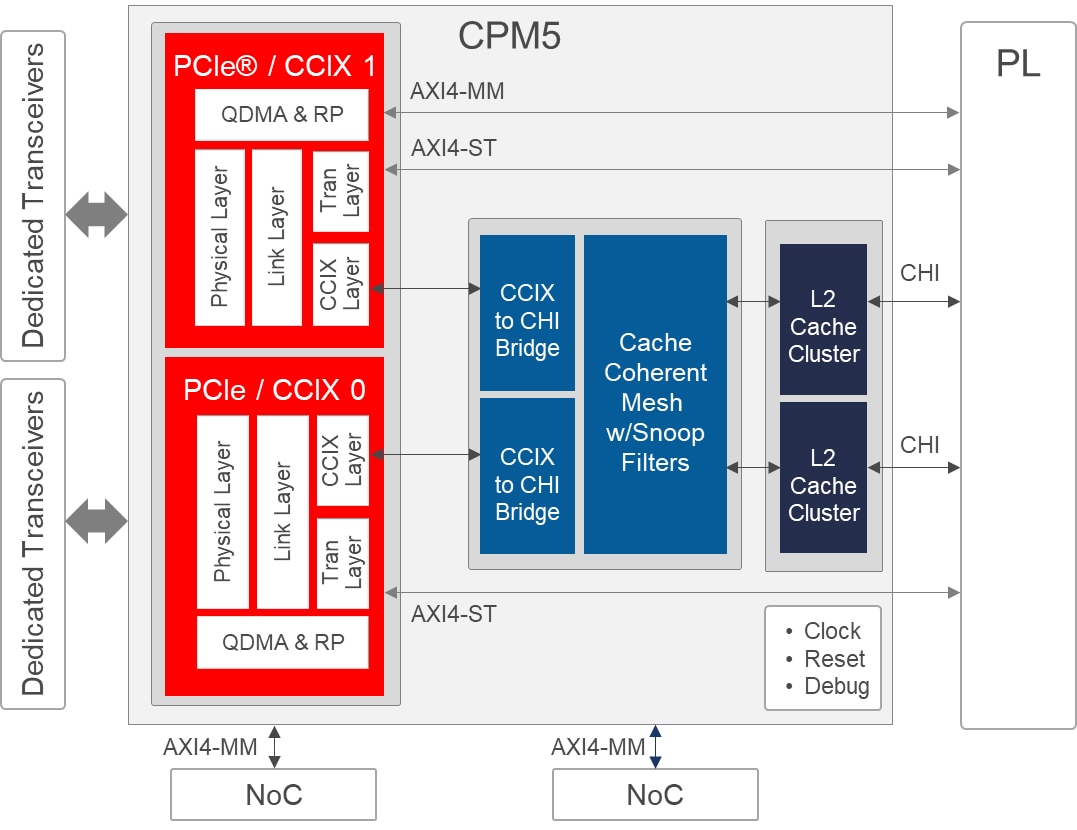

- CPM5: bloco integrado para PCI Express Rev. 5.0 com DMA/ponte

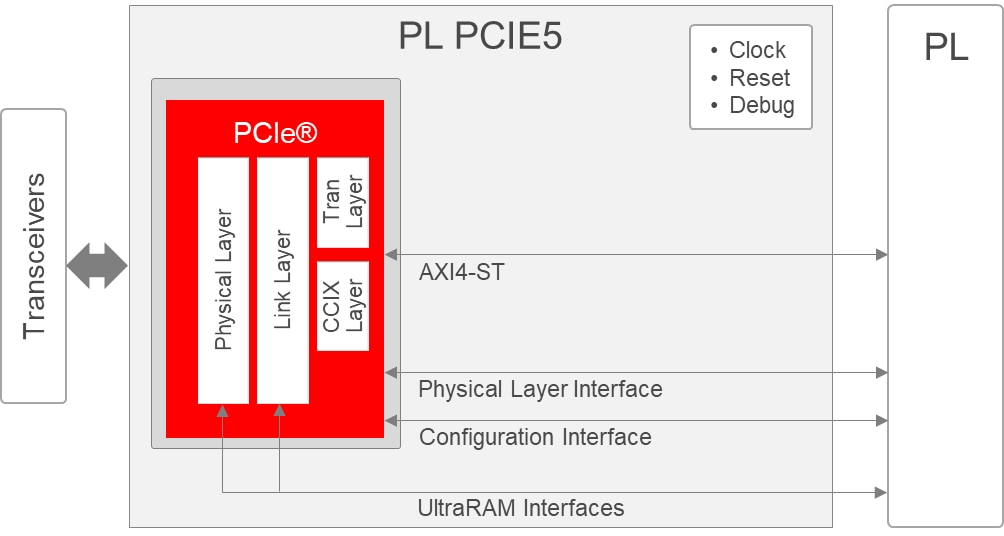

- PL PCIE5: bloco integrado para PCI Express Rev. 5.0

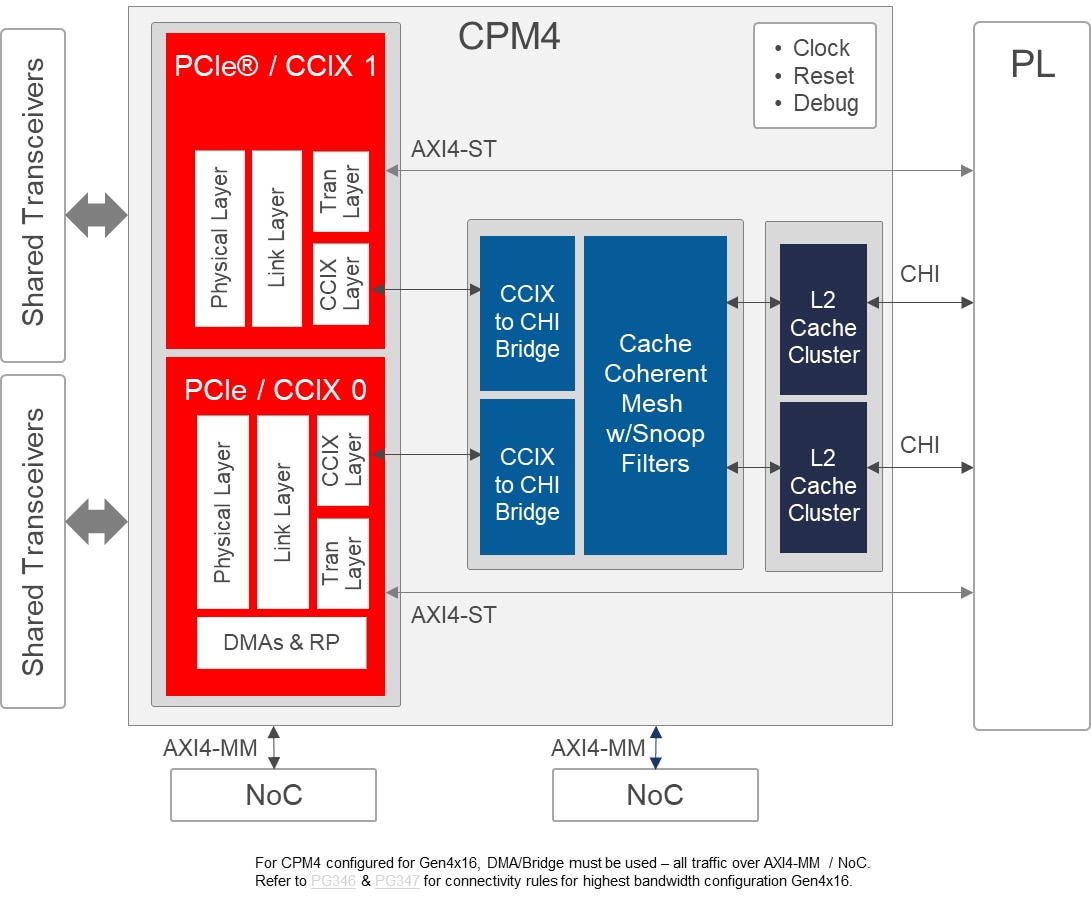

- CPM4: bloco integrado para PCI Express Rev. 4.0 com DMA/ponte

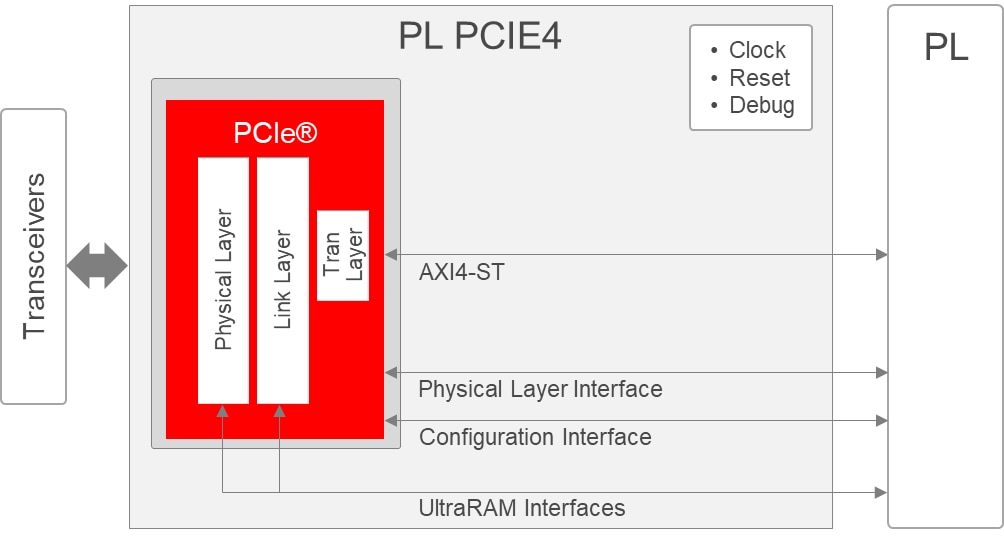

- PL PCIE4: bloco integrado para PCI Express Rev. 4.0

O MDB5, o CPM5, o PL PCIE5, o CPM4 e o PL PCIE4, em conjunto com os transceptores GTYP e GTY disponíveis, possibilitam a operação da interface em taxas de dados definidas pela especificação. Eles variam de 2,5 GT/s por faixa com uma faixa (Gen1x1) até suas configurações de link máximas classificadas, com alguns blocos integrados atingindo 32 GT/s por faixa com 8 faixas (Gen5x8) e 16 GT/s por faixa com 16 faixas (Gen4x16).

A tabela abaixo é um resumo das principais características dos blocos integrados para PCI Express na arquitetura Versal. Consulte a Folha de dados da arquitetura Versal e do produto: Visão geral (DS950) para informações adicionais sobre os recursos e capacidades disponíveis com base nas combinações de dispositivo comercializável, encapsulamento e classes de velocidade/tensão.

|

Blocos integrados da arquitetura Versal para PCI Express |

|---|

MDB5

Visualizar o diagrama

|

CPM5

Visualizar o diagrama

|

PL PCIE5

Visualizar o diagrama

|

CPM4

Visualizar o diagrama

|

PL PCIE4

Visualizar o diagrama

|

|---|

Associado

Especificações |

PCIe Rev. 5.0 |

PCIe Rev. 5.0 |

PCIe Rev. 5.0

|

PCIe Rev. 4.0

|

PCIe Rev. 4.0 |

|---|

PCIe máx.

Configurações de link |

Gen5x4

2 x Gen5x2

Gen5x2 |

2 x Gen5x8

Gen4x16

2 x Gen4x8 |

Gen5x4

Gen4x8

Gen3x16 |

Gen4x16

2 x Gen4x8 |

Gen4x8

Gen3x16 |

|---|

Porta PCIe

Tipo de suporte |

EP, RP |

EP, RP,

Comutador |

EP, RP,

Comutador |

EP, RP,

Comutador |

EP, RP,

Comutador |

|---|

PCIe principal

Recursos |

SR-IOV

8PF/64VF |

SR-IOV

16PF/4KVF |

SR-IOV

8PF/4KVF |

SR-IOV

4PF/252VF |

SR-IOV

4PF/252VF |

|---|

| DMA/ponte integrados |

Duas pontes necessárias,

Dois DMAs opcionais |

Dois opcionais

QDMA/Bridge |

- |

Um opcional

QDMA/Bridge ou XDMA/Bridge |

- |

|---|

O MDB5, o CPM5, o PL PCIE5, o CPM4 e o PL PCIE4 podem ser usados em configurações de link reduzidas para otimizar os projetos de produtos em termos de custo, suportar novos fatores de forma, aliviar a complexidade da placa e reduzir os orçamentos de energia. Além disso, as configurações de links reduzidas podem suportar uma menor utilização de recursos lógicos programáveis, dependendo da natureza de qualquer solução de IP flexível usada para expandir os recursos em nível de aplicativo desses blocos integrados. O CPM5, PL PCIE5, CPM4 e PL PCIE4 podem ser configurados como EP (Endpoint), RP (Root Port, Porta raiz) e tipos de porta de comutador. O MDB5 pode ser configurado como tipos de porta Endpoint (EP) e Root Port (RP).

Subsistemas de DMA/bridge de alto desempenho pré-verificados para os blocos integrados para PCI Express na arquitetura Versal permitem que os usuários concentrem seus investimentos de design nas áreas de maior valor. Os subsistemas de DMA/bridge disponíveis incluem:

- O MDB5 contém dois controladores para PCI Express e integra duas instâncias de um subsistema de DMA/bridge. O uso do DMA integrado é opcional, e cada instância pode ser personalizada de forma independente. Os subsistemas de DMA fornecem um acoplamento rígido aos processadores integrados e à interconexão AXI. Os subsistemas também incluem a funcionalidade de ponte. Os dados podem ser movidos com técnicas mapeadas na memória, incluindo a NoC (Network on Chip, Rede em chip) programável.

- O CPM5 contém dois controladores para PCI Express e também integra duas instâncias de um subsistema de QDMA/ponte. O uso do DMA integrado é opcional, e cada instância pode ser personalizada de forma independente. Os subsistemas de QDMA oferecem DMA dimensionável e baseado em filas para mover enormes volumes de dados com baixa latência, além de suporte para várias funções físicas e virtuais normalmente exigidas por produtos de classe empresarial. Os dados podem ser movidos com técnicas mapeadas na memória, incluindo a NoC, ou com técnicas de transmissão, para a lógica programável do SoC adaptativo Versal. Os subsistemas também incluem a funcionalidade de ponte para a interconexão AXI.

- O CPM4 contém dois controladores para PCI Express e também integra uma instância de um subsistema de QDMA/XDMA/ponte. O uso do DMA integrado é opcional. Quando usado, pode ser configurado como um subsistema de QDMA, como no CPM5, ou como um subsistema de XDMA. Os dados podem ser movidos com técnicas mapeadas na memória, incluindo a NoC, ou com técnicas de transmissão, para a lógica programável do SoC adaptativo Versal. O subsistema também inclui a funcionalidade de ponte para a interconexão AXI.

- O PL PCIE5 e o PL PCIE4 são controladores individuais para PCI Express, suportados por implementações de IP soft de subsistemas de DMA/bridge da AMD, disponíveis no catálogo Vivado™ Design Suite IP. Soluções adicionais também estão disponíveis por meio dos Parceiros de Computação Incorporada da AMD.

Para a maioria dos usuários, os subsistemas de DMA/bridge disponíveis podem fornecer uma infraestrutura que economiza tempo, permitindo a movimentação de dados pronta para uso e de alto desempenho. Confira o Guia do produto Versal Adaptive SoC CPM DMA and Bridge Mode for PCI Express (PG347), o Guia do produto Versal Adaptive SoC DMA and Bridge Subsystem for PCI Express (PG344) e a solução AXI Bridge com DMA para PCIe da Smartlogic GmbH, uma das Parceiras de Computação Incorporada da AMD.

Para os usuários que desejam anexar seu próprio subsistema de DMA/bridge — para preservar seu investimento em software de driver e de aplicativo ou para personalizar /otimizar a funcionalidade usando o conhecimento profundo do aplicativo final — há opções disponíveis para projetar diretamente nos controladores para PCI Express nos blocos CPM5, PL PCIE5, CPM4 e PL PCIE4. Consulte o Guia do produto Versal Adaptive SoC CPM Mode for PCI Express (PG343) e o Guia do produto Versal Adaptive SoC Integrated Block for PCI Express LogiCORE IP (PG343). Para que haja liberdade máxima na implementação de soluções totalmente personalizadas, a AMD oferece um núcleo IP soft PHY para PCI Express, permitindo que os projetistas conectem seus próprios controladores para PCI Express aos transceptores GTYP e GTY disponíveis. Os Parceiros de Computação Incorporada da AMD, incluindo a Fidus Systems, Inc., oferecem serviços de desenvolvimento e consultoria com propostas de valor exclusivas para diferenciar e acelerar projetos com oSoCs adaptativos Versal.