Adaptive AMD Versal SoC Lösungen

Systeme, die Implementierungen der PCI Express® Spezifikation nutzen, sind in Rechenzentren, Kommunikations- und Embedded-Anwendungen weit verbreitet. Die Vielzahl an Verbindungsoptionen in der Versal™ Architektur unterstützt direkt den Wunsch der Benutzer, sich auf ihre Kernkompetenz zu konzentrieren und gleichzeitig fortschrittliche, standardbasierte Schnittstellen zu nutzen. Im Vergleich zu vollständig Software-basierten IP-Lösungen bieten die integrierten Blöcke für PCI Express in der Versal Architektur eine erstklassige Performance bei hoher Benutzerfreundlichkeit. In die Versal Architektur sind fünf Arten integrierter Blöcke für PCI Express integriert:

- MDB5: integrierter Block für PCI Express Rev. 5.0 mit DMA/Bridge

- CPM5: integrierter Block für PCI Express Rev. 5.0 mit DMA/Bridge

- PL PCIE5: integrierter Block für PCI Express Rev. 5.0

- CPM4: integrierter Block für PCI Express Rev. 4.0 mit DMA/Bridge

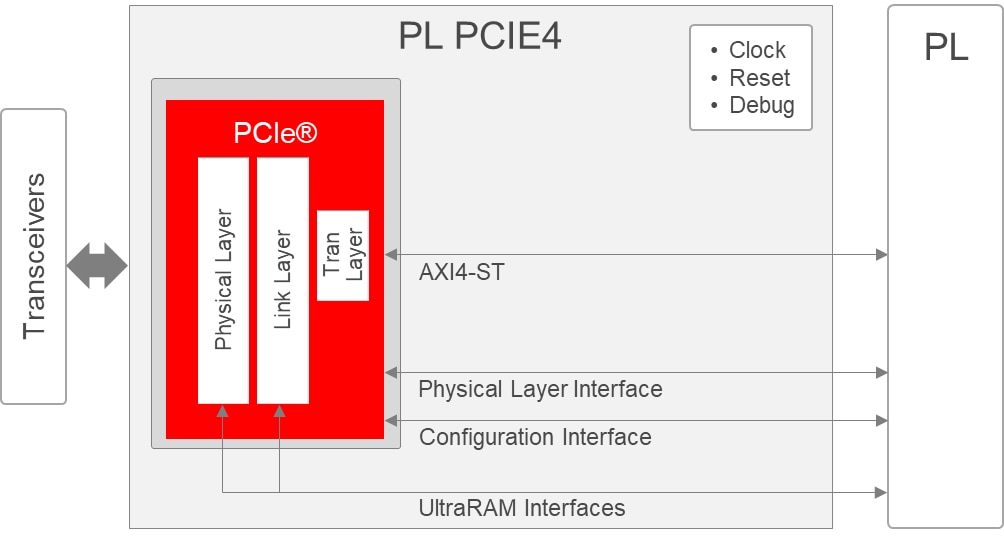

- PL PCIE4: integrierter Block für PCI Express Rev. 4.0

MDB5, CPM5, PL PCIE5, CPM4 und PL PCIE4 ermöglichen in Verbindung mit den verfügbaren GTYP- und GTY-Transceivern einen Schnittstellenbetrieb mit den in der Spezifikation definierten Datenraten. Diese reichen von 2,5 GT/s pro Lane mit einer Lane (Gen1x1) bis zur maximalen Verbindungskonfiguration, wobei einige integrierte Blöcke 32 GT/s pro Lane mit 8 Lanes (Gen5x8) und 16 GT/s pro Lane mit 16 Lanes (Gen4x16) erreichen.

Die folgende Tabelle fasst die wichtigsten Merkmale der integrierten Blöcke für PCI Express in der Versal Architektur zusammen. Im Versal Architecture and Product Data Sheet: Overview (DS950) finden Sie weitere Informationen zu verfügbaren Ressourcen und Fähigkeiten basierend auf bestellbaren Kombinationen aus Chip, Gehäuse und Geschwindigkeits-/Spannungsklasse.

|

Integrierte Blöcke für PCI Express der Versal Architektur |

|---|

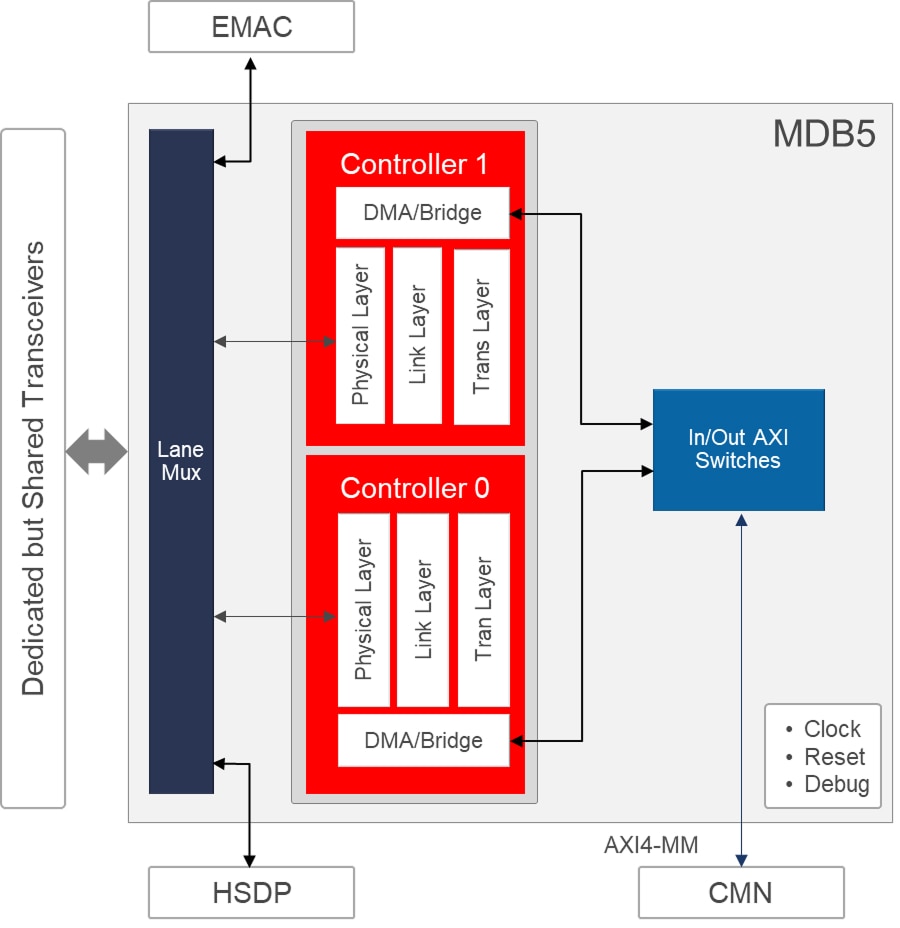

MDB5

Diagramm anzeigen

|

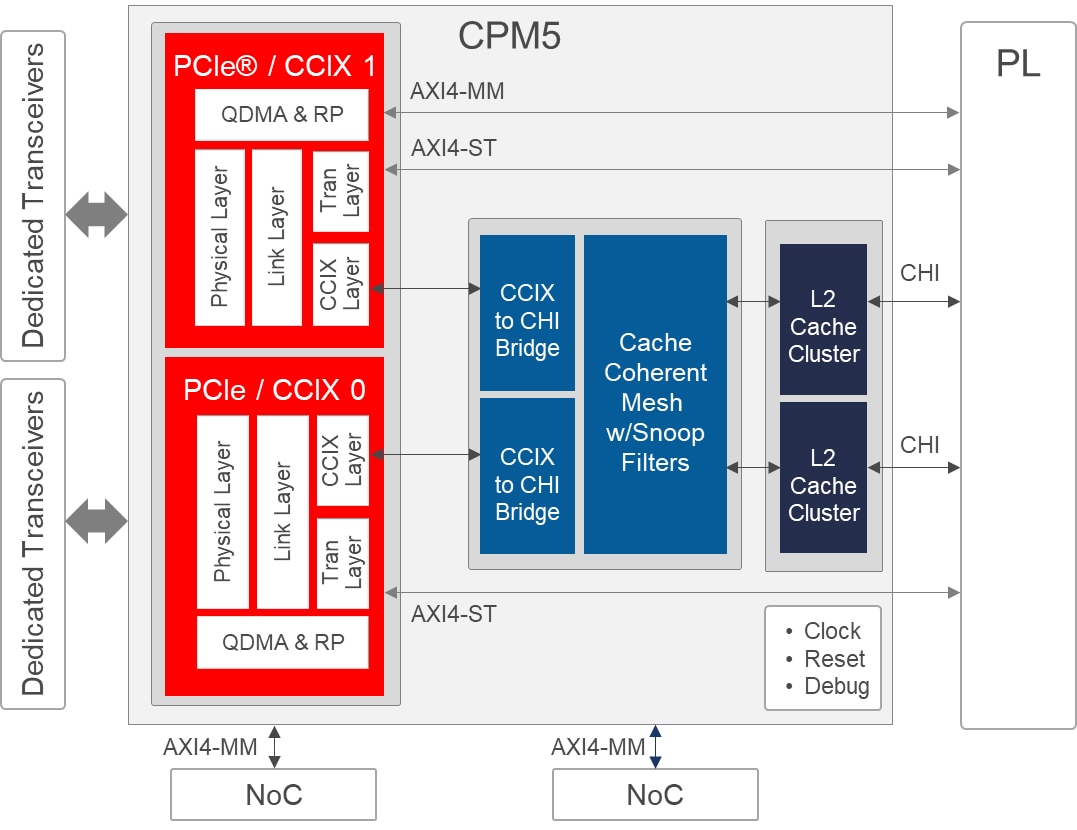

CPM5

Diagramm anzeigen

|

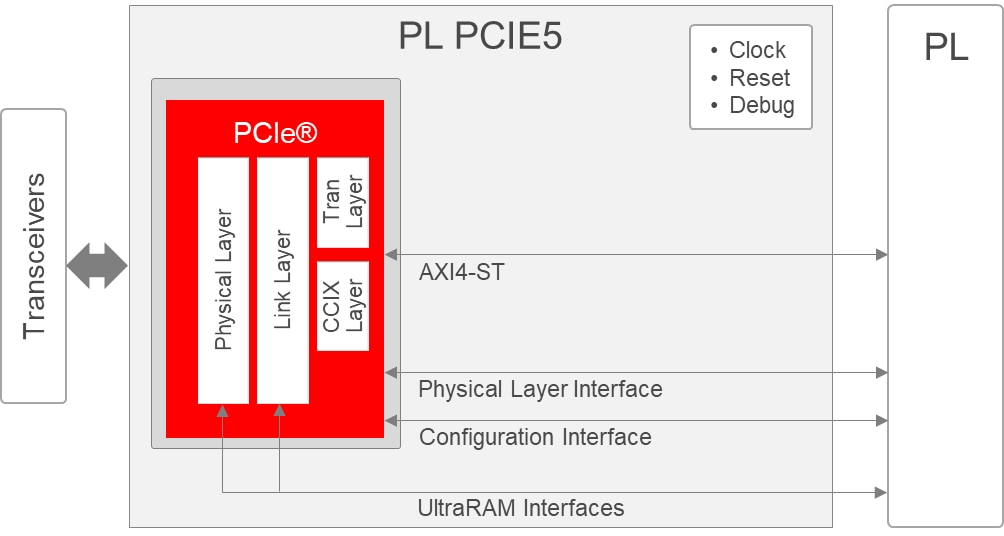

PL PCIE5

Diagramm anzeigen

|

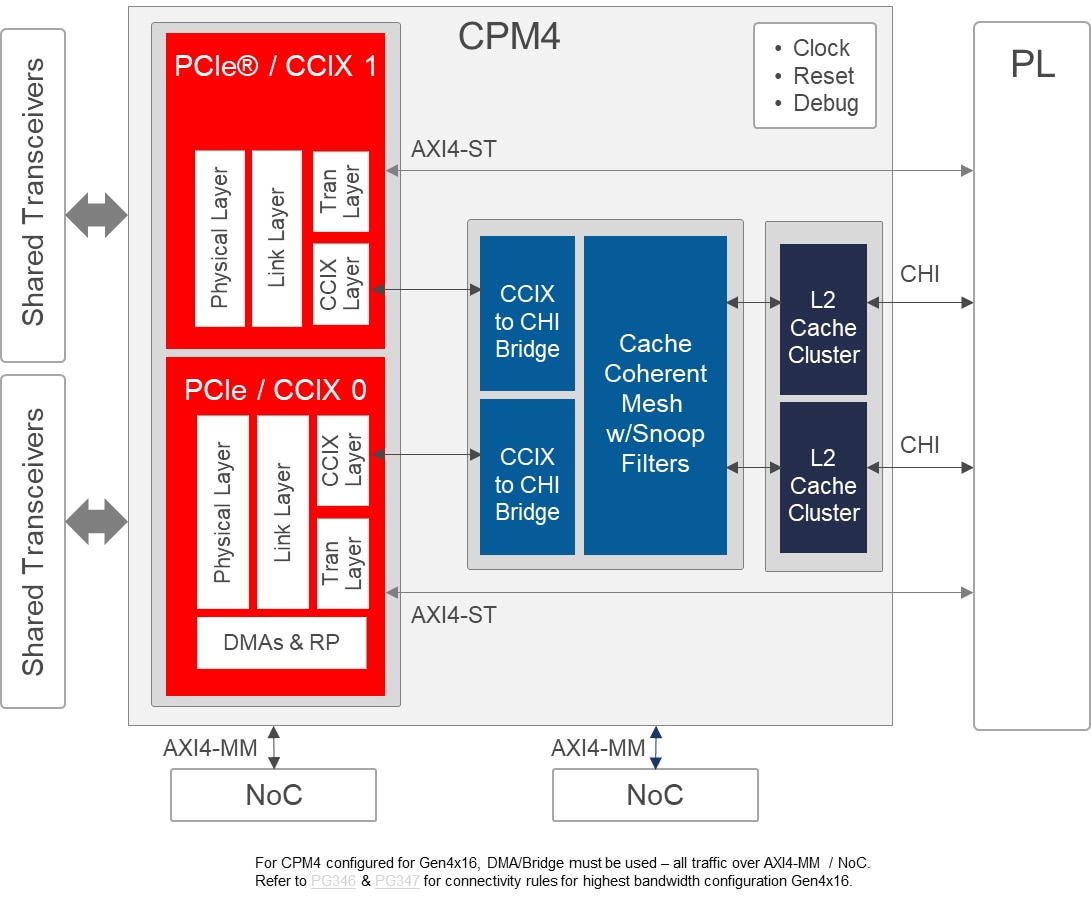

CPM4

Diagramm anzeigen

|

PL PCIE4

Diagramm anzeigen

|

|---|

Zugehörige

Technische Daten |

PCIe Rev. 5.0 |

PCIe Rev. 5.0 |

PCIe Rev. 5.0

|

PCIe Rev. 4.0

|

PCIe Rev. 4.0 |

|---|

Max. PCIe

Verbindungskonfig. |

Gen5x4

2 x Gen5x2

Gen5x2 |

2 x Gen5x8

Gen4x16

2 x Gen4x8 |

Gen5x4

Gen4x8

Gen3x16 |

Gen4x16

2 x Gen4x8 |

Gen4x8

Gen3x16 |

|---|

PCIe-Port

Typenunterstützung |

EP, RP |

EP, RP,

Switch |

EP, RP,

Switch |

EP, RP,

Switch |

EP, RP,

Switch |

|---|

PCIe Haupt-

Funktionen |

SR-IOV

8PF/64VF |

SR-IOV

16PF/4KVF |

SR-IOV

8PF/4KVF |

SR-IOV

4PF/252VF |

SR-IOV

4PF/252VF |

|---|

| Integration von DMA/Bridge |

Zwei Bridges erforderlich,

Zwei optionale DMAs |

Zwei optionale

QDMA/Bridge |

– |

Eine optionale

QDMA/Bridge oder XDMA/Bridge |

– |

|---|

MDB5, CPM5, PL PCIE5, CPM4 und PL PCIE4 können bei reduzierten Verbindungskonfigurationen verwendet werden, um Produktdesigns hinsichtlich der Kosten zu optimieren, neue Bauformen zu unterstützen, die Komplexität der Platinen zu verringern und Budgets für die Stromversorgung zu reduzieren. Je nachdem, welche Art von Soft-IP-Lösung zur Erweiterung der Fähigkeiten dieser integrierten Blöcke auf Anwendungsebene verwendet wird, können reduzierte Verbindungskonfigurationen außerdem eine geringere Nutzung der Ressourcen für programmierbare Logik unterstützen. Bei CPM5, PL PCIE5, CPM4 und PL PCIE4 kann der Port-Typ als Endpunkt (EP), Root Port (RP) und Switch konfiguriert werden. MDB5 kann als Endpoint- (EP-) und Root Port- (RP-) Port-Typen konfiguriert werden.

Vorab verifizierte High-Performance-DMA/Bridge-Subsysteme für die integrierten Blöcke für PCI Express in der Versal-Architektur ermöglichen es Benutzern, sich auf ihre wichtigsten Design-Bereiche zu konzentrieren. Folgende DMA/Bridge-Subsysteme stehen zur Verfügung:

- MDB5 enthält zwei Controller für PCI Express und integriert zwei Instanzen eines DMA/Bridge-Subsystems. Die Verwendung des integrierten DMA ist optional, und jede Instanz kann unabhängig voneinander angepasst werden. Die DMA-Subsysteme bieten eine enge Kopplung mit integrierten Prozessoren und dem AXI Interconnect. Die Subsysteme enthalten auch eine Bridge-Funktionalität. Daten können mit Memory-Mapped-Techniken (Abbildung in den Speicher) verschoben werden, wozu auch das programmierbare Network-on-Chip (NoC) gehört.

- CPM5 enthält zwei Controller für PCI Express und integriert auch zwei Instanzen eines QDMA/Bridge-Subsystems. Die Verwendung des integrierten DMA ist optional, und jede Instanz kann unabhängig voneinander angepasst werden. Die QDMA-Subsysteme bieten einen skalierbaren, warteschlangenbasierten Speicherdirektzugriff (Direct Memory Access, DMA) für das Verschieben riesiger Datenmengen mit geringer Latenz und zusätzlich Unterstützung für mehrere physische und virtuelle Funktionen, die üblicherweise von Produkten der Enterprise-Klasse benötigt werden. Daten können mit Memory-Mapped-Techniken verschoben werden, wozu auch das programmierbare Network-on-Chip (NoC) gehört, oder sie können mit Streaming-Techniken in die programmierbare Logik des adaptiven Versal SoC verschoben werden. Die Subsysteme enthalten auch eine Bridge-Funktionalität zum AXI Interconnect.

- CPM4 enthält zwei Controller für PCI Express und integriert auch eine Instanz eines QDMA/XDMA/Bridge-Subsystems. Die Verwendung des integrierten DMA ist optional und kann, sofern verwendet, als QDMA-Subsystem wie bei CPM5 oder als XDMA-Subsystem konfiguriert werden. Daten können mit Memory-Mapped-Techniken verschoben werden, wozu auch das programmierbare NoC gehört, oder sie können mit Streaming-Techniken in die programmierbare Logik des adaptiven Versal SoC verschoben werden. Das Subsystem enthält auch eine Bridge-Funktionalität zum AXI Interconnect.

- PL PCIE5 und PL PCIE4 sind individuelle Controller für PCI Express und werden durch Soft-IP-Implementierungen von DMA/Bridge-Subsystemen unterstützt, die bei AMD über den IP-Katalog der Vivado™ Design Suite zur Verfügung stehen – und weitere Lösungen sind bei AMD Embedded Computing Partnern erhältlich.

Für die meisten Benutzer können die verfügbaren DMA/Bridge-Subsysteme zeitsparende Infrastrukturen bereitstellen, die eine schlüsselfertige High-Performance-Datenverschiebung ermöglichen. Weitere Informationen finden Sie im Versal Adaptive SoC CPM DMA and Bridge Mode for PCI Express Product Guide (PG347), im Versal Adaptive SoC DMA and Bridge Subsystem for PCI Express Product Guide (PG344) und in der Lösung AXI Bridge with DMA for PCIe vom AMD Embedded Computing Partner Smartlogic GmbH.

Für Benutzer, die ihr eigenes DMA/Bridge-Subsystem anbinden möchten, um weiter von ihren Investitionen in Treiber und Anwendungssoftware zu profitieren oder um die Funktionalität durch ihre profunden Kenntnisse der Endanwendung anzupassen bzw. zu optimieren, gibt es Möglichkeiten, Designs direkt für Controller für PCI Express in den Blocks CPM5, PL PCIE5, CPM4 und PL PCIE4 zu entwickeln. Siehe Versal Adaptive SoC CPM Mode for PCI Express Product Guide (PG346) und Versal Adaptive SoC Integrated Block for PCI Express LogiCORE IP Product Guide (PG343). Für größtmögliche Freiheit bei der Implementierung vollständig benutzerdefinierter Lösungen bietet AMD eine Soft-IP-Core-PHY für PCI Express an, mit der Designer ihre eigenen Controller für PCI Express an verfügbare GTYP- und GTY-Transceiver anbinden können. AMD Embedded Computing Partner, einschließlich Fidus Systems, Inc., bieten Entwicklungs- und Beratungsservices mit einzigartigen Wertversprechen an, um das Design mit adaptiven Versal SoCs zu differenzieren und zu beschleunigen.