可编程系统集成

- 使用第二代 3D IC 时,以 20nm 制程工艺提供 550 万个系统逻辑单元

- 集成了 100G 以太网 MAC 和 150G Interlaken 的核

降低 BOM 成本

- 成本降低达 50%,是 Nx100G 系统每端口成本的一半

- 通过集成 VCXO 和小数分频 PLL 可降低时钟组件成本

- 中速等级芯片可支持 2400Mb/s DDR4

降低总功耗

- 功耗比上一代降低 40%

- 通过 UltraScale 器件的类似于 ASIC 的时钟实现精细时钟门控功能

- 增强型系统逻辑单元封装可减小动态功耗

提高设计生产力

- 与 Kintex™ UltraScale 器件封装兼容带来更高可扩展性

- 从 20nm 平面到 16nm FinFET 的无缝封装迁移

- 与 Vivado™ Design Suite 协同优化加快设计收敛

所有比较均基于 28nm Virtex 7 FPGA。

产品表

| XCVU065 | XCVU080 | XCVU095 | XCVU125 | XCVU160 | XCVU190 | XCVU440 | |

|---|---|---|---|---|---|---|---|

| 系统逻辑单元 (K) | 783 | 975 | 1,176 | 1,567 | 2,027 | 2,350 | 5,541 |

| DSP Slice | 600 | 672 | 768 | 1,200 | 1,560 | 1,800 | 2,880 |

| 内存 (Mb) |

44.3 | 50.0 | 60.8 | 88.6 | 115.2 | 132.9 | 88.6 |

| GTH 16.3Gb/s 收发器 | 20 | 32 | 32 | 40 | 52 | 60 | 48 |

| GTY 30.5Gb/s 收发器 | 20 | 32 | 32 | 40 | 52 | 60 | 0 |

| I/O 管脚数 | 520 | 832 | 832 | 802 |

702 |

702 |

1,456 |

立即体验

利用该套件提供的经过验证的硬件、软件支持、工具、设计示例和文档,快速启动您的设计周期,并实现快速上市。

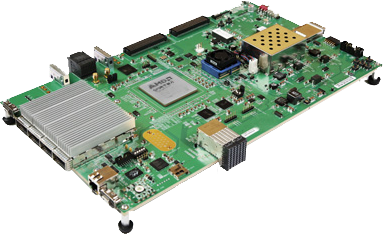

Virtex UltraScale FPGA VCU110 开发套件

Virtex UltraScale FPGA VCU110 开发套件是非常适合用于评估 Virtex UltraScale 器件出色性能、系统集成度以及带宽的开发环境。

支持和资源

联系销售人员

我们的销售团队将根据您的具体需求帮助您做出明智的技术决策。