AMD Virtex™ UltraScale™ 製品の特長

AMD Virtex UltraScale デバイスは、シリアル I/O 帯域幅やロジック容量など、20 nm で最高の性能と統合性を提供します。20 nm プロセス ノードで業界唯一のハイエンド FPGA となるこのファミリは、400G ネットワーキングから大規模な ASIC プロトタイピングやエミュレーションまで広範なアプリケーションに最適です。

アプリケーション

プログラム可能なシステム統合

- 第 2 世代 3D IC を採用した 20 nm プロセスで最大 550 万個のシステム ロジック セル

- 100G Ethernet MAC と 150G Interlaken コアを統合

BOM コストの削減

- 最大 50% のコスト削減 - Nx100G システムの場合、1 ポートあたりのコストが半分になる

- VCXO およびフラクショナル PLL の統合によって、クロッキング コンポーネント コストが削減

- ミッドレンジ スピード グレードで 2400 Mb/s DDR4

総消費電力が低減

- 前世代より最大 40% の消費電力を低減

- UltraScale デバイスの ASIC のようなクロッキング機能により、細粒度クロック ゲーティングが可能

- システム ロジック セルのパッキング機能の改善によりダイナミック消費電力が低減

設計の生産性向上

- Kintex™ UltraScale デバイスとのフットプリントの互換性があるため拡張性に優れている

- 20 nm プレーナから 16 nm FinFET へシームレスにフットプリントを移行

- Vivado™ Design Suite による同時最適化で迅速なデザイン クロージャを達成

すべての比較は 28 nm Virtex 7 FPGA に基づいています。

製品一覧

| XCVU065 | XCVU080 | XCVU095 | XCVU125 | XCVU160 | XCVU190 | XCVU440 | |

|---|---|---|---|---|---|---|---|

| システム ロジック セル (K) | 783 | 975 | 1,176 | 1,567 | 2,027 | 2,350 | 5,541 |

| DSP スライス | 600 | 672 | 768 | 1,200 | 1,560 | 1,800 | 2,880 |

| メモリ (Mb) |

44.3 | 50.0 | 60.8 | 88.6 | 115.2 | 132.9 | 88.6 |

| GTH 16.3Gb/s トランシーバー | 20 | 32 | 32 | 40 | 52 | 60 | 48 |

| GTY 30.5Gb/s トランシーバー | 20 | 32 | 32 | 40 | 52 | 60 | 0 |

| I/O ピン | 520 | 832 | 832 | 802 |

702 |

702 |

1,456 |

利用開始

実証済みの HW/SW サポート、ツール、デザイン サンプル、およびキットに対応した関連資料を利用することで、すぐに設計を開始して製品の市場投入までの期間を短縮できます。

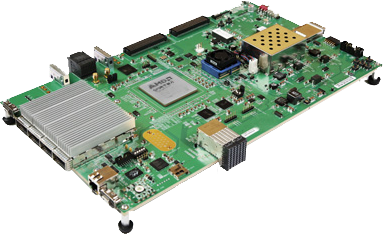

Virtex UltraScale FPGA VCU110 開発キット

Virtex UltraScale FPGA VCU110 開発キットは、Virtex UltraScale デバイスで実現する優れた性能、システム統合、および帯域幅を評価するのための完全な開発環境です。

サポートとリソース

営業に問い合わせ

AMD のセールス チームがお客様のニーズに合ったベストな技術的判断ができるようお手伝いいたします。