可程式化系統整合

- 利用第 2 代 3D IC,最高達 5.5M 的 20 奈米系統邏輯單元

- 整合 100G 乙太網路 MAC 和 150G Interlaken 核心

BOM 成本降低

- 成本最高省下 50%,對於 Nx100G 系統,每個連接埠的成本可直接減半

- 整合 VCXO 和小數 PLL,可降低時脈元件成本

- 中速等級為 2400 Mb/s DDR4

總功耗降低

- 相較於上一代產品,降低功耗最高達 40%

- 使用 UltraScale 器件的類 ASIC 時脈,精細調整時脈閘控

- 增強系統邏輯單元封裝,減少動態功耗

提升設計效率

- 使用空間與 Kintex™ UltraScale 器件相同,適合進行擴充

- 在尺寸及腳位方面,能從 20 奈米平面製程,流暢移轉至 16 奈米 FinFET

- 與 Vivado™ Design Suite 共同最佳化,以利迅速完成設計

所有比較的比較對象都是 28 奈米的 Virtex 7 FPGA。

產品表格

| XCVU065 | XCVU080 | XCVU095 | XCVU125 | XCVU160 | XCVU190 | XCVU440 | |

|---|---|---|---|---|---|---|---|

| 系統邏輯單元 (K) | 783 | 975 | 1,176 | 1,567 | 2,027 | 2,350 | 5,541 |

| DSP 配量 | 600 | 672 | 768 | 1,200 | 1,560 | 1,800 | 2,880 |

| 記憶體 (Mb) |

44.3 | 50.0 | 60.8 | 88.6 | 115.2 | 132.9 | 88.6 |

| GTH 16.3 Gb/s 收發器 | 20 | 32 | 32 | 40 | 52 | 60 | 48 |

| GTY 30.5 Gb/s 收發器 | 20 | 32 | 32 | 40 | 52 | 60 | 0 |

| I/O 腳位 | 520 | 832 | 832 | 802 |

702 |

702 |

1,456 |

開始

利用套件所提供的經實證的硬體、軟體支援、工具、設計範例及文件,快速展開設計週期並快速上市。

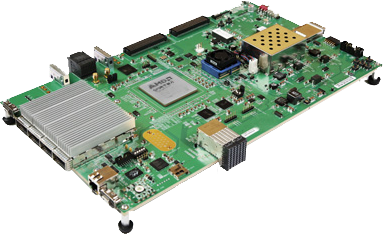

Virtex UltraScale FPGA VCU110 開發套件

Virtex UltraScale FPGA VCU110 開發套件在評估 Virtex UltraScale 器件無與倫比的出色效能、系統整合性和頻寬等方面,實為相當理想的開發環境。

支援與資源

聯絡銷售人員

我們的銷售團隊會根據您的特定需求,協助您做出最佳的技術決策。