Comercio algorítmico de ULL

Desde el comercio algorítmico complejo hasta los servicios de creación de mercados

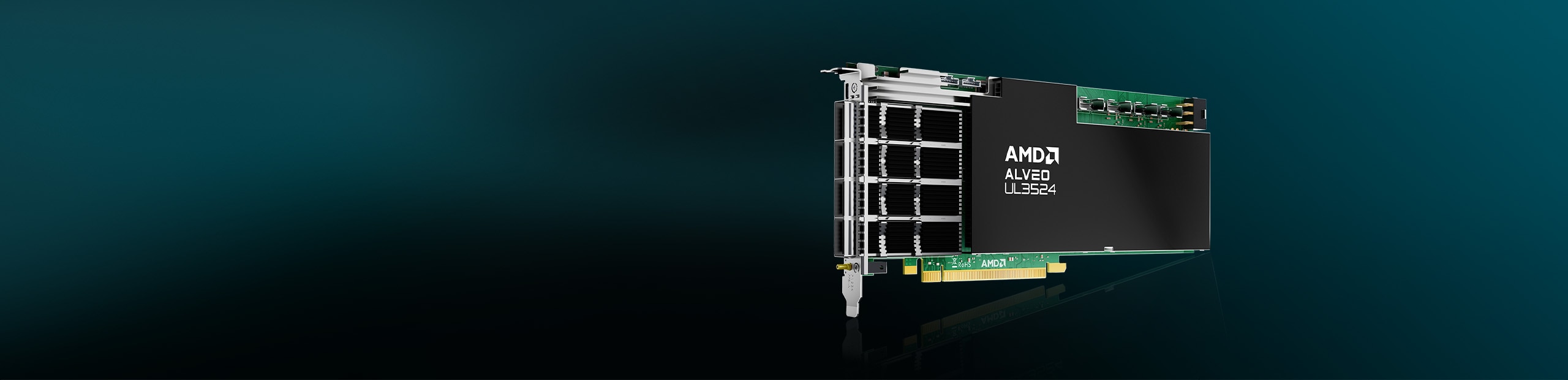

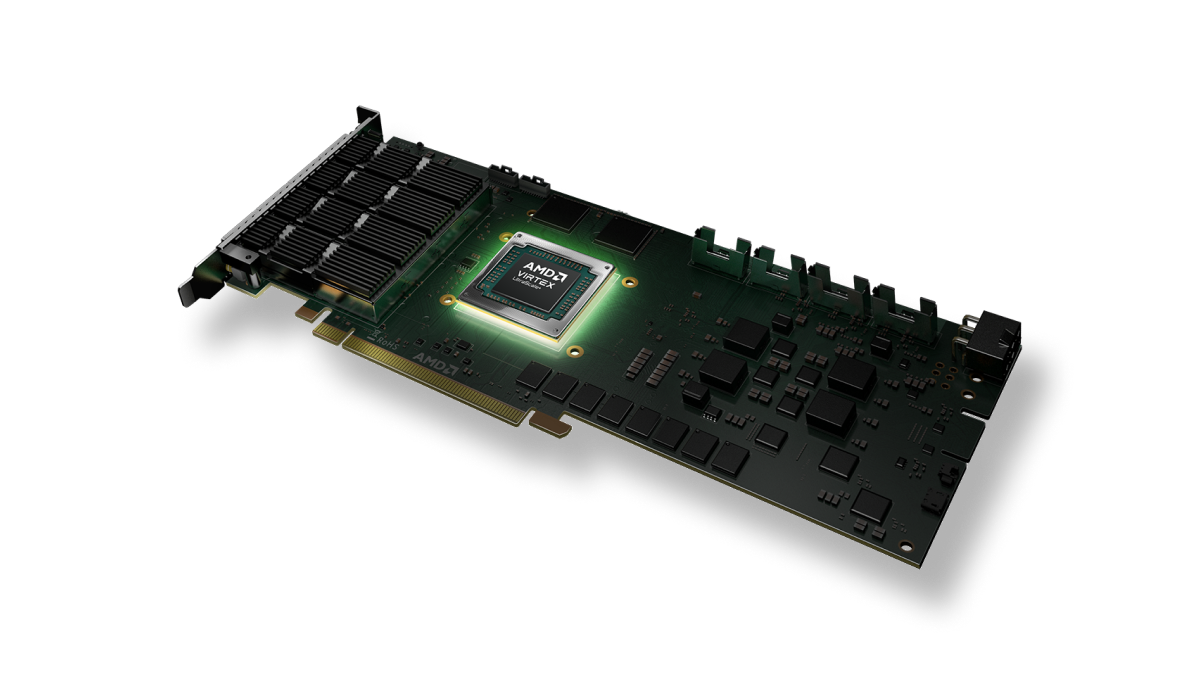

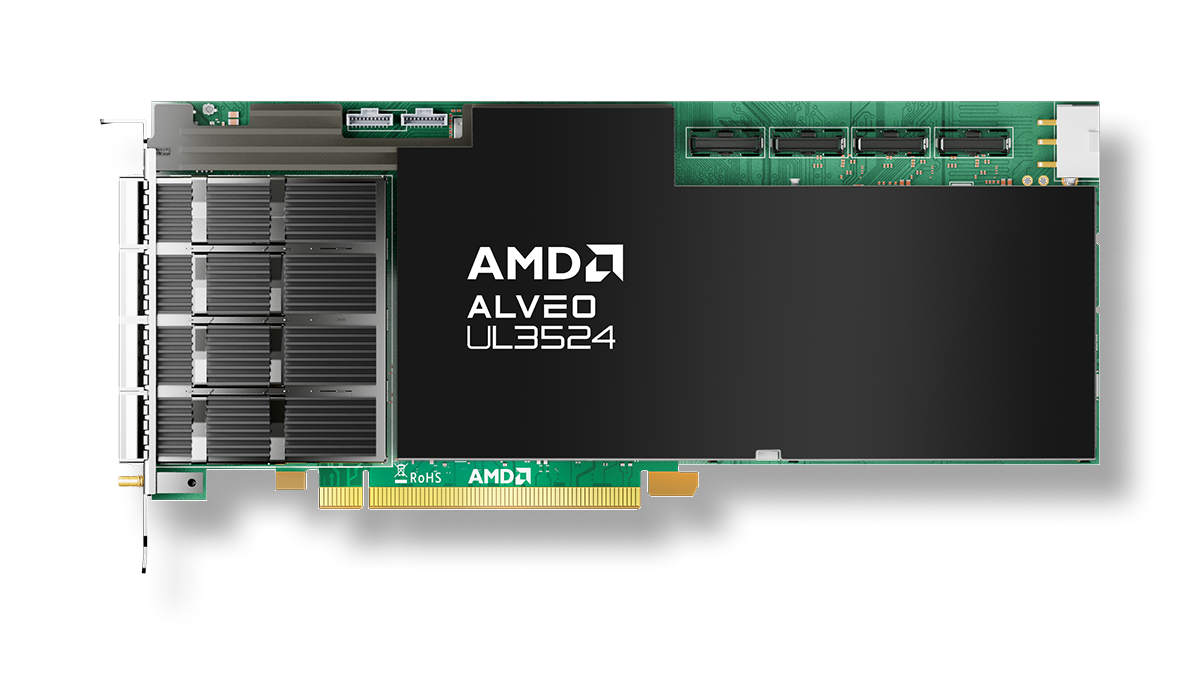

Nueva AMD Alveo™ UL3524 para operaciones comerciales con latencia ultrabaja

Latencia de transceptor inferior a 3 ns1 para una ejecución comercial determinista de alto rendimiento

Los desarrolladores pueden integrar modelos de IA de baja latencia en el sistema comercial utilizando el diseño tradicional de FPGA, así como flujos de desarrollo de código abierto de PyTorch

Aceleración de hardware para comercio algorítmico, análisis de riesgos previos al comercio y entrega de datos de mercado

La AMD Alveo™ UL3524 cuenta con tecnología de una nueva FPGA Virtex UltraScale+™ diseñada para el comercio electrónico. El dispositivo tiene una revolucionaria arquitectura de transceptor que logra una latencia inferior a 3 ns para una ejecución comercial de primer nivel1 y proporciona siete veces más rendimiento en comparación con la tecnología de FPGA anterior2.

Con 64 transceptores de latencia ultrabaja, 780 000 LUT de estructura de FPGA (Field-Programmable Gate Arrays, matriz de puertas lógicas programable en campo) y 1680 cortes de DSP (Digital Signal Processing, procesamiento de señales digitales), la tarjeta aceleradora Alveo UL3524 está diseñada para acelerar los algoritmos de comercio personalizados en hardware, en los que los corredores de bolsa pueden adaptar su diseño a las condiciones de mercado y las estrategias en constante evolución.

La tarjeta aceleradora Alveo UL3524 es compatible con la Vivado™ Design Suite para flujos de FPGA tradicionales. AMD también ofrece a los desarrolladores el marco de desarrollo FINN de código abierto y apoyado por la comunidad, lo que permite implementar modelos de IA de baja latencia en sistemas comerciales de alto rendimiento.

Las empresas comerciales patentadas, los fondos de cobertura, los creadores de mercado, los corretajes y los proveedores de datos pueden implementar el acelerador Alveo UL3524 para el comercio algorítmico de ULL, la administración de riesgos previos al comercio, la entrega de datos de mercado y mucho más. La convergencia de la aceleración de hardware, la flexibilidad de FPGA y las redes de baja latencia garantizan un alto rendimiento y determinismo en una amplia gama de casos de uso.

El acelerador Alveo UL3524 es compatible con flujos de desarrollo tradicionales de RTL que utilizan la Vivado™ Design Suite. Los diseños de referencia a fin de evaluar la latencia y el rendimiento, así como para probar otras funciones de la tarjeta, están disponibles en el repositorio de GitHub.

Se requiere una licencia especial para permitir el dispositivo Virtex™ UltraScale+ objetivo. Los desarrolladores pueden solicitar acceso al sitio seguro de Alveo UL3524 para obtener licencias y acceder a documentación técnica adicional.

La tarjeta aceleradora Alveo UL3524 se puede implementar en servidores de 1U, 2U y 4U, lo que la hace flexible para diversos requisitos de formato y rack de servidores

El servidor de alta frecuencia Hypertec Orion HF X410R-G6 de 1U ya está disponible con un sistema de refrigeración personalizado para la tarjeta aceleradora Alveo UL3524. Comunícate con nosotros para obtener más información.

Comienza hoy mismo con la tarjeta aceleradora Alveo UL3524. Disponible ahora en AMD y distribuidores autorizados.

La Alveo™ UL3524 cuenta con tecnología de una nueva FPGA Virtex UltraScale+™ diseñada para el comercio electrónico. El dispositivo tiene una revolucionaria arquitectura de transceptor que logra una latencia inferior a 3 ns para una ejecución comercial de primer nivel y proporciona siete veces más rendimiento en comparación con la tecnología de FPGA anterior.

La tarjeta aceleradora de FPGA Alveo UL3524 combina redes de latencia ultrabaja con hardware adaptable para acelerar las estrategias de comercio a una velocidad de nanosegundos.

Regístrate para recibir las últimas novedades sobre centros de datos o comunícate con un representante de ventas de AMD.

1. Pruebas realizadas en los laboratorios de rendimiento de AMD al 16/8/23 en la tarjeta aceleradora Alveo UL3524, que usa Vivado Design Suite 2023.1 y se ejecuta en Vivado Lab (Hardware Manager) 2023.1. Información basada en GTF Latency Benchmark Design configurado para permitir transceptores GTF en modo de bucle cercano al extremo interno. Los relojes de TX y RX GTF operan a la misma frecuencia de aproximadamente 644 MHz, con un desfase de 180 grados. GTF Latency Benchmark Design mide la latencia en el hardware mediante el registro del valor de un único contador de ejecución libre. La latencia se mide como la diferencia entre el momento en que los datos de TX se registran en el transceptor GTF y el momento en que los datos de TX se registran en el receptor GTF antes de ser redirigidos nuevamente al FPGA. La medición de latencia no incluye la sobrecarga de protocolo, el encuadre de protocolo, la latencia PL (programmable logic, lógica programable), el tiempo de configuración de la interfaz PL de TX, la interfaz PL de RX de reloj a salida, el tiempo de vuelo de los paquetes ni otras fuentes de latencia. La prueba de evaluación comparativa se ejecutó 1000 veces con 250 cuadros por prueba. El resultado de medición citado se basa en el “modo RAW” del transceptor GTF, en el que la PCS (physical medium attachment, conexión de medio físico) del transceptor transmite los datos “tal como están” a la estructura de FPGA. La medición de la latencia es coherente en todas las pruebas realizadas para esta configuración. Los fabricantes de sistemas pueden variar las configuraciones, lo que arroja resultados diferentes. ALV-10

2. Información basada en una comparación de simulación entre los transceptores GTY Virtex UltraScale+ y los transceptores GTF de latencia ultrabaja.