超低延迟算法交易

适用于复杂的算法交易和做市服务

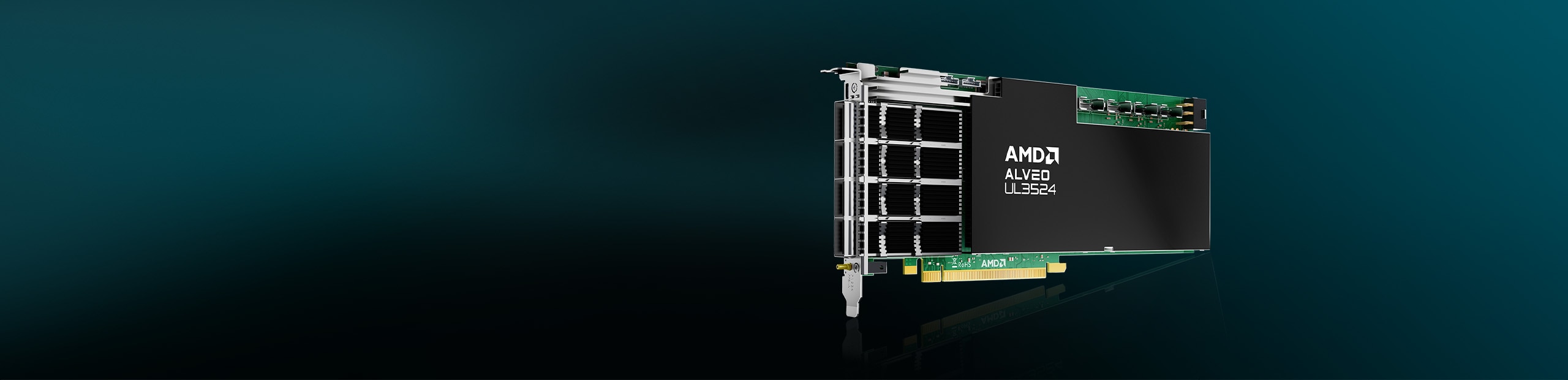

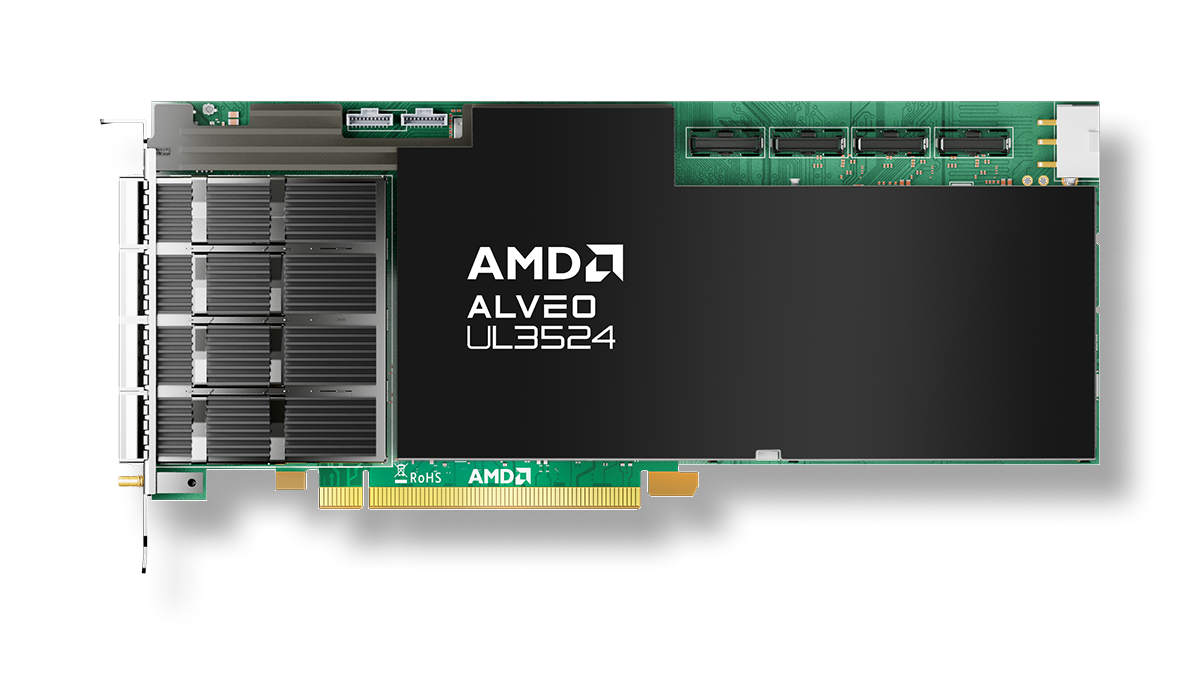

全新 AMD Alveo™ UL3524,专为以超低延迟执行交易而打造

收发器延迟不到 3ns1,可实现高性能的确定性交易执行

开发者可使用传统 FPGA 设计以及开源 PyTorch 开发流程将低延迟 AI 模型整合到交易系统中

面向算法交易、交易前风险分析以及市场数据传输的硬件加速

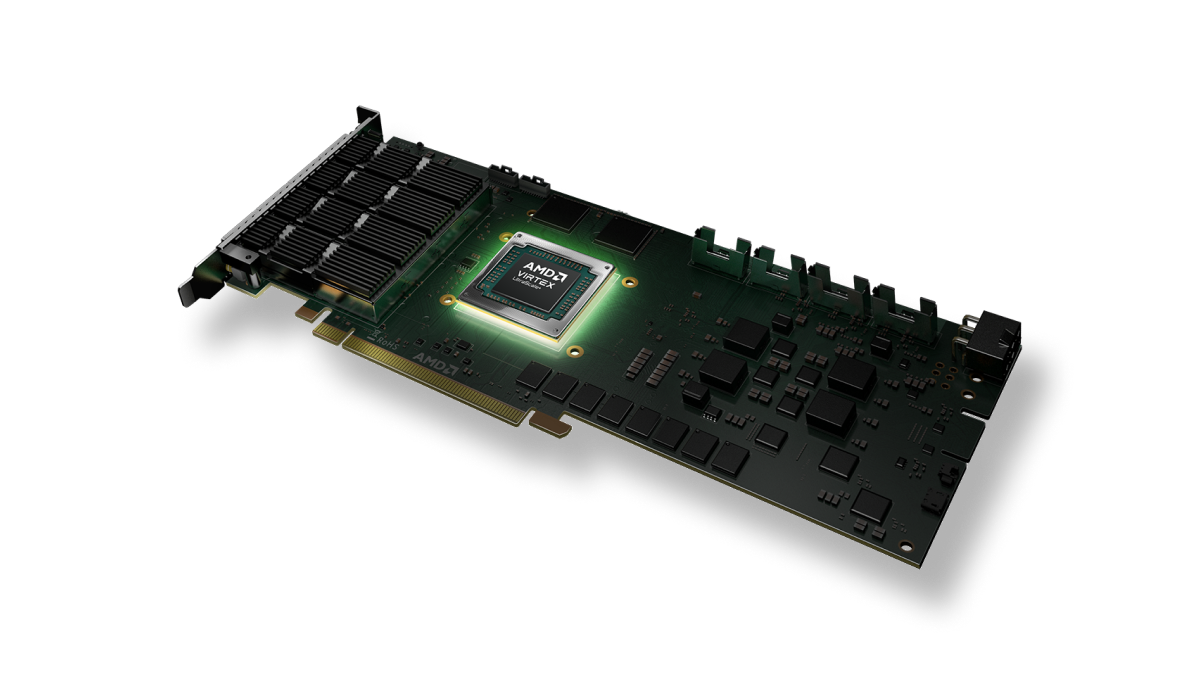

AMD Alveo™ UL3524 采用专为电子交易打造的全新 Virtex UltraScale+™ FPGA。该器件采用突破性的收发器架构实现低于 3ns 的延迟,带来卓越的交易执行速度1,与以前的 FPGA 技术2相比,性能锐增 7 倍。

Alveo UL3524 加速器卡支持 64 个超低延迟收发器、78 万个 LUT 的 FPGA 结构和 1,680 个 DSP 计算 silce,专门用于通过硬件来加速自定义交易算法,交易者可以根据不断变化的策略和市场条件灵活调整其设计。

Alveo UL3524 加速器卡由面向传统 FPGA 流程的 Vivado™ Design Suite 提供支持。AMD 还为开发者提供开源和社区支持的 FINN 开发框架,使低延迟 AI 模型能够部署到高性能交易系统中。

自营交易公司、对冲基金、做市商、经纪公司和数据供应商可以部署 Alveo UL3524 加速器进行超低延迟算法交易,提供交易前风险管理、市场数据传输等功能。硬件加速、FPGA 灵活性和低延迟网络全面结合,可确保在各类应用场景下实现高性能和高确定性。

Alveo UL3524 加速器支持使用 Vivado™ Design Suite 进行传统的 RTL 开发。用于评估延迟和性能以及测试加速器卡其他功能的参考设计可通过 GitHub 库获。

需要特殊许可才能启用目标 Virtex™ UltraScale+ 器件。开发者可申请访问 Alveo UL3524 Secure Site 以获取许可和访问其他技术文档。

Alveo UL3524 加速器卡可部署在 1U、2U 和 4U 服务器中,灵活满足不同的服务器机架及外形需求。

1U Hypertec Orion HF X410R-G6 高频服务器现已上市,针对 Alveo UL3524 加速器卡配备了定制散热系统。联系我们了解更多信息。

立即体验 Alveo UL3524 加速器卡。该产品目前可从 AMD 和授权分销商处购买。

Alveo™ UL3524 采用专为电子交易打造的全新 Virtex UltraScale+™ FPGA。该器件采用突破性的收发器架构,可实现低于 3ns 的延迟,带来卓越的交易执行速度,与以前的 FPGA 技术相比,性能锐增 7 倍。

Alveo UL3524 FPGA 加速器卡将超低延迟网络与自适应硬件相结合,能够以纳秒级速度加速执行交易策略。

订阅接收最新数据中心动态,或与 AMD 销售代表取得联系。

1.基于 AMD 性能实验室于 2023 年 8 月 16 日对 Alveo UL3524 加速器卡进行的测试,该测试使用 Vivado Design Suite 2023.1 并在 Vivado Lab(硬件管理器)2023.1 上运行。测试采用 GTF Latency Benchmark Design,其经过配置,会在内部近端回送模式下启用 GTF 收发器。GTF TX 和 RX 时钟在 180 度相移情况下,以相同频率运行,约为 644MHz。GTF Latency Benchmark Design 通过锁存单个自由运行计数器的值来测量硬件延迟。延迟是指从 TX 数据在 GTF 收发器处锁存到 TX 数据在导回 FPGA 结构之前在 GTF 接收器处锁存之间的时间差。延迟测量结果不涵盖协议开销、协议成帧、可编程逻辑 (PL) 延迟、TX PL 接口设置时间、RX PL 接口时钟输出、包无线传输时间及其他延迟情况。基准测试运行 1000 次,每次测试 250 帧。引用的测量结果基于 GTF 收发器“RAW 模式”,其中该收发器通过物理介质连接 (PCS) 将数据“按原样”传给 FPGA 架构。在该配置下运行的所有测试中,延迟测量结果是一致的。系统制造商可能会采用不同的配置,因而得到不同的结果。ALV-10

2.基于 Virtex UltraScale+ GTY 收发器与超低延迟 GTF 收发器的仿真比较。