Algorithmischer ULL-Handel

Vom komplexen algorithmischen Handel bis hin zu Market-Making-Services

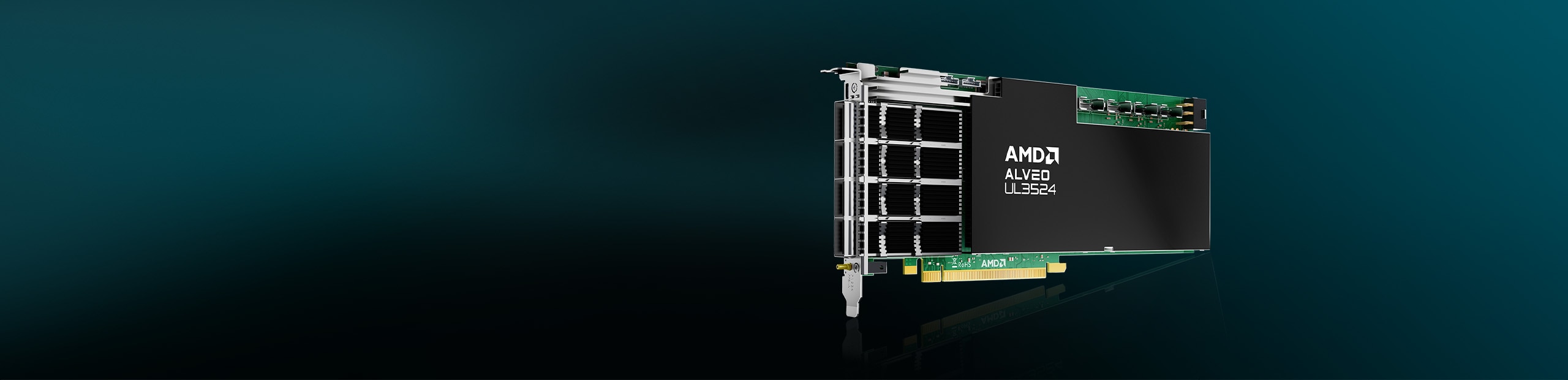

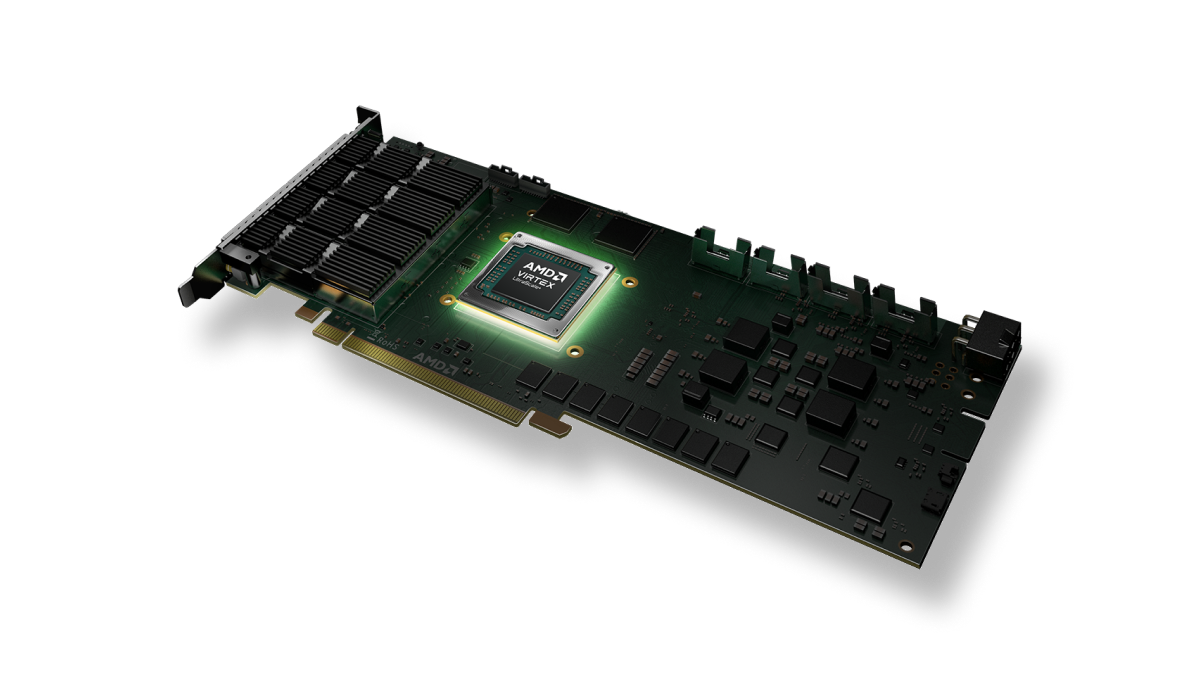

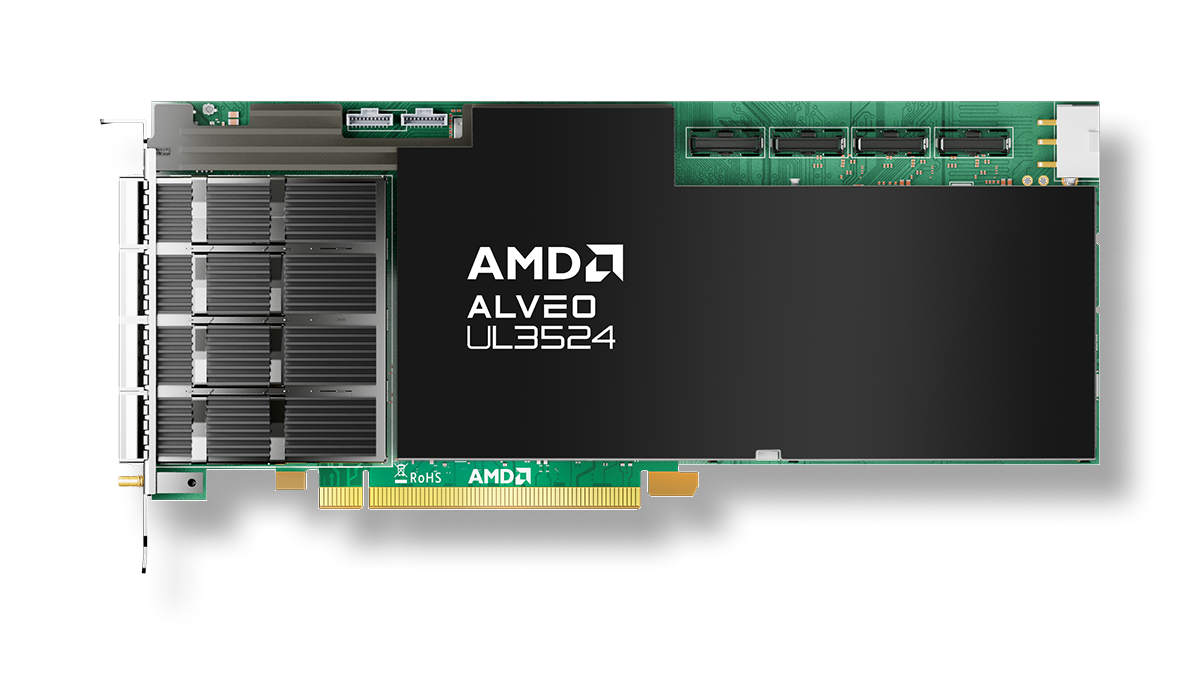

Die neue AMD Alveo™ UL3524 für den Handel mit extrem niedriger Latenz

Weniger als 3 ns Transceiver-Latenzzeit1 für eine hochperformante, deterministische Handelsausführung

Entwickler können KI-Modelle mit niedriger Latenz in das Handelssystem integrieren und dafür das traditionelle FPGA-Design oder Open-Source-PyTorch-Entwicklungsabläufe nutzen.

Hardwarebeschleunigung für algorithmischen Handel, Pre-Trade-Risikoanalyse und Bereitstellung von Marktdaten

Die AMD Alveo™ UL3524 ist mit einem neuen, für den elektronischen Handel entwickelten Virtex UltraScale+™ FPGA ausgestattet. Der Chip verfügt über eine bahnbrechende Transceiver-Architektur, die eine Latenzzeit von weniger als 3 ns für eine erstklassige Handelsausführung1 bietet und im Vergleich zur vorherigen FPGA-Technologie eine bis zu 7-mal höhere Performance ermöglicht2.

Mit 64 Transceivern mit extrem niedriger Latenz, FPGA-Struktur mit 780.000 LUTs und 1.680 DSP-Recheneinheiten ist die Alveo UL3524 Beschleunigerkarte darauf ausgelegt, benutzerdefinierte Handelsalgorithmen in der Hardware zu beschleunigen, sodass Händler ihr Konzept an sich weiterentwickelnde Strategien und Marktbedingungen anpassen können.

Die Alveo UL3524 Beschleunigerkarte wird von der Vivado™ Design Suite für herkömmliche FPGA-Flows unterstützt. AMD stellt Entwicklern auch das Open-Source- und von der Community unterstützte FINN Entwicklungs-Framework zur Verfügung, mit dem KI-Modelle mit geringer Latenz in High-Performance-Handelssystemen bereitgestellt werden können.

Eigenhandelsunternehmen, Hedgefonds, Market Maker, Broker und Datenanbieter können den Alveo UL3524 Beschleuniger für den algorithmischen ULL-Handel, Pre-Trade-Risikomanagement, Bereitstellung von Marktdaten und vieles mehr einsetzen. Die Konvergenz von Hardwarebeschleunigung, FPGA-Flexibilität und Netzwerken mit geringer Latenz gewährleistet eine hohe Performance und Deterministik in einer Vielzahl von Anwendungsfällen.

Der Alveo UL3524 Beschleuniger wird von traditionellen RTL-Entwicklungsabläufen mit der Vivado™ Design Suite unterstützt. Referenzkonzepte zur Bewertung von Latenz und Performance sowie zum Testen anderer Funktionen der Karte sind im GitHub Repository verfügbar.

Um die Virtex™ UltraScale+-Einheit als Ziel zu aktivieren, ist eine spezielle Lizenzierung erforderlich. Entwickler können für die Lizenzierung und den Zugriff auf zusätzliche technische Dokumentation Zugang zur Alveo UL3524 Secure Site beantragen.

Die Alveo UL3524 Beschleunigerkarte kann in Servern mit 1 HE, 2 HE und 4 HE eingesetzt werden – flexibel für verschiedene Anforderungen an Server-Racks und Bauformen.

Der Hochfrequenz-Server Hypertec Orion HF X410R-G6 mit 1 HE ist jetzt verfügbar, ausgestattet mit einem speziellen Kühlsystem für die Alveo UL3524 Beschleunigerkarte. Kontaktieren Sie uns, wenn Sie weitere Informationen wünschen.

Legen Sie noch heute los mit der Alveo UL3524 Beschleunigerkarte. Jetzt verfügbar von AMD und autorisierten Händlern.

Die Alveo™ UL3524 ist mit einem neuen, für den elektronischen Handel entwickelten Virtex UltraScale+™ FPGA ausgestattet. Der Chip verfügt über eine bahnbrechende Transceiver-Architektur, die eine Latenzzeit von weniger als 3 ns für eine erstklassige Handelsausführung bietet und im Vergleich zur vorherigen FPGA-Technologie eine bis zu 7-mal höhere Performance ermöglicht.

Die Alveo UL3524 FPGA Beschleunigerkarte kombiniert Netzwerke mit extrem niedriger Latenz mit anpassungsfähiger Hardware, um Handelsstrategien im Nanosekundentakt zu beschleunigen.

Melden Sie sich an, um alle Neuigkeiten zum Thema Rechenzentrum zu erhalten oder um mit einem AMD Vertriebsmitarbeiter Kontakt aufzunehmen.

1. Die Tests wurden vom AMD Leistungslabor am 16.08.23 auf der Alveo UL3524 Beschleunigerkarte durchgeführt, unter Verwendung von Vivado Design Suite 2023.1, die auf Vivado Lab (Hardware Manager) 2023.1 läuft. Basierend auf dem GTF Latency Benchmark Design, das so konfiguriert ist, dass GTF-Transceiver im internen Near-End-Loopback-Modus aktiviert werden. GTF TX- und RX-Taktungen arbeiten mit gleichen Frequenz von ~644 MHz mit einer Phasenverschiebung von 180 Grad. Das GTF Latency Benchmark Design misst die Latenz in der Hardware durch Latching des Wertes eines einzelnen Zählers im Free-Running-Betrieb. Latenz wird als Differenz zwischen dem Zeitpunkt gemessen, an dem TX-Daten im GTF-Transceiver gespeichert werden, und dem Zeitpunkt, an dem TX-Daten im GTF-Empfänger gespeichert werden, bevor sie in die FPGA-Struktur zurückgeleitet werden. Nicht in der Latenzmessung berücksichtigt sind Protokoll-Overhead, Protokoll-Framing, Latenz der programmierbaren (PL), Einrichtungszeit der TX-PL-Schnittstelle, Clock-to-Out der RX-PL-Schnittstelle, Paketlaufzeit und weitere Latenzquellen. Der Benchmark-Test wurde 1.000 Mal mit 250 Frames pro Test ausgeführt. Das angegebene Messergebnis basiert auf dem „RAW-Modus“ des GTF-Transceivers, bei dem PCS (Physical Medium Attachment) des Transceivers die Daten unverändert („as-is“) an die FPGA-Struktur weitergibt. Die Latenzmessung ist konsistent bei allen Testläufen für diese Konfiguration. Systemhersteller wählen möglicherweise andere Konfigurationen, was zu anderen Ergebnissen führen kann. ALV-10

2. Basierend auf einem Simulationsvergleich zwischen Virtex UltraScale+ GTY-Transceivern und GTF-Transceivern mit extrem niedriger Latenz.