ULL アルゴリズム取引

複雑なアルゴリズム取引からマーケット メーカーのサービスに対応

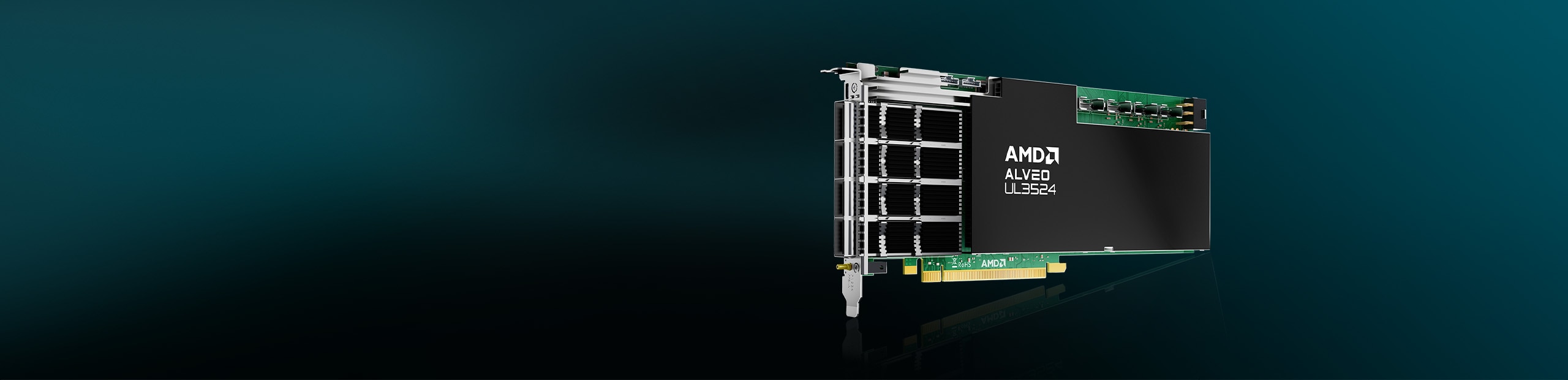

超低レイテンシ取引向けの新しい AMD Alveo™ UL3524

3 ns 未満のトランシーバー レイテンシ1 を達成し、高性能かつ確定的な取引の実行が可能

従来の FPGA 設計手法や、オープンソースの PyTorch 開発フローを使用して、取引システムに低レイテンシの AI モデルを統合できる

ハードウェア アクセラレーション機能により、アルゴリズム取引、取引前のリスク評価、マーケット情報の提供などのさまざまなアプリケーションを高速化

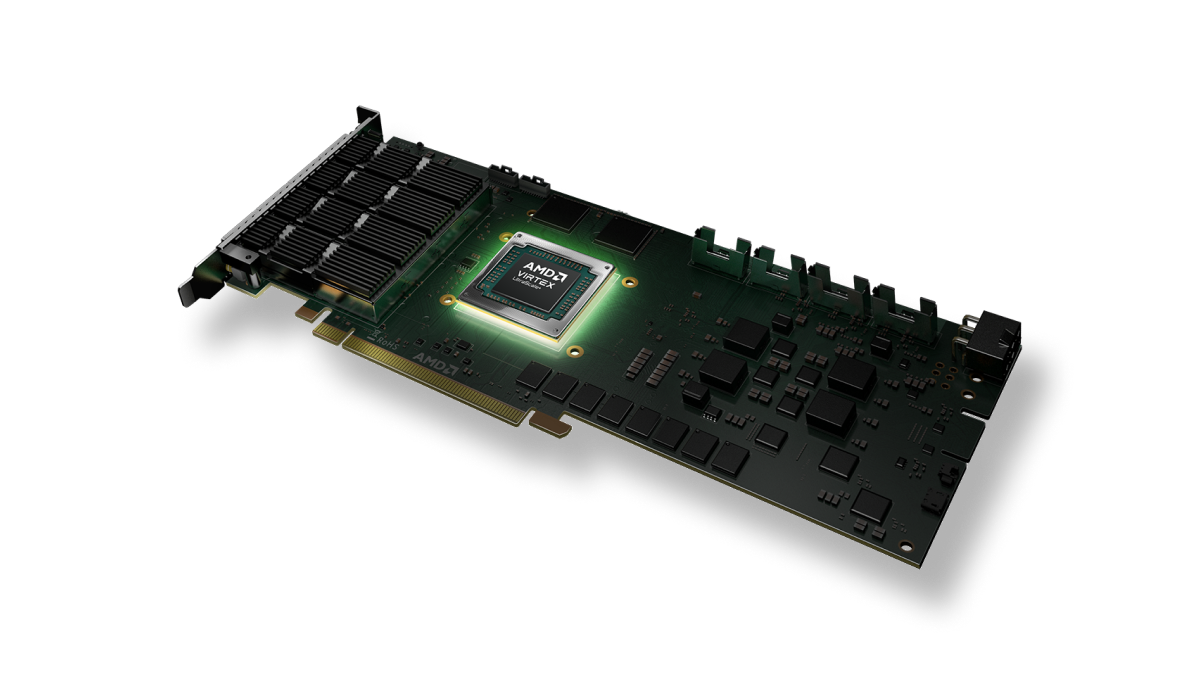

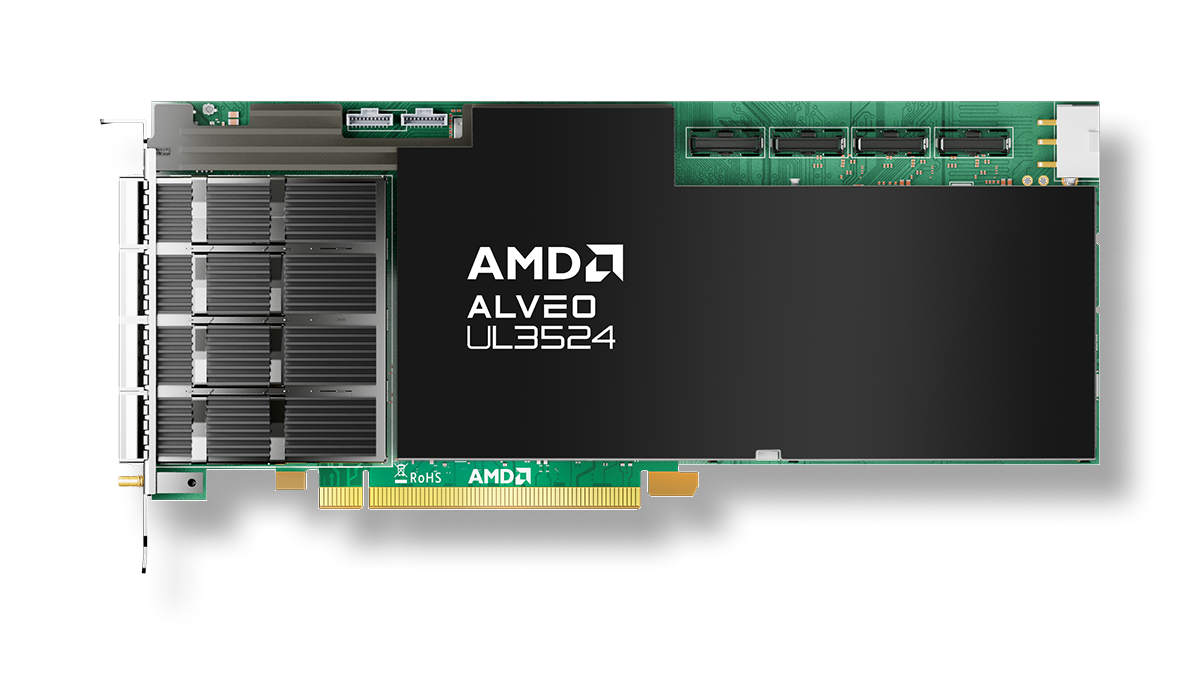

新しい Virtex UltraScale+™ FPGA を搭載した AMD Alveo™ UL3524 は、電子取引向けに構築されています。このデバイスは、世界トップ クラスの取引を実現するために 3 ns 未満の超低レイテンシ1 を可能にする革新的なトランシーバー アーキテクチャを採用しており、従来の FPGA 技術より 7 倍優れた性能を提供します。2

64 個の超低レイテンシ トランシーバー、78 万個の LUT、および 1,680 個の DSP スライスによる計算能力を統合した Alveo UL3254 アクセラレータ カードは、独自の取引アルゴリズムをハードウェアで高速化するために構築されたソリューションです。このカードを使用することで、独自のアルゴリズムを簡単に変更し、進化する戦略や市況に適応させることが可能になります。

Alveo UL3524 アクセラレータ カードは、従来型 FPGA フロー向けの Vivado™ Design Suite で設計可能です。また、AMD は、オープンソースでコミュニティによってサポートされる FINN 開発フレームワークを提供し、低レイテンシな AI モデルを高性能な取引システムに展開できるよう支援しています。

プロプライエタリ トレーディング会社、ヘッジ ファンド、マーケット メーカー、証券会社、データ ベンダーは、ULL アルゴリズム取引、取引前のリスク管理、マーケット情報の提供など、さまざまな用途に Alveo UL3524 アクセラレータを活用できます。ハードウェア アクセラレーション、FPGA の柔軟性、低レイテンシ ネットワーキングをすべて備えることができるため、あらゆるアプリケーションで高性能かつ確定的な動作を実現できます。

Alveo UL3524 アクセラレータは、Vivado™ Design Suite を使用した従来の RTL 開発フローに対応しています。レイテンシや性能の評価、ならびにその他のカード機能の検証のためのリファレンス デザインは GitHub リポジトリで提供しています。

ターゲットの Virtex™ UltraScale+ デバイスを有効にするには特別なライセンスが必要になります。開発者は Alveo UL3524 セキュア サイトへのアクセスをリクエストして、ライセンスおよび詳細な技術資料を入手できます。

Alveo UL3524 アクセラレータ カードは、1U、2U、および 4U で運用でき、さまざまなサーバー ラックの種類および形状要件に適応できます。

現在、Alveo UL3524 アクセラレータ カード向けのカスタム冷却システムを搭載した 1U の Hypertec Orion HF X410R-G6 高周波数サーバーが提供されています。詳細情報については、こちらよりお問い合わせください。

Alveo UL3524 アクセラレータ カードで設計を開始しましょう。AMD および正規販売でご購入いただけます。

最新の Virtex UltraScale+™ FPGA を搭載した Alveo™ UL3524 は、電子取引向けに構築されています。このデバイスは、世界トップ クラスの取引を実現するために 3 ns 未満の超低レイテンシを可能にする革新的なトランシーバー アーキテクチャを採用しており、従来の FPGA 技術より 7 倍優れた性能を提供します。

Alveo UL3524 FPGA アクセラレータ カードは、超低レイテンシのネットワーク技術と適応型ハードウェアを組み合わせることで、取引戦略をナノ秒単位で高速化します。

サインアップすると、データセンターに関する最新情報の受信や、AMD の営業担当者へのお問い合わせが可能になります。

1.2023 年 8 月 16 日に AMD パフォーマンス ラボが実施したテスト結果に基づいています。このテストでは、Vivado Design Suite 2023.1 と Vivado Lab (ハードウェア マネージャー) 2023.1 を使用して Alveo UL3524 アクセラレータ カードを実行しました。使用した GTF レイテンシ ベンチマーク デザインは、内部で近端ループバック モードの GTF トランシーバーを有効にするように構成されています。GTF の TX クロックと RX クロックは、位相が 180 度シフトしており、約 644 MHz の同じ周波数で動作します。GTF レイテンシ ベンチマーク デザインは、単一のフリーランニング カウンターの値をラッチしてハードウェアのレイテンシを測定します。TX データが GTF トランシーバーでラッチされた時点と、FPGA ファブリックにルーティング バックされる前に TX データが GTF レシーバーでラッチされた時点の差がレイテンシとして測定されます。レイテンシ測定値には、プロトコルのオーバーヘッド、プロトコル フレーミング、プログラマブル ロジック (PL) のレイテンシ、TX PL インターフェイスのセットアップ時間、RX PL インターフェイスの clock-to-out 時間、パッケージ フライト時間など、その他のレイテンシは含まれません。ベンチマーク テストは 1000 回実行され、各テストで 250 フレームを処理しています。測定結果は、「RAW モード」の GTF トランシーバー動作に基づいたものです。つまりトランシーバーの PCS (physical medium attachment) がそのままのデータを FPGA ファブリックに送信します。この設定で実行されるレイテンシ測定は、すべてのテストで一貫しています。システム メーカーの構成によって、異なる結果が生じる場合があります。ALV-10

2.Virtex UltraScale+ GTY トランシーバーと超低レイテンシ GTF トランシーバーのシミュレーション比較に基づいた結果です。