Trading algorithmique ULL

Du trading algorithmique complexe aux services des teneurs de marchés

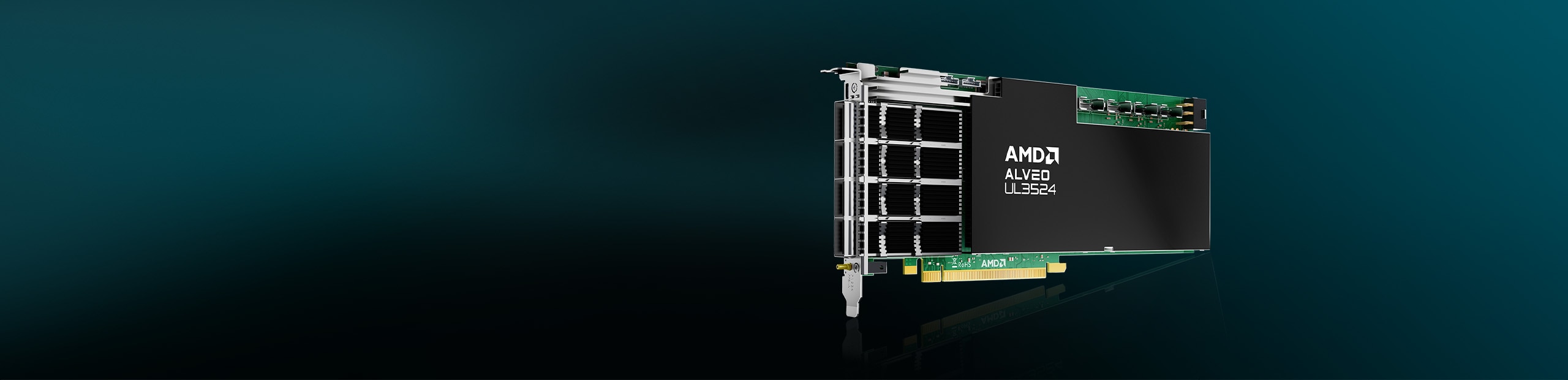

Nouvel Alveo™ UL3524 pour le trading à très faible temps de latence

Temps de latence des transceivers inférieur à 3 ns1 pour une exécution des transactions déterministe hautes performances

Les développeurs peuvent intégrer des modèles d'IA à faible temps de latence dans un système de trading à l'aide d'une conception FPGA traditionnelle ainsi que de flux de développement PyTorch open source

Accélération hardware pour le trading algorithmique, l'analyse des risques avant transaction et la livraison de données de marché

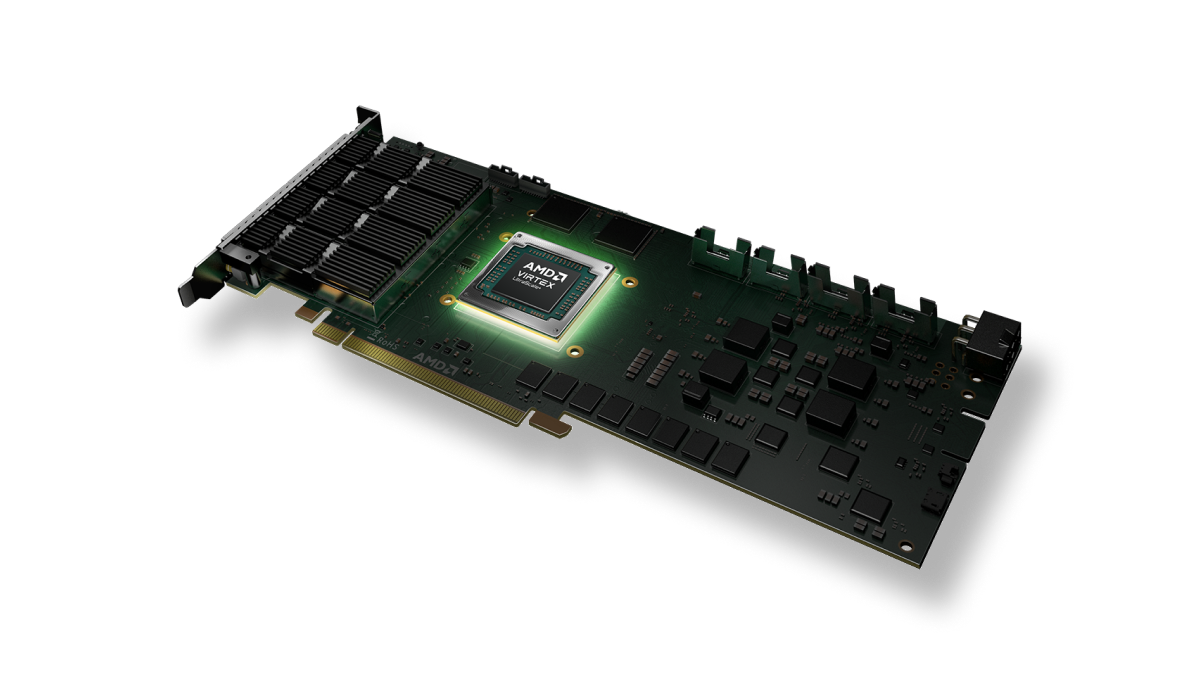

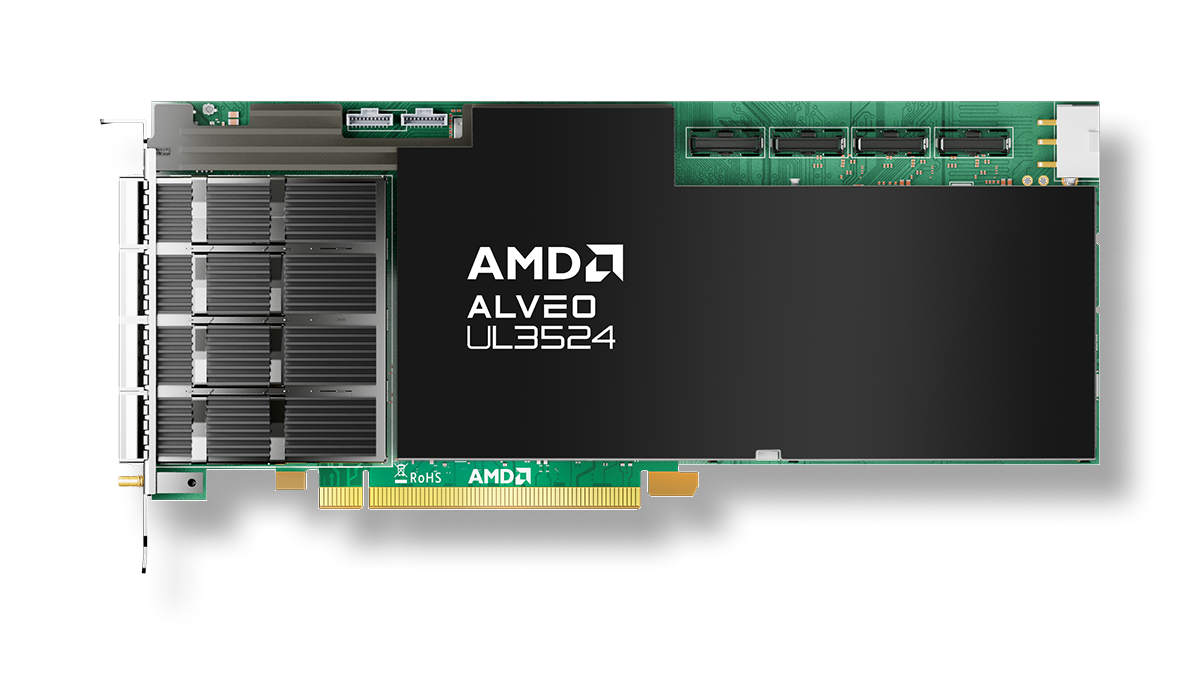

La carte AMD Alveo™ UL3524 est alimentée par un nouveau FPGA Virtex UltraScale+™ conçu pour le trading électronique. Cet appareil est doté d'une architecture de transceiver révolutionnaire qui permet d'atteindre un temps de latence inférieur à 3 ns pour une exécution des transactions de classe mondiale1, offrant des performances jusqu'à 7 fois supérieures à celles de la technologie FPGA précédente2.

Avec 64 transceivers à très faible temps de latence, 780 000 LUT de structure de FPGA et 1 680 unités de calcul DSP, la carte d'accélération Alveo UL3524 est conçue pour accélérer les algorithmes de trading personnalisés au niveau du hardware, où les traders peuvent adapter leur design à l'évolution des stratégies et des conditions du marché.

La carte d'accélération Alveo UL3524 est prise en charge par Vivado™ Design Suite pour les flux FPGA traditionnels. AMD fournit également aux développeurs le cadre de développement FINN open source et communautaire, permettant de déployer des modèles d'IA à faible temps de latence dans des systèmes de trading hautes performances.

Les sociétés de trading propriétaires, les fonds spéculatifs, les teneurs de marchés, les courtiers et les fournisseurs de données peuvent déployer l'accélérateur Alveo UL3524 pour le trading algorithmique ULL, la gestion des risques avant négociation, la livraison de données de marché, etc. La convergence de l'accélération hardware, de la flexibilité des FPGA et de la mise en réseau à faible temps de latence garantit des performances et un déterminisme élevés dans un large éventail de cas d'utilisation.

L'accélérateur Alveo UL3524 est pris en charge par les flux de développement RTL classiques à l'aide de la Vivado™ Design Suite. Des designs de référence pour évaluer le temps de latence et les performances, ainsi que pour tester d'autres fonctionnalités de la carte, sont disponibles dans le référentiel GitHub.

Une licence spéciale est requise pour activer l'appareil Virtex™ UltraScale+ cible. Les développeurs peuvent demander l'accès au site sécurisé Alveo UL3524 pour obtenir des licences et accéder à de la documentation technique supplémentaire.

La carte d'accélération Alveo UL3524 peut être déployée sur des serveurs 1U, 2U et 4U, ce qui permet une grande flexibilité pour répondre aux exigences diverses en matière de racks de serveurs et de formats.

Le serveur haute fréquence 1U Hypertec Orion HF X410R-G6 est désormais disponible, avec un système de refroidissement personnalisé pour la carte d'accélération Alveo UL3524. Contactez-nous pour plus d'informations.

Adoptez dès aujourd'hui la carte d'accélération Alveo UL3524. Disponible dès maintenant auprès d'AMD et des distributeurs agréés.

La carte Alveo™ UL3524 est basée sur le FPGA Virtex UltraScale+™ spécialement conçu pour le trading électronique. Cet appareil est doté d'une architecture de transceiver révolutionnaire qui permet d'atteindre un temps de latence inférieur à 3 ns pour une exécution des transactions de classe mondiale, offrant des performances jusqu'à 7 fois supérieures à celles de la technologie FPGA précédente.

La carte d'accélération FGPA Alveo UL3524 associe une mise en réseau à très faible temps de latence et une adaptabilité hardware pour accélérer les stratégies de trading au niveau des nanosecondes.

Abonnez-vous pour recevoir les dernières actualités sur les centres de données ou contactez un représentant commercial AMD.

1. Tests réalisés par AMD Performance Labs le 16/08/2023 sur la carte d'accélération Alveo UL3524, à l'aide de Vivado Design Suite 2023.1 et exécutés sur Vivado Lab (Hardware Manager) 2023.1. Basé sur le design de benchmark de temps de latence configuré pour activer les transceivers GTF en mode bouclage à proximité interne. Les horloges GTF TX et RX fonctionnent à la même fréquence d'environ 644 MHz avec un décalage de phase de 180 degrés. Le design de benchmark de temps de latence mesure le temps de latence du hardware en verrouillant la valeur d'un seul compteur à fonctionnement libre. Le temps de latence est mesuré comme la différence entre le moment où les données TX sont verrouillées au niveau du transceiver GTF et le moment où les données TX sont verrouillées au niveau du récepteur GTF avant d'être réacheminées vers la structure FPGA. La mesure du temps de latence n'inclut pas le temps système du protocole, le tramage du protocole, le temps de latence de la logique programmable (PL), le temps de configuration de l'interface PL TX, le temps de sortie de l'horloge de l'interface PL RX, le temps de transfert du paquet et les autres sources de latence. Le test de benchmark a été effectué 1 000 fois avec 250 trames par test. Le résultat de mesure cité est basé sur le « mode RAW » du transceiver GTF, où le PCS (raccordement au support physique) du transceiver transmet les données « en l'état » à la structure FPGA. La mesure de la latence est cohérente dans toutes les exécutions de test pour cette configuration. Les résultats peuvent varier en fonction des configurations créées par les fabricants de systèmes. ALV-10

2. D'après la comparaison de simulation entre les transceivers GTY de Virtex UltraScale+ et les transceivers GTF à ultra-faible latence