ULL 演算法交易

從複雜的演算法交易到造市服務

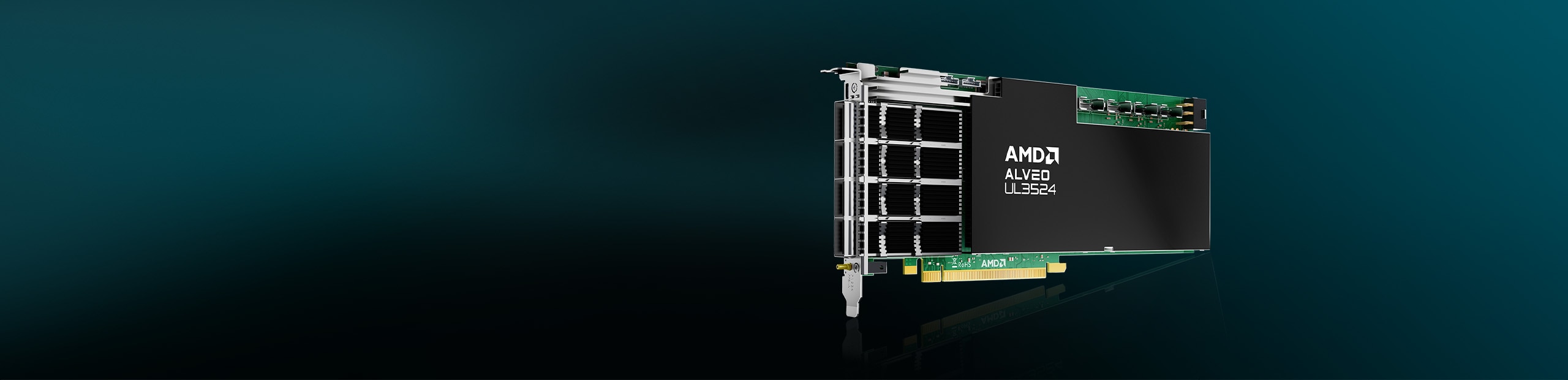

全新 AMD Alveo™ UL3524 提供超低延遲交易效能

低於 3 ns 的收發器延遲1,可實現高效能且決定性的交易執行

開發人員可透過傳統 FPGA 設計及開放原始碼 PyTorch 開發流程,將低延遲 AI 模型整合至交易系統

為演算法交易、交易前風險分析和市場資料傳輸實現硬體加速

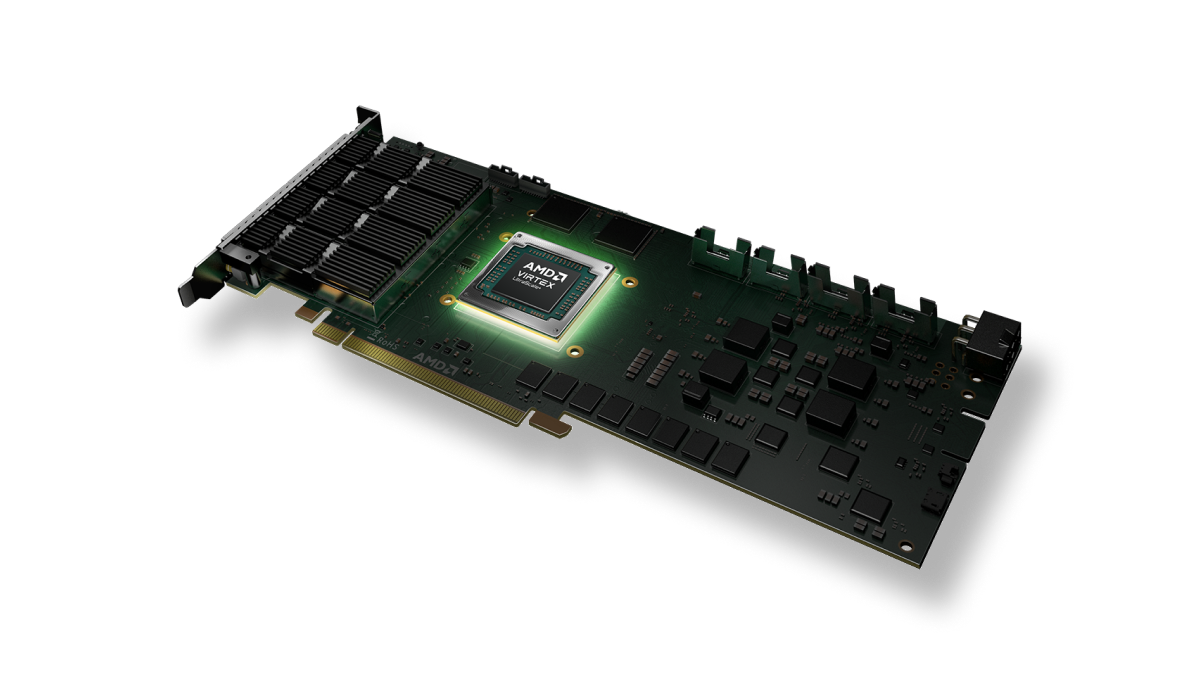

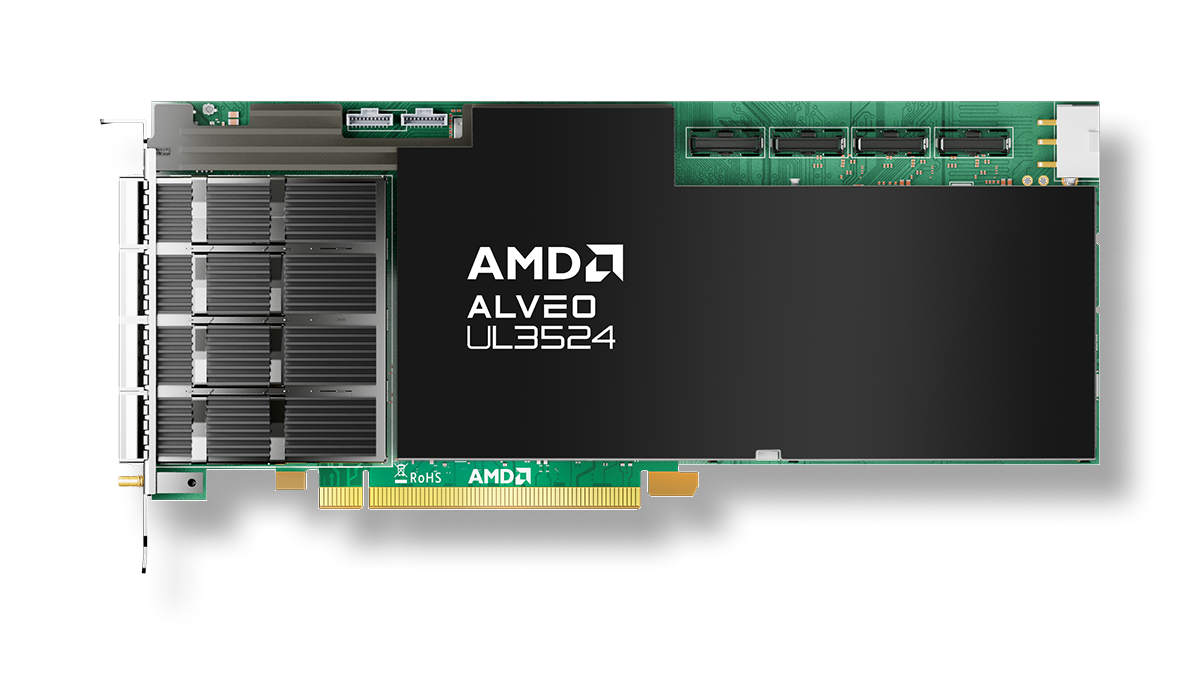

AMD Alveo™ UL3524 採用專為電子交易打造的全新 Virtex UltraScale+™ FPGA。此器件使用能帶來效能突破的收發器架構,可實現低於 3ns 的出色延遲表現1,相較於上一代的 FPGA 技術,效能表現提升達 7 倍2,是世界級的交易執行利器。

Alveo UL3524 加速卡擁有 64 個超低延遲收發器、LUT 78 萬的 FPGA 網狀架構以及 1,680 個運算 DSP slice,專為提升硬體內的自訂交易演算法速度而打造,讓交易員能因應不停進化的策略與市場狀況來調整設計。

Vivado™ Design Suite 支援 Alveo UL3524 加速卡的傳統 FPGA 流程。AMD 亦為開發人員提供開放原始碼且獲社群支援的 FINN 開發框架,使低延遲 AI 模型能夠部署至高效能交易系統。

專為超低延遲 (ULL) 演算法交易打造的 Alveo UL3524 加速器,適合用於交易前風險管理和市場資料傳輸等服務,是自營交易商、對沖基金、造市商、經紀商和資料廠商的理想部署選擇。結合硬體加速、現場可程式化閘陣列彈性與低延遲網路等優勢,可確保在各種使用案例中都能提供卓越的效能與確定性。

使用 Vivado™ Design Suite 可為 Alveo UL3524 加速器提供傳統 RTL 開發流程支援。GitHub 儲存庫提供用於評估延遲與效能,及測試其他加速卡功能的參考設計。

要啟用目標 Virtex UltraScale+ 器件,需取得特殊授權。開發人員可要求存取 Alveo UL3524 安全網站以取得授權,並存取其他技術文件。

Alveo UL3524 加速卡可部署於 1U、2U 和 4U 伺服器之中,靈活適應各種伺服器機架與外型規格需求。

1U Hypertec Orion HF X410R-G6 高頻率伺服器現已上市,配備專為 Alveo UL3524 加速卡客製的冷卻系統。請聯絡我們以瞭解更多資訊。

現在就開始使用 Alveo UL3524 加速器卡。現可向 AMD 與授權經銷商購買。

Alveo™ UL3524 採用專為電子交易打造的全新 Virtex UltraScale+™ FPGA。此器件使用能帶來效能突破的收發器架構,可實現低於 3ns 的出色延遲表現,相較於上一代的 FPGA 技術,效能表現提升達 7 倍,是世界級的交易執行利器。

Alveo UL3524 FPGA 加速卡結合超低延遲網路與自行調適硬體,以奈秒級速度加速執行交易策略。

註冊以接收最新資料中心消息,或是聯絡 AMD 銷售代表。

1.截至 2023 年 8 月 16 日,AMD 效能實驗室對 Alveo UL3524 加速卡進行的測試,使用 Vivado Design Suite 2023.1,在 Vivado Lab (Hardware Manager) 2023.1 上執行。以 GTF Latency Benchmark Design 為基礎,並透過設定將 GTF 收發器修改成內部近端環回模式。GTF TX 和 RX 時脈以約 644MHz 的相同頻率運作,且有 180 度的相位偏移。GTF Latency Benchmark Design 透過閂鎖單一自由運行計數器的值,在硬體中測量延遲。延遲的測量方式為比較 GTF 收發器閂鎖 TX 資料的時間點與 GTF 接收器在回傳至 FPGA 架構前閂鎖 TX 資料的時間點兩者之間的差距。延遲之測量,並未納入通訊協定負擔、通訊協定訊框化、可程式化邏輯 (PL) 延遲、TX PL 介面設定時間、RX PL 介面時脈至輸出時間、封包飛行時間和其他延遲來源。基準測試執行了 1,000 次,每次測試均有 250 個訊框。文中引用的測量結果是以 GTF 收發器的「RAW 模式」為基礎,在此模式下,收發器的 PCS(實體媒體附接層)會將資料「依原貌」傳送至 FPGA 網狀架構。此組態的每一次測試執行,都呈現出一致的延遲測量值。系統製造商可能改變配置,而產生不同的結果。ALV-10

2.根據 Virtex UltraScale+ GTY 收發器與超低延遲 GTF 收發器之間的模擬比較。