ULL 알고리즘 트레이딩

복잡한 알고리즘 트레이딩에서 시장 형성 서비스까지

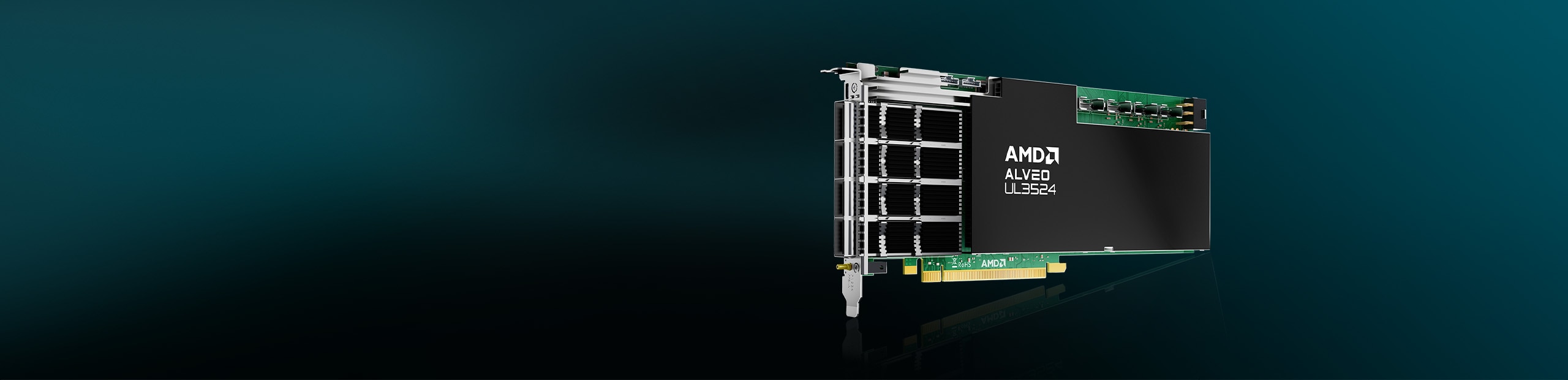

초저지연율 거래를 위한 새로운 AMD Alveo™ UL3524

3ns 미만의 트랜시버 지연율1로 결정론적인 고성능 거래 실행 가능

개발자는 기존 FPGA 설계 및 오픈 소스 PyTorch 개발 흐름을 사용하여 낮은 지연율의 AI 모델을 거래 시스템에 통합 가능

알고리즘 트레이딩, 거래 전 위험 분석 및 시장 데이터 전달을 위한 하드웨어 가속화

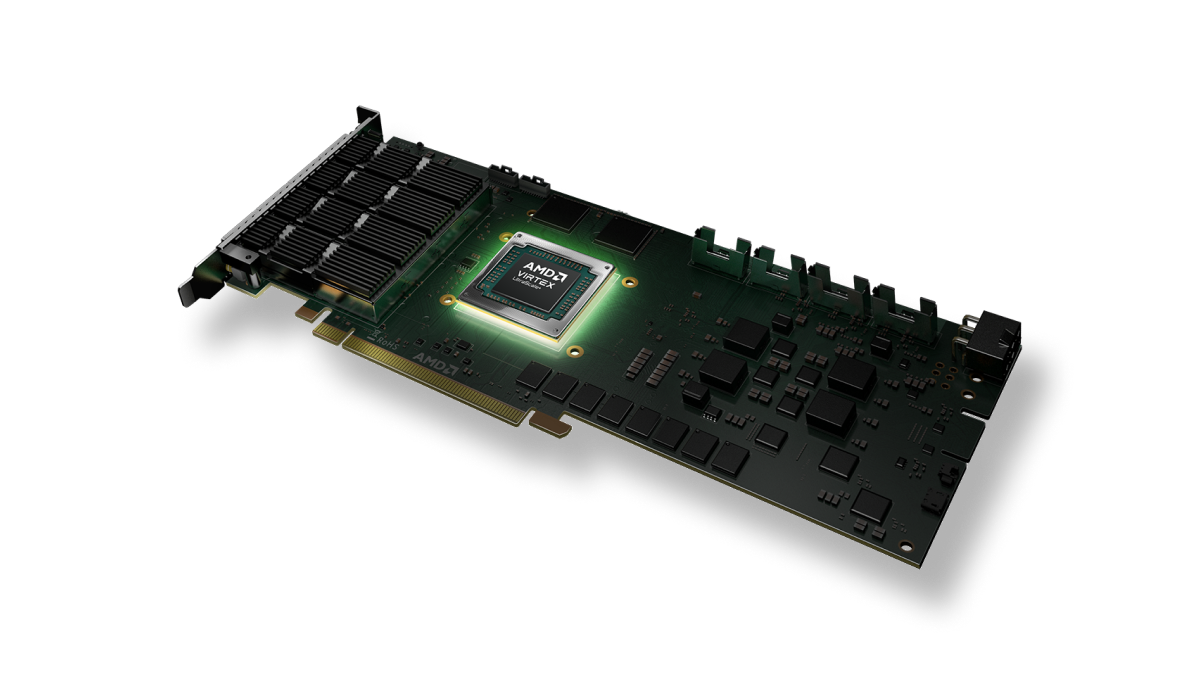

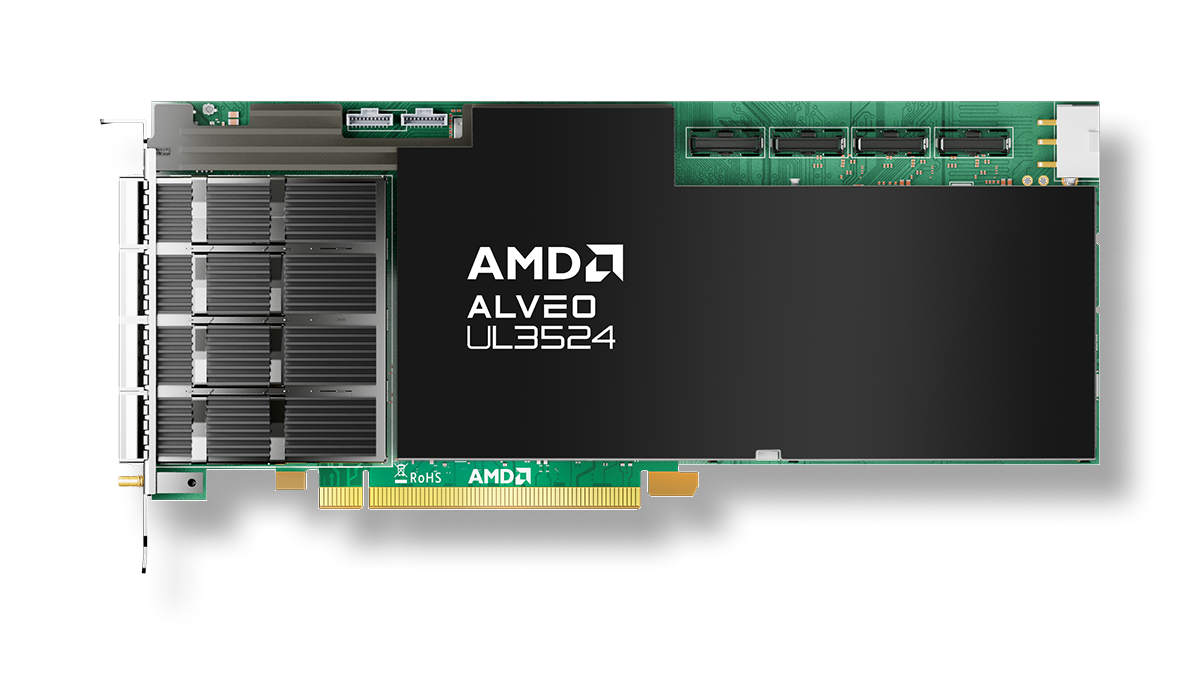

AMD Alveo™ UL3524는 전자 거래를 위해 제작된 새로운 Virtex UltraScale+™ FPGA에 기반합니다. 이 디바이스는 획기적인 트랜시버 아키텍처를 갖추고 있어 세계적 수준의 거래 실행1을 위해 3ns 미만의 지연율을 달성하고, 기존 FPGA 기술에 비해 7배 더 뛰어난 성능을 제공합니다2.

64개의 초저지연율 트랜시버, 780K LUT의 FPGA 패브릭과 1,680개의 DSP 컴퓨팅 슬라이스를 지원하는 Alveo UL3524 가속기 카드는 하드웨어의 맞춤형 트레이딩 알고리즘을 가속화하도록 제작되었으며, 트레이더는 변화하는 전략과 시장 상황에 맞게 설계를 조정할 수 있습니다.

Alveo UL3524 가속기 카드는 기존 FPGA 흐름을 위해 Vivado™ Design Suite가 지원합니다. AMD는 또한 개발자들에게 오픈 소스 및 커뮤니티 지원 FINN 개발 프레임워크를제공하여 저지연율 AI 모델을 고성능 트레이딩 시스템에 배포할 수 있도록 합니다.

프롭 트레이딩 회사, 헤지 펀드, 시장 조성자, 중개업체 및 데이터 공급업체는 ULL 알고리즘 트레이딩을 위한 Alveo UL3524 가속기를 배포하여 거래 전 위험 관리, 시장 데이터 제공 등을 지원할 수 있습니다. 하드웨어 가속, FPGA 유연성, 저지연율 네트워킹의 융합으로 다양한 사용 사례에서 높은 성능과 결정성이 보장됩니다.

Alveo UL3524 가속기는 Vivado™ Design Suite를 사용하는 기존의 RTL 개발 흐름이 지원합니다. 지연율과 성능을 평가하고 카드의 다른 기능을 테스트할 수 있는 참조 설계는 GitHub 리포지토리에서제공됩니다.

대상 Virtex™ UltraScale+ 디바이스를 사용하려면 특별 라이선스가 필요합니다. 개발자는 라이선싱을 위해 Alveo UL3524 Secure Site에 대한 액세스 권한을 요청하고 추가 기술 문서에 액세스할 수 있습니다.

Alveo UL3524 가속기 카드는 1U, 2U 및 4U 서버에 배포할 수 있으며 다양한 서버 랙 및 폼 팩터 요구 사항에 유연하게 대응할 수 있습니다.

1U Hypertec Orion HF X410R-G6 고주파수 서버가 출시되었으며, Alveo UL3524 가속기 카드용 맞춤형 냉각 시스템을 갖추고 있습니다. 자세한 내용은 AMD에 문의하세요.

지금 바로 Alveo UL3524 가속기 카드를 사용해 보세요. AMD 및 공인 대리점에서 구매할 수 있습니다.

Alveo™ UL3524는 전자 거래를 위해 제작된 새로운 Virtex UltraScale+™ FPGA에 기반합니다. 이 디바이스는 획기적인 트랜시버 아키텍처를 갖추고 있어 세계 최고 수준의 거래 실행을 위해 3ns 미만의 지연율을 달성하고, 이전 FPGA 기술에 비해 7배 더 뛰어난 성능을 제공합니다.

Alveo UL3524 FPGA 가속기 카드는 초저지연율 네트워킹과 적응형 하드웨어를 결합하여 트레이딩 전략을 나노초 단위의 속도로 가속화합니다.

등록하여 최신 데이터 센터 소식을 받아보거나 AMD 영업 담당자와 상담하세요.

1. 테스트는 2023년 8월 16일 AMD 퍼포먼스 랩이 Alveo UL3524 가속기 카드를 대상으로 Vivado Design Suite 2023.1을 사용하고 Vivado Lab(Hardware Manager) 2023.1에서 실행하여 수행했습니다. 내부 니어엔드 루프백 모드에서 GTF 트랜시버를 사용하도록 구성된 GTF 지연율 벤치마크 설계를 기반으로 합니다. GTF TX 및 RX 클럭은 180도 위상 이동으로 약 644MHz의 동일한 주파수에서 작동합니다. GTF Latency Benchmark Design은 단일 자유 실행 카운터의 래칭 값을 통해 하드웨어의 지연율을 측정합니다. 지연율은 TX 데이터가 GTF 트랜시버에서 래치되는 시점과 FPGA 패브릭으로 다시 라우팅되기 전에 GTF 수신기에서 TX 데이터가 래치되는 시점의 차이로 측정됩니다. 지연율 측정에는 프로토콜 오버헤드, 프로토콜 프레이밍, 프로그래밍 가능 로직(PL) 지연율, TX PL 인터페이스 설정 시간, RX PL 인터페이스 클럭-투-아웃, 패키지 플라이트 타임 및 기타 지연율 소스가 포함되지 않습니다. 벤치마크 테스트는 테스트당 250개 프레임으로 1,000회 실행되었습니다. 인용된 측정 결과는 GTF 트랜시버 "RAW 모드"를 기준으로 하며, 여기서 트랜시버의 PCS(물리적 매체 연결)는 데이터를 '있는 그대로' FPGA 패브릭으로 전달합니다. 지연율 측정은 이 구성의 모든 테스트 실행에서 일관성을 유지합니다. 시스템 제조업체별 구성에 따라 다른 결과가 나올 수 있습니다. ALV-10

2. Virtex UltraScale+ GTY 트랜시버와 초저지연율 GTF 트랜시버의 시뮬레이션 비교를 기준으로 합니다.