-

Características principales

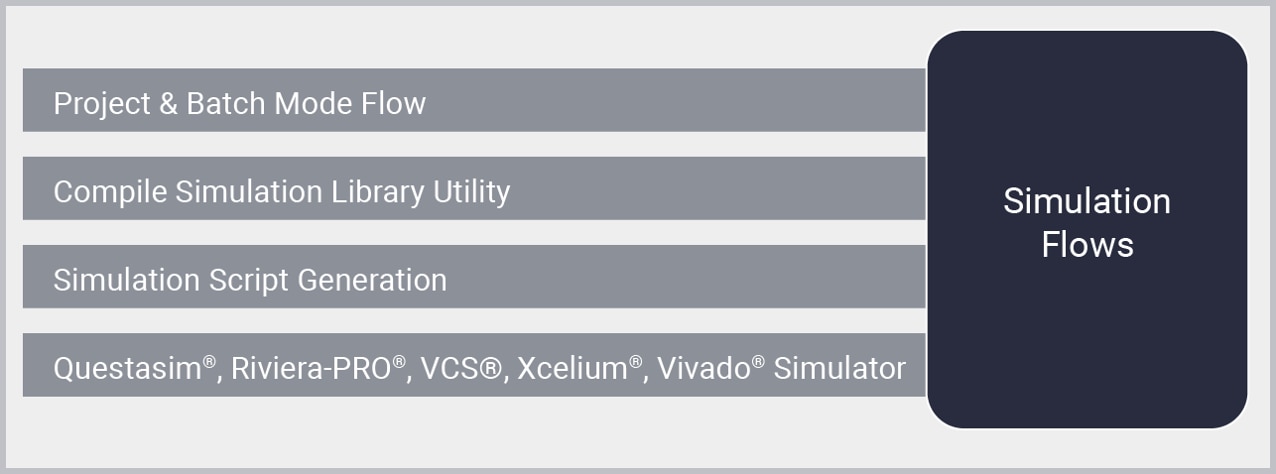

- Funciones de simulación

- Los flujos de simulación proporcionan la capacidad de compilar bibliotecas de simulación para los simuladores compatibles en el entorno del usuario a fin de permitir la reutilización de las bibliotecas compiladas.

- Capacidad para simular y verificar la integridad del diseño en diferentes etapas del proceso de diseño, como la simulación de comportamiento y la simulación funcional y de temporización posterior a la síntesis y posterior a la implementación.

- Integración de simulación unificada utilizando un proceso constante de tres pasos (compilar, elaborar y simular) para todos los simuladores

- Generación de scripts de simulación para simuladores empresariales de terceros que permitan la verificación utilizando entornos propios de los usuarios.

Descripción general

La verificación y la depuración del hardware son fundamentales para garantizar la funcionalidad, el rendimiento y la confiabilidad de la implementación final de la FPGA. Las funciones de verificación Vivado permiten una validación eficiente de la funcionalidad de diseño, mientras que sus funciones de depuración integrales permiten a los ingenieros localizar y resolver problemas de manera eficiente dentro de diseños complejos de FPGA.

Características

- Simulación lógica

- IP de verificación

Flujo de simulación

AMD Vivado™ Design Suite ofrece una variedad de funcionalidades de entrada de diseño, análisis de temporización, depuración de hardware y simulación, todo incluido en un único IDE (Integrated Design Environment, entorno de diseño integrado) de última generación. Este flujo satisface las necesidades de verificación integradas y empresariales para todos los simuladores compatibles.

Vivado permite simulaciones de comportamiento, posteriores a la síntesis y posteriores a la implementación (funcional o temporizador) para el simulador Vivado totalmente integrado y los simuladores de HDL de terceros. El tiempo dedicado a la simulación al comienzo del ciclo de diseño ayuda a identificar los problemas de forma temprana y reduce significativamente los tiempos de respuesta en comparación con las etapas posteriores del flujo.

Para mejorar la flexibilidad en los entornos de verificación de usuarios, Vivado ofrece compatibilidad para un entorno integrado y proporciona scripts a fin de usarlos con configuraciones de verificación externas.

El IDE de Vivado admite los principales simuladores en modo integrado para usuarios de simulación interactiva y modo de script para ingenieros de verificación avanzada.

Aldec Active-HDL® y Riviera-PRO®, Cadence Xcelium® Simulator, Siemens EDA ModelSim® y Questasim®, Synopsys VCS® y simulador Vivado de AMD

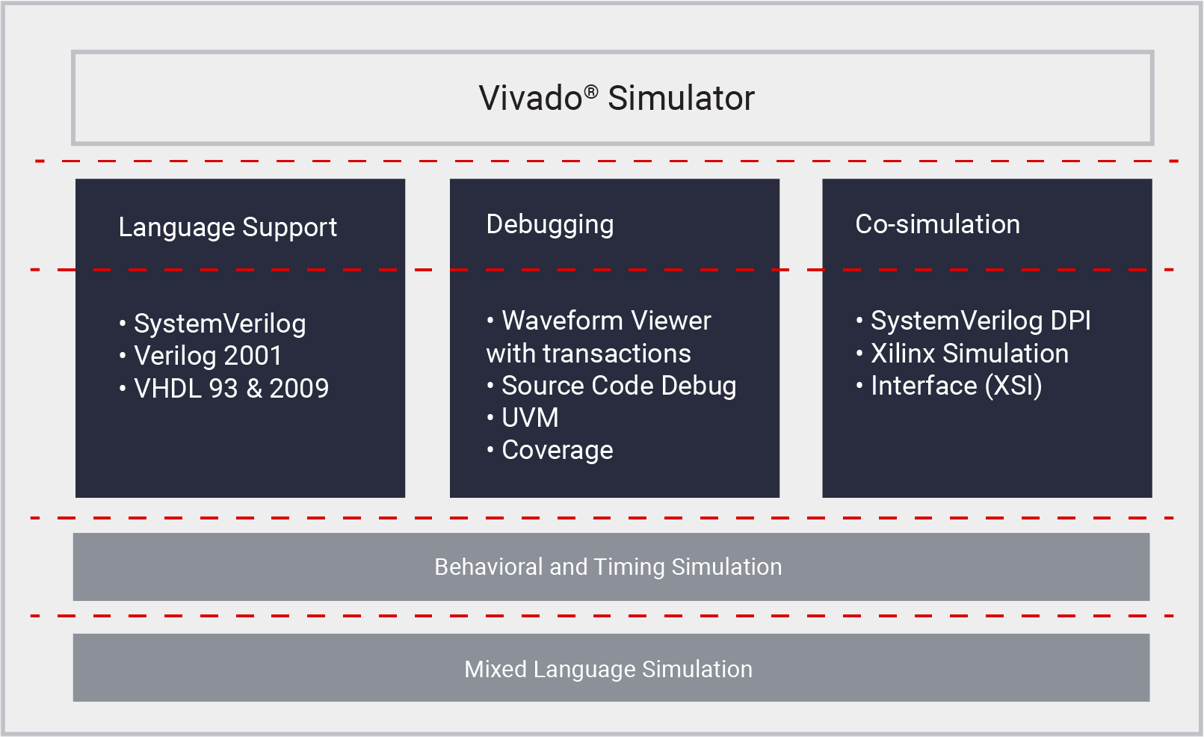

Simulador de Vivado

El simulador de Vivado™ es un simulador de lenguaje mixto y numerosas funciones que admite los lenguajes Verilog, SystemVerilog y VHDL. El simulador de Vivado es parte de Vivado y está disponible sin costo adicional. No tiene limitación de tamaño de diseño, instancias o línea y permite ejecutar instancias ilimitadas de simulación en lenguaje mixto mediante una única licencia Vivado.

El simulador de Vivado admite sistemas operativos Windows® y Linux® con potentes funciones de depuración que están destinadas a satisfacer las necesidades de verificación de los clientes de AMD.

El simulador de Vivado es un simulador basado en eventos de HDL (Hardware Description Language, lenguaje de descripción de hardware) que admite simulación de comportamiento y temporización para diseños de lenguaje único y lenguaje mixto.

-

Características principales

- Compatibilidad de lenguajes

- SystemVerilog (incluye aleatorización de restricciones y cobertura funcional)

- Verilog 2001

- VHDL 93 y VHDL 2008

- Depuración y verificación

- Visor de formas de onda avanzado que admite la vista de forma de onda y transacción digital/analógica

- Herramientas integrales de depuración como puntos de interrupción, depuración de subprogramas y cross-probing (sondeo cruzado)

- Compatibilidad para la biblioteca UVM 1.2

- Cobertura funcional

- Compatibilidad para GUI y modo de script

- Cosimulación

- Interfaz de programación directa (DPI)

- Interfaz de simulación Xilinx (XSI)

IP de verificación

La cartera de VIP (Verification IP, IP de verificación) de AMD ofrece a los usuarios la capacidad de verificar y depurar sus diseños en un entorno de simulación de forma fácil, rápida y más eficaz. Los núcleos de IP de verificación son modelos de verificación diseñados específicamente cuyo objetivo es garantizar la interoperabilidad y el comportamiento correctos del sistema. Las empresas del sector de la EDA (Electronic Design Automation, automatización de diseño electrónico) desarrollan VIP para interfaces basadas en estándares (AXI, PCIe, SAS, SATA, USB, HDMI, ENET, etc.). Las ventajas de usar VIP incluyen una mejor calidad de diseño y una reducción del tiempo de programación debido a la reutilización.

Los núcleos VIP de AMD son modelos de simulación basados en SystemVerilog que proporcionan una comprobación completa del protocolo AXI con aserciones con licencia ARM, admiten todos los simuladores principales y están incluidos en Vivado sin costo alguno. AMD ofrece VIP para su uso en diseños de nivel de componente AXI (AXI-MM, AXI_Stream) y que utilizan sistemas de procesamiento (Zynq™ 7000).

-

Características principales

- Generador de tráfico

Generador de tráfico AXI para AXI4, AXI4-Stream, AXI4-Lite

- VIP AXI y VIP AXI Stream

Compatibilidad total con AXI y AXI Stream Protocol Checker

- VIP de Zynq 7000 y VIP de MPSoC Zynq UltraScale+™

Compatibilidad con la simulación funcional para la aplicación basada en Zynq 7000 y MPSoC Zynq UltraScale+

- VIP de CIPS (Control, Interface, and Processing System; control, interfaz y sistema de procesamiento) Versal™

Compatibilidad de simulación funcional de IP de control, interfaz y sistema de procesamiento (CIPS)