-

Principais recursos

- Recursos de simulação

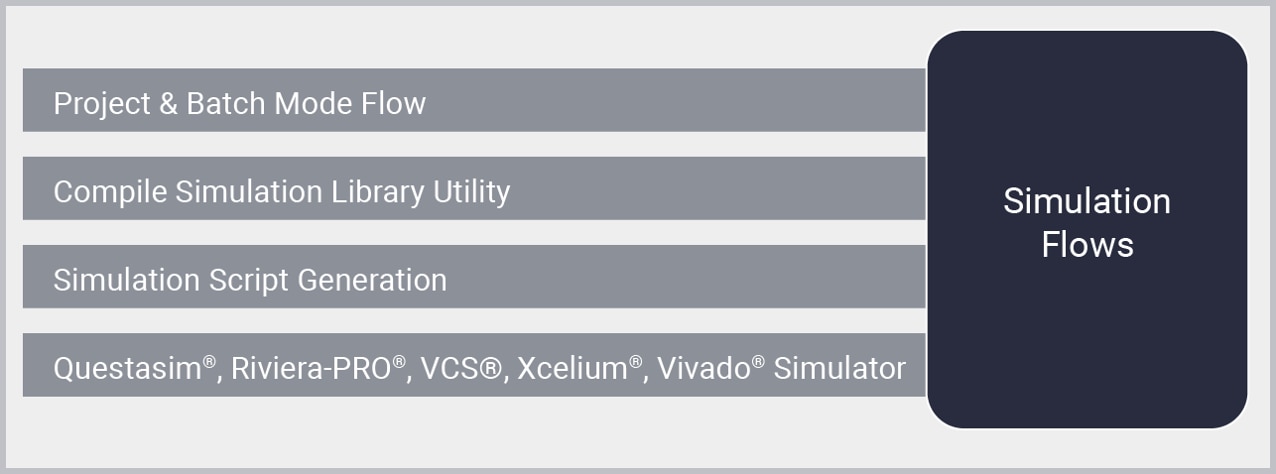

- Os fluxos de simulação permitem compilar bibliotecas de simulação para os simuladores compatíveis no ambiente dos usuários, possibilitando a reutilização das bibliotecas compiladas.

- Capacidade de simular e verificar a integridade do projeto em diferentes estágios do processo de projeto, como simulação comportamental, funcional pós-síntese e de tempo e simulação funcional e de tempo pós-implementação.

- Integração de simulação unificada usando um processo consistente de 3 etapas (compilar, elaborar, simular) para todos os simuladores

- Geração de script de simulação para simuladores empresariais terceirizados para possibilitar a verificação usando próprios ambientes de usuários.

Visão geral

A verificação e a depuração de hardware são essenciais para garantir a funcionalidade, o desempenho e a confiabilidade da implementação final da FPGA. Os recursos de verificação do Vivado possibilitam a validação eficiente da funcionalidade do projeto, enquanto seus recursos abrangentes de depuração permitem aos engenheiros localizar e resolver com eficiência os problemas em projetos complexos de FPGA.

Recursos

- Simulação lógica

- Verification IP

Fluxo de simulação

O AMD Vivado™ Design Suite fornece uma variedade de capacidades de entrada de projeto, análise de tempo, depuração de hardware e simulação, todas englobadas em um único ambiente de projeto integrado (IDE) de última geração. Este fluxo possibilita as necessidades de verificação integrada e empresarial para todos os simuladores compatíveis.

O Vivado possibilita simulações comportamentais, pós-síntese e pós-implementação (funcionais ou de tempo) para o Vivado Simulator totalmente integrado e simuladores HDL terceirizados. O tempo gasto na simulação no início do ciclo de projeto ajuda a identificar problemas antecipadamente e reduz significativamente os tempos de resposta em comparação com os estágios posteriores do fluxo.

Para auxiliar a flexibilidade em ambientes de verificação de usuário, o Vivado fornece suporte para um ambiente integrado, bem como scripts para uso com configurações de verificação externa.

O Vivado IDE é compatível com todos os principais simuladores no modo integrado para usuários de simulação interativa e no modo de script para engenheiros de verificação avançada.

Aldec — Active-HDL® e Riviera-PRO®, Cadence Xcelium® Simulator, Siemens EDA — ModelSim® e Questasim®, Synopsys VCS® e AMD Vivado Simulator

Vivado Simulator

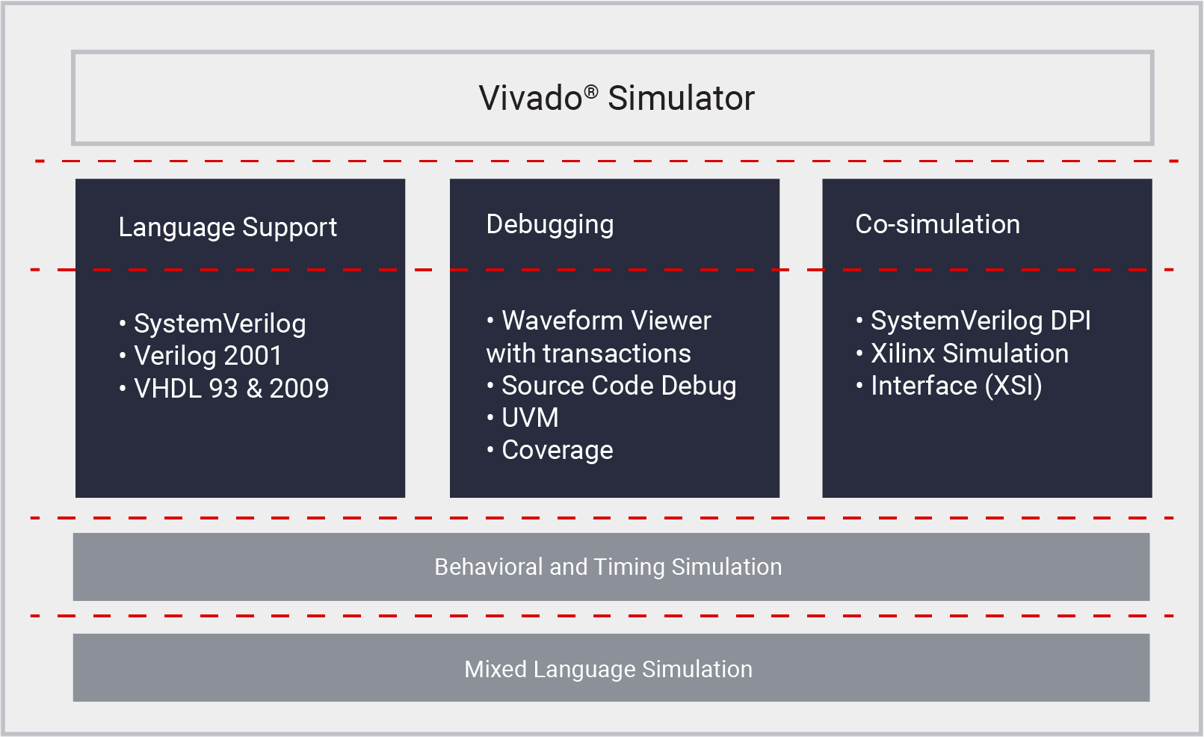

O Vivado™ Simulator é um simulador de linguagem mista rico em recursos que é compatível com a linguagem Verilog, SystemVerilog e VHDL. O Vivado Simulator está incluído como parte do Vivado e está disponível sem custo adicional. Ele não tem um tamanho de projeto, instâncias ou limitação de linha e permite executar instâncias ilimitadas de simulação de linguagem mista usando uma única licença do Vivado.

O Vivado Simulator é compatível com os sistemas operacionais Windows® e Linux® com poderosos recursos de depuração que visam atender às necessidades de verificação dos clientes AMD.

O Vivado Simulator é um simulador de linguagem de descrição de hardware (HDL) orientado a eventos compatível com simulação comportamental e de tempo para projetos de linguagem única e de linguagem mista.

-

Principais recursos

- Suporte a linguagens

- SystemVerilog (incluindo randomização de restrições e cobertura funcional)

- Verilog 2001

- VHDL 93 e VHDL 2008

- Depuração e verificação

- Visualizador avançado de forma de onda com suporte a forma de onda digital/analógica e a visualização de transações

- Ferramentas de depuração abrangentes, como pontos de parada, depuração de subprograma e teste cruzado

- Suporte para a biblioteca UVM 1.2

- Cobertura funcional

- Oferece suporte a modo de script e GUI

- Simulação conjunta

- Interface de programação direta (DPI)

- Xilinx simulation interface (XSI)

Verification IP

O portfólio de Verification IP (VIP) da AMD fornece aos usuários a capacidade de verificar e depurar seus projetos em um ambiente de simulação de forma fácil, rápida e eficaz. Os núcleos do Verification IP são modelos de verificação desenvolvidos especificamente, cujo objetivo é garantir a interoperabilidade e o comportamento corretos do sistema. As empresas da indústria de EDA desenvolvem VIP para interfaces baseadas em padrões (AXI, PCIe, SAS, SATA, USB, HDMI, ENET, etc.). As vantagens de usar VIP incluem qualidade de projeto aprimorada e tempo de programação reduzido devido à reutilização.

Os núcleos de VIP da AMD são modelos de simulação baseados em SystemVerilog que fornecem verificação do AXI Protocol Checker com asserções licenciadas ARM, são compatíveis com todos os principais simuladores e estão incluídos no Vivado sem nenhum custo. A AMD fornece VIP para uso em projetos que usam nível de componente AXI (AXI-MM, AXI_Stream) e sistema de processamento (Zynq™ 7000).

-

Principais recursos

- Traffic Generator

O AXI Traffic Generator para AXI4, AXI4-Stream, AXI4-Lite

- VIP AXI e VIP AXI Stream

Suporte completo ao AXI e AXI Stream Protocol Checker

- VIP Zynq 7000 e VIP MPSoC Zynq UltraScale+™

Suporte à simulação funcional para aplicativos baseados em MPSoC Zynq UltraScale+ e Zynq 7000

- VIP do sistema de controle, interfaces e processamento (VIP CIPS) Versal™

Suporte à simulação funcional de IP do sistema de controle, interfaces e processamento (CIPS)