-

主要功能

- 模擬功能

- 模擬流程提供了在使用者環境中,為支援的模擬器編譯模擬程式庫的功能,方面使用者重複使用編譯過的程式庫。

- 能夠在設計過程的不同階段模擬並驗證設計完整性,例如行為模擬、合成後功能模擬和時序模擬,以及實作後功能模擬和時序模擬。

- 統一模擬整合,所有模擬器都使用一致的 3 步驟流程(編譯、演繹、模擬)

- 為企業第三方模擬器生成模擬腳本,以運用使用者自己的環境進行驗證。

概述

驗證和硬體除錯是確保最終 FPGA 實作的功能、效能和可靠性的關鍵。Vivado 的驗證功能可有效驗證設計的功能性,並具備全面的除錯功能,讓工程師能夠提高效率,迅速找出並解決複雜 FPGA 設計中的問題。

功能

- 邏輯模擬

- 驗證 IP

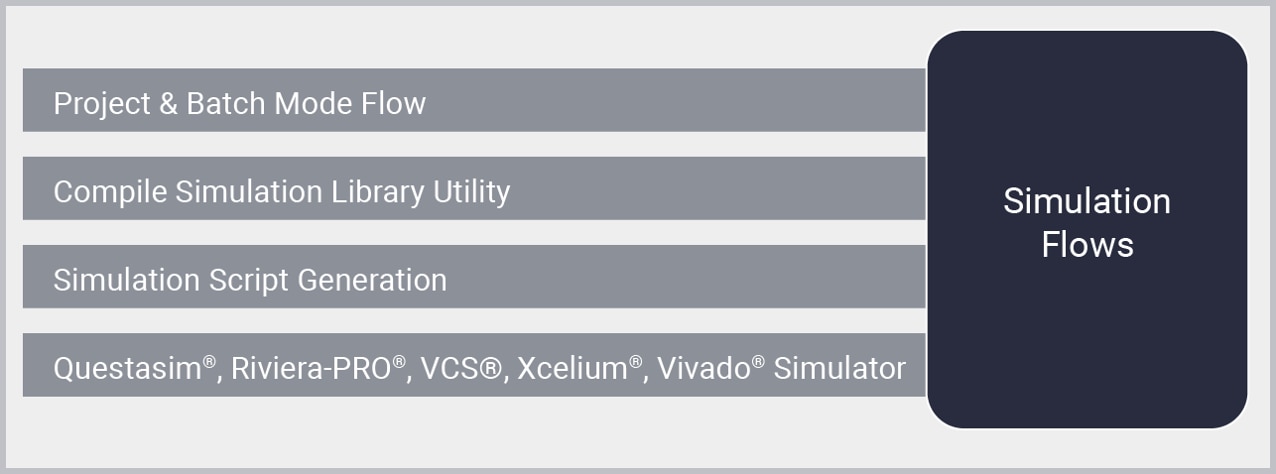

模擬流程

AMD Vivado™ Design Suite 提供一系列的設計輸入、時序分析、硬體除錯和模擬功能,這些所有功能都包含在單一先進的整合式設計環境 (IDE) 中。此流程支援整合式驗證和企業驗證需求,適用於所有受到支援的模擬器。

Vivado 可為完全整合的 Vivado 模擬器和第 3 方硬體描述語言 (Hardware Description Language, HDL) 模擬器,提供行為、合成後和實作後(功能或時序)模擬。在設計週期早期花費在模擬上的時間有助於及早發現問題,與在流程的後期階段才發現相比,可顯著縮短產出時間。

為了提高使用者驗證環境的靈活性,Vivado 既支援整合式環境,也提供可與外部驗證環境搭配使用的腳本 (script)。

Vivado IDE 支援所有主流模擬器,包括互動式模擬使用者慣用的整合模式,以及進階驗證工程師所需要的腳本 (script) 模式。

Aldec - Active-HDL® 與 Riviera-PRO®、Cadence Xcelium® 模擬器、Siemens EDA – ModelSim® 與 Questasim®、Synopsys VCS®,以及 AMD Vivado 模擬器

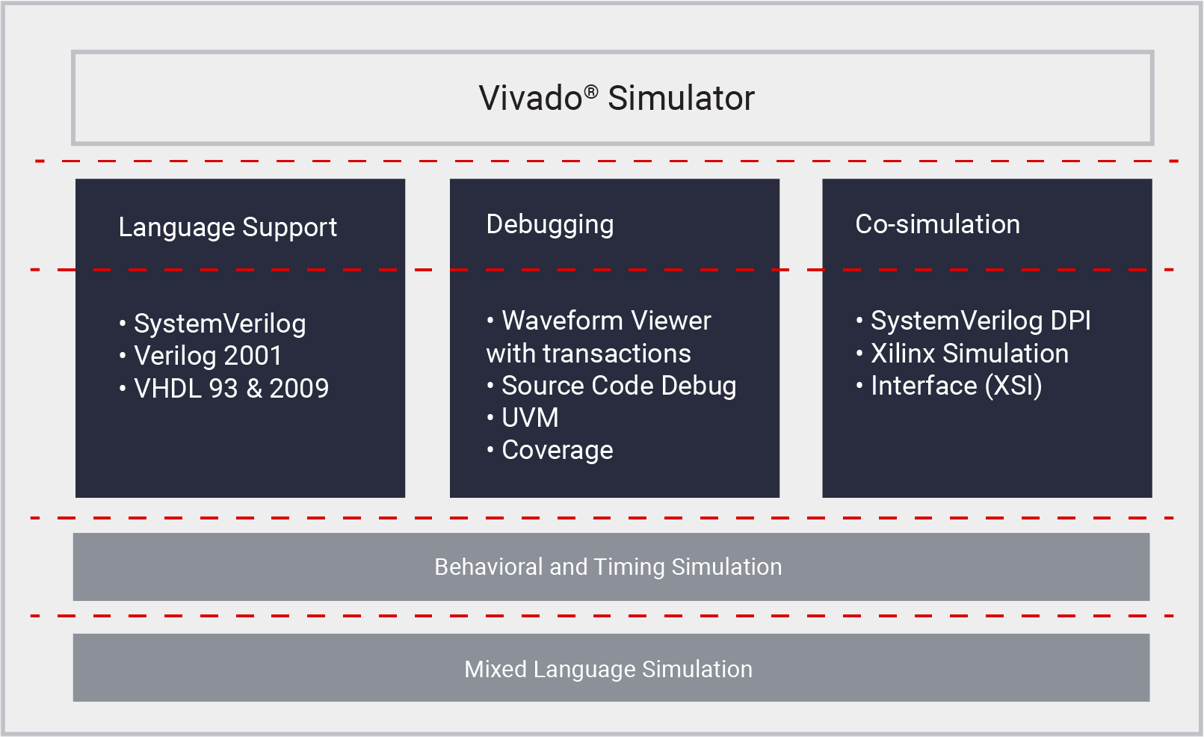

Vivado 模擬器

Vivado™ 模擬器是一款功能豐富的混合語言模擬器,可支援 Verilog、SystemVerilog 和超高速積體電路硬體描述語言 (Very High-Speed Integrated Circuit Hardware Description Language, VHDL)。Vivado 模擬器是 Vivado 的一部分,無須額外付費即可使用。它沒有設計大小、實體或行數的限制,並且允許使用單一 Vivado 授權,執行不限數量的混合語言模擬實體。

Vivado 模擬器支援 Windows® 和 Linux® 作業系統,具有強大的除錯功能,可確實滿足 AMD 客戶的驗證需求。

Vivado 模擬器是一款硬體描述語言 (HDL) 事件驅動型模擬器,支援單一語言和混合語言設計的行為模擬和時序模擬。

-

主要功能

- 語言支援

- SystemVerilog(包括限制隨機化和功能覆蓋率)

- Verilog 2001

- VHDL 93 和 VHDL 2008

- 除錯和驗證

- 支援數位/類比波形和交易視圖的進階波形檢視器

- 全方位的除錯工具,例如中斷點、子程式除錯和交互定位

- 支援 UVM 1.2 程式庫

- 功能覆蓋率

- 同時支援圖形使用者介面 (Graphical User Interface, GUI) 和腳本模式

- 共同模擬

- 直接程式設計介面 (DPI)

- 賽靈思模擬介面 (XSI)

驗證 IP

AMD 的驗證 IP (VIP) 產品組合讓使用者能夠在模擬環境中,輕鬆、快速、高效地驗證設計並加以除錯。驗證 IP 核心是專門建立的驗證模型,其目標是確保正確的互通性和系統行為。電子設計自動化 (Electronic Design Automation, EDA) 產業的公司開發了標準型介面(AXI、PCIe、SAS、SATA、USB、HDMI、ENET 等)適用的 VIP。使用 VIP 的優點包括可重複使用性,進而改善設計品質,並縮短期程。

AMD VIP 核心是以 SystemVerilog 為基礎的模擬模型,透過 ARM 授權的判定,提供完整的 AXI 協定檢查,同時支援所有主要的模擬器並免費隨附在 Vivado 中。AMD 提供的 VIP 可用於使用 AXI 元件層級(AXI-MM、AXI_Stream)和處理系統 (Zynq™ 7000) 設計的設計中。

-

主要功能

- 流量生成器

AXI 流量生成器,適用於 AXI4、AXI4-Stream、AXI4-Lite

- AXI VIP 和 AXI Stream VIP

完整支援 AXI 和 AXI Stream 協定檢查器

- Zynq 7000 VIP 和 Zynq UltraScale+™ MPSoC VIP

針對以 Zynq 7000 和 Zynq UltraScale+ MPSoC 為基礎的應用,提供功能模擬支援

- Versal™ 控制、介面與處理系統 VIP (CIPS VIP)

針對控制、介面與處理系統 (CIPS) IP 提供功能模擬支援