-

主要功能特性

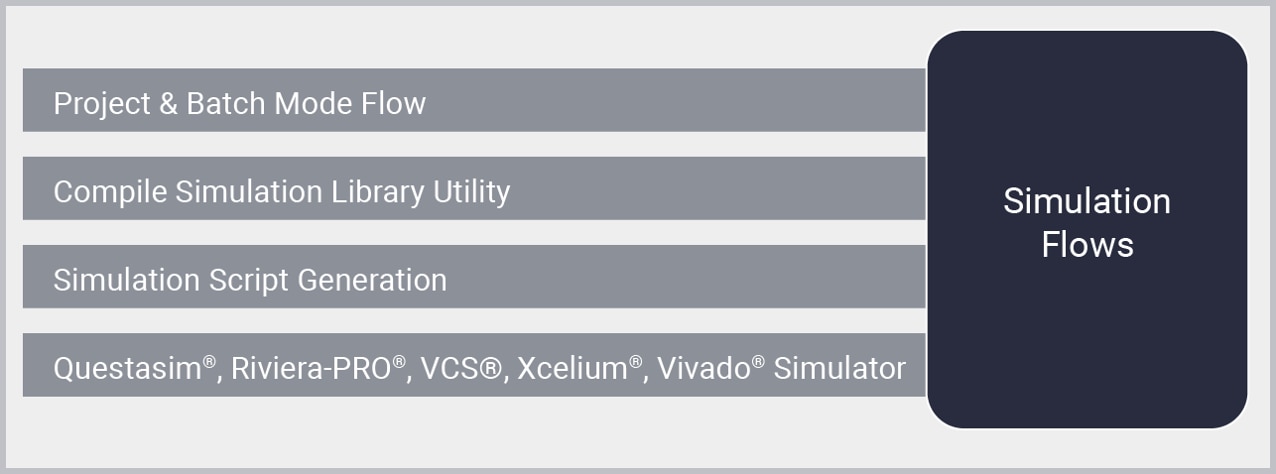

- 仿真功能

- 仿真流程能够在用户环境中为所支持的仿真器编译仿真库,从而实现对编译库的重复使用。

- 能够在设计过程的不同阶段(如行为、综合后功能和时序仿真以及实现后功能及时序仿真)仿真和验证设计完整性。

- 使用一致的 3 步流程(编译、细化、仿真)对所有仿真器进行统一仿真集成

- 为企业级第三方仿真器生成仿真脚本,以便在用户自己的环境中进行验证。

概观

验证和硬件调试对于确保最终 FPGA 实现方案的功能性、性能和可靠性至关重要。Vivado 验证功能支持高效验证设计功能性,借助其综合调试功能,工程师能够高效排查并解决复杂 FPGA 设计中存在的问题。

特性

- 逻辑仿真

- Verification IP

仿真流程

AMD Vivado™ Design Suite 提供一系列设计输入、时序分析、硬件调试和仿真功能,所有这些功能都包含在一个先进的集成设计环境 (IDE) 中。该流程能够满足所有受支持的仿真器的集成验证和企业级验证需求。

Vivado 支持行为仿真、综合后仿真和实现后(功能或定时)仿真,适用于完全集成的 Vivado 仿真器和第三方 HDL 仿真器。与流程的后期阶段相比,在设计周期的早期阶段进行仿真有助于及早发现问题,从而显著缩短周转时间。

为了增强用户验证环境的灵活性,Vivado 不仅提供对集成环境的支持,同时还提供了用于外部验证设置的脚本。

Vivado IDE 支持所有主流仿真器,无论是在集成模式(适用于交互式仿真用户)还是脚本模式(适用于高级验证工程师)下,都没有问题。

Aldec - Active-HDL® 与 Riviera-PRO®、Cadence Xcelium® 仿真器、Siemens EDA – ModelSim® 与 Questasim®、Synopsys VCS® 和 AMD Vivado 仿真器

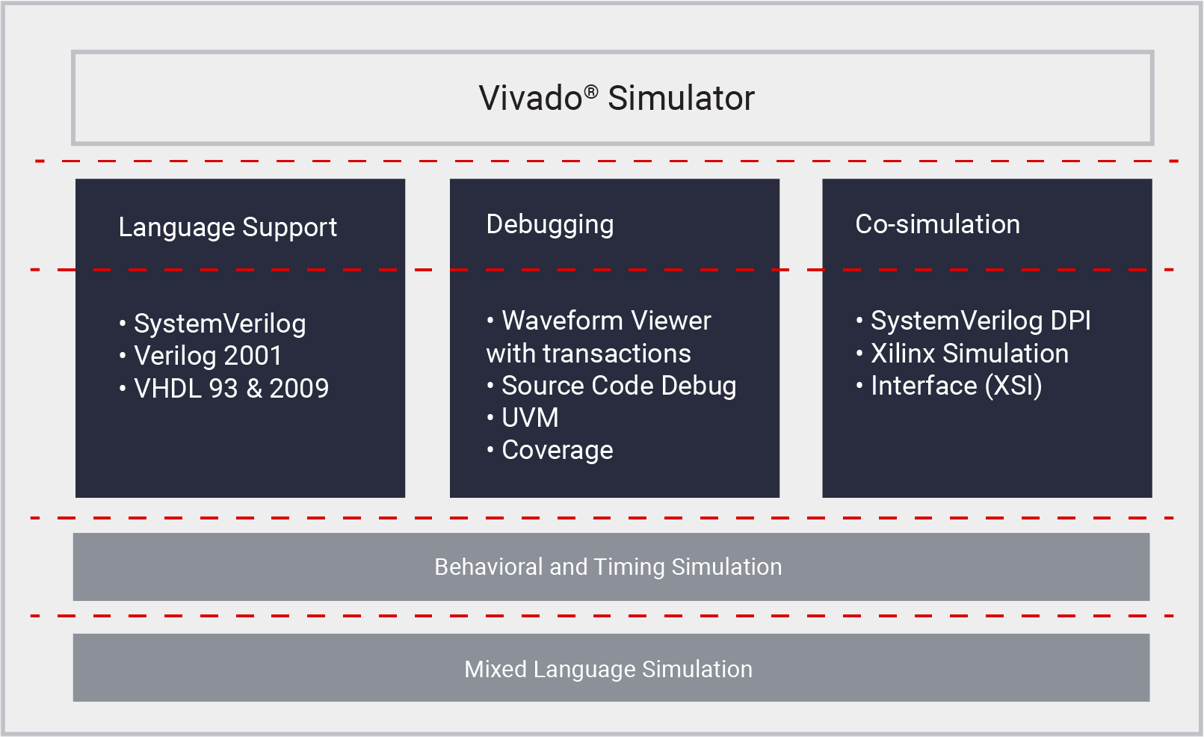

Vivado 仿真器

-

主要功能特性

- 语言支持

- SystemVerilog(包括约束随机化和功能覆盖)

- Verilog 2001

- VHDL 93 和 VHDL 2008

- 调试和验证

- 支持数字/模拟波形和事务视图的高级波形查看器

- 断点、子程序调试和交叉探测等综合调试工具

- 支持 UVM 1.2 库

- 功能覆盖范围

- 支持 GUI 和脚本模式

- 协同仿真

- 直接编程接口 (DPI)

- Xilinx 仿真接口 (XSI)

Verification IP

AMD Verification IP (VIP) 产品系列使用户能够在仿真环境下中更高效便捷地验证和调试其设计。Verification IP 核是一种专门构建的验证模型,旨在确保正确的互操作性和系统行为。EDA 行业的公司为基于标准的接口(AXI、PCIe、SAS、SATA、USB、HDMI、ENET 等)开发 VIP。使用 VIP 的优势包括提升设计质量以及通过重复使用缩短开发周期。

AMD VIP 核是基于 SystemVerilog 的仿真模型,可通过 ARM 许可的断言提供全面的 AXI 协议检查,支持所有主流仿真器,并随 Vivado 免费提供。AMD 提供的 VIP 可用于那些使用 AXI 组件级(AXI-MM、AXI_Stream)和处理系统 (Zynq™ 7000) 的设计。

-

主要功能特性

- Traffic Generator

适用于 AXI4、AXI4-Stream、AXI4-Lite 的 AXI Traffic Generator

- AXI VIP 和 AXI Stream VIP

全面支持 AXI 和 AXI Stream Protocol Checker

- Zynq 7000 VIP 和 Zynq UltraScale+™ MPSoC VIP

对基于 Zynq 7000 和 Zynq UltraScale+ MPSoC 的应用的功能仿真支持

- Versal™ 控制、接口和处理系统 VIP (CIPS VIP)

控制、接口和处理系统 (CIPS) IP 的功能仿真支持