-

Fonctionnalités clés

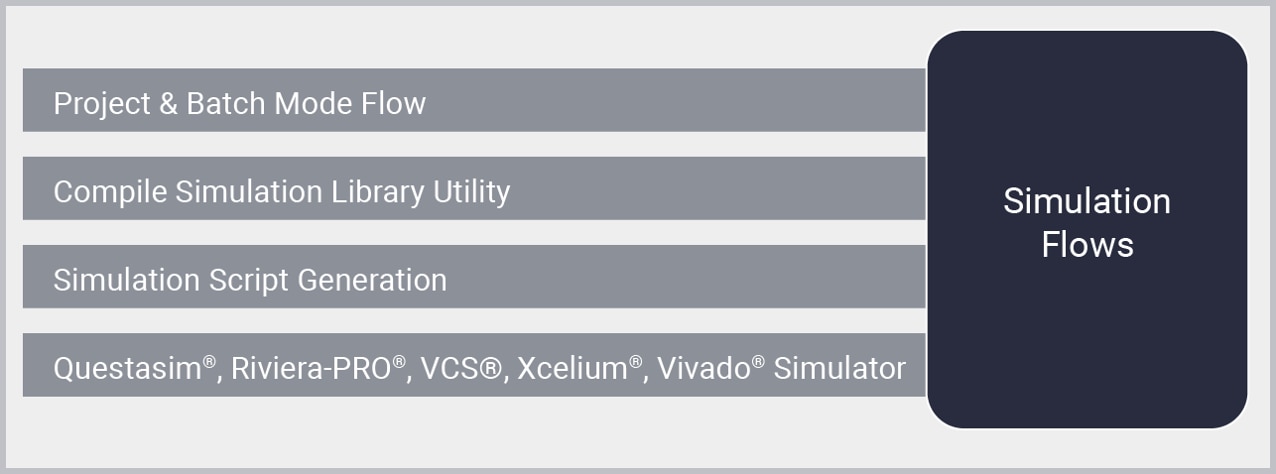

- Fonctionnalités de simulation

- Les flux de simulation permettent de compiler des bibliothèques de simulation pour les simulateurs pris en charge dans l'environnement des utilisateurs, afin de permettre la réutilisation des bibliothèques compilées.

- Possibilité de simuler et de vérifier l'intégrité de la conception à différentes étapes du processus de conception : simulation comportementale, simulation fonctionnelle et temporelle post-synthèse, et simulation fonctionnelle et temporelle post-implémentation.

- Intégration de simulation unifiée utilisant un processus cohérent en trois étapes (compilation, élaboration, simulation) pour tous les simulateurs

- Génération de scripts de simulation pour les simulateurs d'entreprise tiers, afin de permettre la vérification avec les environnements des utilisateurs.

Présentation

La vérification et le débogage hardware sont essentiels pour garantir le fonctionnement, les performances et la fiabilité de l'implémentation FPGA finale. Les fonctions de vérification de Vivado permettent de valider efficacement les fonctionnalités de la conception, et ses fonctions de débogage complètes aident les ingénieurs à localiser et à résoudre efficacement les problèmes dans les conceptions FPGA complexes.

Fonctionnalités

- Simulation logique

- IP de vérification

Flux de simulation

AMD Vivado™ Design Suite offre toute une gamme de fonctionnalités de conception, d'analyse de la synchronisation, de débogage du hardware et de simulation, le tout dans un seul environnement de conception intégré (IDE) de pointe. Ce flux permet de répondre aux besoins de vérification, qu'ils soient intégrés ou propres à l'entreprise, pour tous les simulateurs pris en charge.

Vivado permet d'effectuer des simulations comportementales, post-synthèse et post-implémentation (fonctionnelle ou temporelle) pour le simulateur Vivado entièrement intégré et les simulateurs HDL tiers. La simulation effectuée au début du cycle de conception permet d'identifier les problèmes en amont et réduit considérablement les délais d'exécution dans les étapes ultérieures du flux.

Pour plus de flexibilité dans les environnements de vérification des utilisateurs, Vivado prend en charge un environnement intégré et fournit des scripts à utiliser avec les configurations de vérification externes.

L'IDE Vivado prend en charge tous les principaux simulateurs, en mode intégré pour les utilisateurs de simulation interactive, et en mode script pour les ingénieurs de vérification avancés.

Aldec - Active-HDL® et Riviera-PRO®, Cadence Xcelium® Simulator, Siemens EDA – ModelSim® et Questasim®, Synopsys VCS® et AMD Vivado Simulator

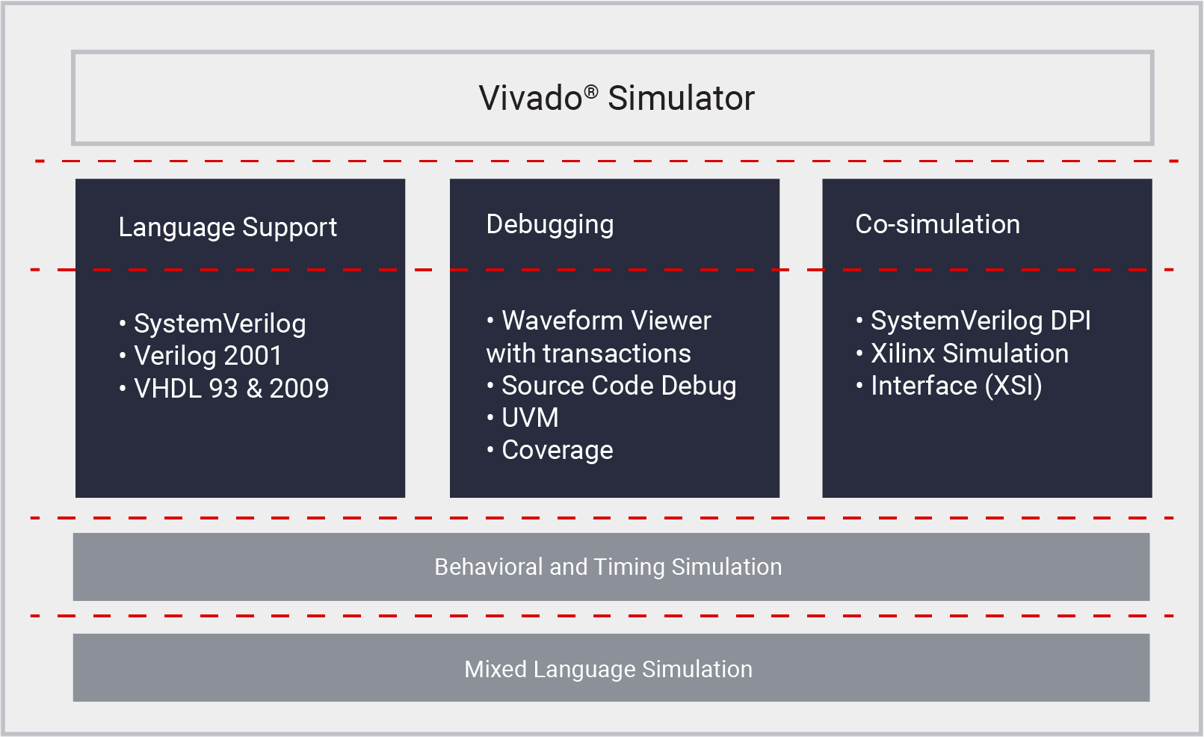

Vivado Simulator

Vivado™ Simulator est un simulateur en langage mixte, riche en fonctionnalités, qui prend en charge Verilog, SystemVerilog et VHDL. Vivado Simulator est inclus dans Vivado et est disponible sans frais supplémentaires. Ne comporte pas de limite de taille de conception, d'instances ou de ligne et permet d'exécuter un nombre illimité d'instances de simulation dans plusieurs langages à l'aide d'une seule licence Vivado.

Vivado Simulator prend en charge les systèmes d'exploitation Windows® et Linux® avec de puissantes fonctionnalités de débogage destinées à répondre aux besoins de vérification des clients AMD.

Vivado Simulator est un simulateur basé sur les événements de langage de description du matériel (HDL) qui prend en charge la simulation comportementale et temporelle pour les conceptions en langage unique et en langage mixte.

-

Fonctionnalités clés

- Prise en charge des langages

- SystemVerilog (y compris randomisation des contraintes et couverture fonctionnelle)

- Verilog 2001

- VHDL 93 et VHDL 2008

- Débogage et vérification

- Visualiseur de forme d'onde avancée prenant en charge les formes d'onde numérique/analogique et la vue de transaction

- Outils de débogage complets, notamment breakpoints, débogage de sous-programme et cross-probing

- Prise en charge de la bibliothèque UVM 1.2

- Protection fonctionnelle

- Prend en charge à la fois le mode GUI et le mode script

- Co-simulation

- Interface de programmation directe (DPI)

- Interface de simulation Xilinx (XSI)

IP de vérification

Le portefeuille d'IP de vérification (VIP) d'AMD permet aux utilisateurs de vérifier et de déboguer leurs conceptions dans un environnement de simulation, de manière simple, rapide et plus efficace. Les cœurs d'IP de vérification sont des modèles de vérification spéciaux dont l'objectif est de garantir l'interopérabilité et le comportement du système. Les entreprises du secteur EDA développent des VIP pour les interfaces basées sur des normes (AXI, PCIe, SAS, SATA, USB, HDMI, ENET, etc.). Les VIP permettent d'améliorer la qualité des conceptions et de réduire le temps de planification grâce à la réutilisation.

Les cœurs VIP d'AMD sont des modèles de simulation basés sur SystemVerilog, inclus dans Vivado sans frais supplémentaires, qui fournissent un contrôle complet du protocole AXI avec des assertions ARM sous licence, prennent en charge tous les principaux simulateurs. AMD fournit des VIP pour les conceptions utilisant des composants AXI (AXI-MM, AXI_Stream) et des systèmes de traitement (Zynq™ 7000).

-

Fonctionnalités clés

- Générateur de trafic

Générateur de trafic AXI pour AXI4, AXI4-Stream, AXI4-Lite

- AXI VIP et AXI Stream VIP

Prise en charge complète d'AXI et d'AXI Stream Protocol Checker

- VIP Zynq 7000 et VIP MPSoC Zynq UltraScale+™

Prise en charge de la simulation fonctionnelle pour les applications basées sur Zynq 7000 et Zynq UltraScale+ MPSoC

- Contrôle, interfaces et système de traitement (CIPS VIP) Versal™

Prise en charge de la simulation fonctionnelle de l'IP de contrôle, d'interfaces et de système de traitement (CIPS)