-

주요 특징

- 시뮬레이션 기능

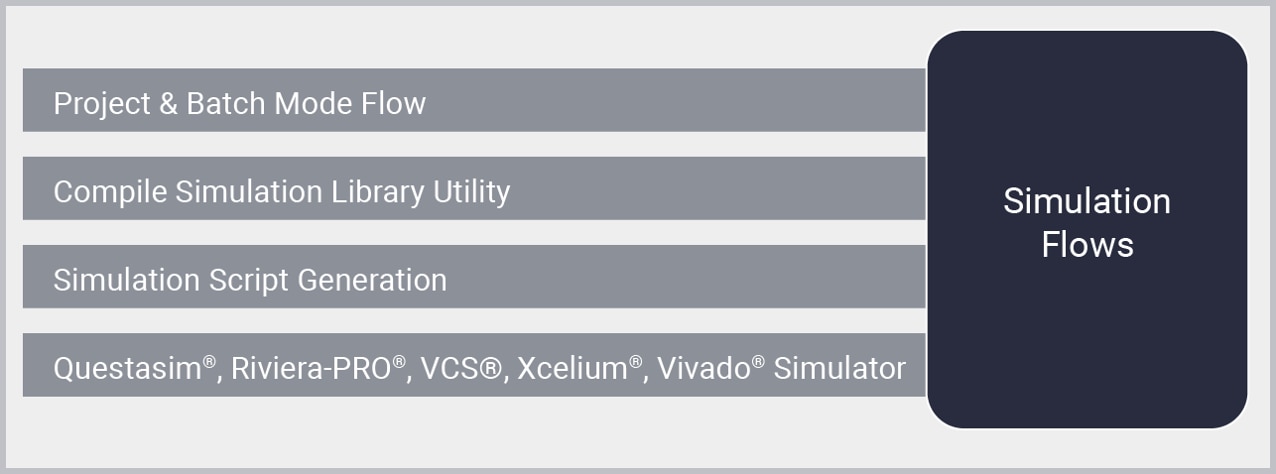

- 시뮬레이션 흐름은 사용자 환경에서 지원되는 시뮬레이터에 대한 시뮬레이션 라이브러리를 컴파일하여 컴파일된 라이브러리를 재사용할 수 있는 기능을 제공합니다.

- 동작, 합성 후 기능 및 타이밍 시뮬레이션, 구현 후 기능 및 타이밍 시뮬레이션 등 설계 프로세스의 여러 단계에서 설계 무결성 시뮬레이션 및 검증 가능

- 모든 시뮬레이터에 대해 일관된 3단계 프로세스(컴파일, 정교화, 시뮬레이션)를 사용하는 단일 시뮬레이션 통합

- 사용자 고유의 환경을 사용하여 검증할 수 있도록 엔터프라이즈 타사 시뮬레이터용 시뮬레이션 스크립트 생성

개요

검증 및 HW 디버그는 최종 FPGA 구현의 기능, 성능, 신뢰성을 보장하는 데 중요합니다. Vivado의 검증 기능으로 설계 기능의 효율적인 검증이 가능하며, 포괄적인 디버깅 기능을 활용하여 엔지니어는 복잡한 FPGA 설계 내에서 효율적으로 문제를 찾고 해결할 수 있습니다.

기능

- 로직 시뮬레이션

- 검증 IP

시뮬레이션 흐름

AMD Vivado™ Design Suite는 단일 최첨단 IDE(Integrated Design Environment)에 모두 포함된 다양한 설계 입력, 타이밍 분석, 하드웨어 디버그, 시뮬레이션 기능을 제공합니다. 이 흐름을 통해 지원되는 모든 시뮬레이터에 대한 통합 및 엔터프라이즈 검증 요구 사항을 모두 충족할 수 있습니다.

Vivado를 사용하면 완전히 통합된 Vivado Simulator 및 타사 HDL 시뮬레이터를 위한 동작, 합성 후 및 구현 후(기능 또는 타이밍) 시뮬레이션이 가능합니다. 설계 주기 초반에 시뮬레이션에 소요되는 시간은 문제를 조기에 식별하는 데 도움이 되며 흐름의 후반 단계에 비해 처리 시간을 크게 단축합니다.

사용자 검증 환경에서 유연성을 높이기 위해 Vivado는 통합 환경을 지원하고 외부 검증 설정과 함께 사용할 스크립트를 제공합니다.

Vivado IDE는 대화형 시뮬레이션 사용자를 위한 통합 모드와 고급 검증 엔지니어를 위한 스크립트 모드에서 모든 주요 시뮬레이터를 지원합니다.

Aldec - Active-HDL® 및 Riviera-PRO®, Cadence Xcelium® Simulator, Siemens EDA - ModelSim® 및 Questasim®, Synopsys VCS® 및 AMD Vivado Simulator

Vivado Simulator

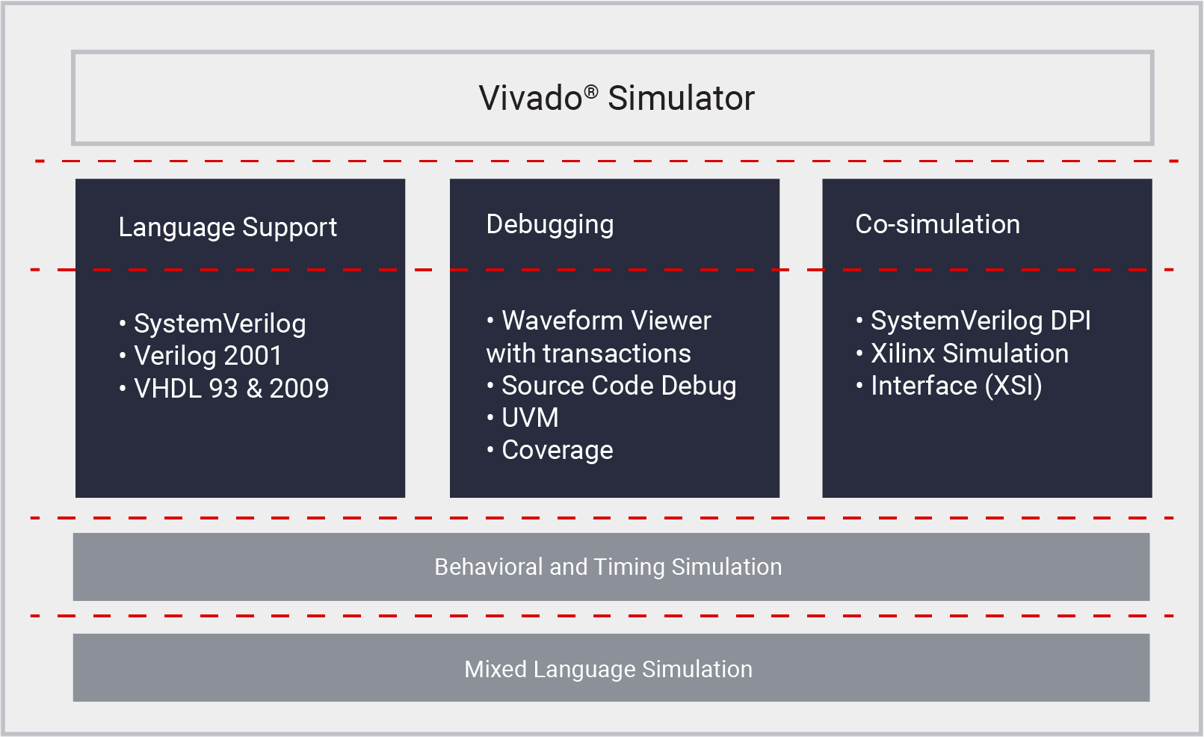

Vivado™ Simulator는 Verilog, SystemVerilog, VHDL 언어를 지원하는 풍부한 기능의 혼합 언어 시뮬레이터입니다. Vivado Simulator는 Vivado의 일부이며 추가 비용 없이 사용할 수 있습니다. 디자인 크기, 인스턴스 또는 라인 제한이 없으며 단일 Vivado 라이선스를 사용하여 혼합 언어 시뮬레이션의 무제한 인스턴스를 실행할 수 있습니다.

Vivado Simulator는 AMD 고객의 검증 요구를 충족시키기 위한 강력한 디버깅 기능을 갖추어 Windows® 및 Linux® 운영 체제를 모두 지원합니다.

Vivado Simulator는 단일 언어 및 혼합 언어 디자인에 대한 동작 및 타이밍 시뮬레이션을 지원하는 HDL(Hardware Description Language) 이벤트 기반 시뮬레이터입니다.

-

주요 특징

- 언어 지원

- SystemVerilog(Constraint Randomization 및 기능 적용 범위 포함)

- Verilog 2001

- VHDL 93 및 VHDL 2008

- 디버깅 및 검증

- 디지털/아날로그 파형 및 트랜잭션 보기를 지원하는 고급 파형 뷰어

- 중단점, 하위 프로그램 디버그 및 크로스 프로빙과 같은 포괄적인 디버깅 도구

- UVM 1.2 라이브러리 지원

- 기능 적용 범위

- GUI 및 스크립트 모드 모두 지원

- 공동 시뮬레이션

- DPI(직접 프로그래밍 인터페이스)

- XSI(Xilinx 시뮬레이션 인터페이스)

검증 IP

AMD의 VIP(검증 IP) 포트폴리오는 사용자에게 시뮬레이션 환경에서 설계를 쉽고 빠르며 더욱 효과적으로 검증하고 디버깅할 수 있는 기능을 제공합니다. 검증 IP 코어는 올바른 상호 운용성과 시스템 동작을 보장하기 위한 특수 목적용 검증 모델입니다. EDA 업계의 기업들은 표준 기반 인터페이스(AXI, PCIe, SAS, SATA, USB, HDMI, ENET 등)를 위한 VIP를 개발합니다. VIP를 사용하면 설계 품질이 향상되고 재사용성 덕분에 일정의 시간을 단축할 수 있다는 장점이 있습니다.

AMD VIP 코어는 ARM 라이선스 어설션을 통한 전체 AXI 프로토콜 검사를 제공하고, 모든 주요 시뮬레이터를 지원하며, Vivado에 무료로 포함된 SystemVerilog 기반 시뮬레이션 모델입니다. AMD는 AXI 구성 요소 수준(AXI-MM, AXI_Stream) 및 처리 시스템(Zynq™ 7000) 설계를 사용하는 설계에서 사용할 VIP를 제공합니다.

-

주요 특징

- Traffic Generator

AXI4, AXI4-Stream, AXI4-Lite용 AXI Traffic Generator

- AXI VIP 및 AXI Stream VIP

전체 AXI 및 AXI Stream Protocol Checker 지원

- Zynq 7000 VIP 및 Zynq UltraScale+™ MPSoC VIP

Zynq 7000 및 Zynq UltraScale+ MPSoC 기반 애플리케이션에 대한 기능 시뮬레이션 지원

- Versal™ CIPS VIP(Control, Interfaces, and Processing System VIP)

CIPS(Control, Interfaces, and Processing System) IP의 기능 시뮬레이션 지원