-

主な特長

- シミュレーション機能

- シミュレーション フローは、ユーザーの環境でサポートされているシミュレータ用にシミュレーション ライブラリをコンパイルし、コンパイル済みライブラリの再利用を可能にします。

- ビヘイビアー シミュレーションや合成後の論理/タイミング シミュレーション、インプリメンテーション後の論理/タイミング シミュレーションなど、さまざまな設計段階でデザイン インテグリティをシミュレーションし、検証できます。

- すべてのシミュレータで一貫した 3 ステップのプロセス (コンパイル、エラボレート、シミュレーション) を使用する統一されたシミュレーション環境を提供します。

- エンタープライズ サードパーティ シミュレータ用のシミュレーション スクリプトを生成して、ユーザー独自の環境で検証できます。

概要

検証とハードウェア デバッグは、最終的な FPGA インプリメンテーションの機能性、パフォーマンス、信頼性を確保するために重要です。Vivado の検証機能ではデザインの効率的な検証を可能にし、包括的なデバッグ機能では複雑な FPGA デザインの問題をエンジニアがすばやく特定して解決できるようサポートします。

機能

- ロジック シミュレーション

- Verification IP

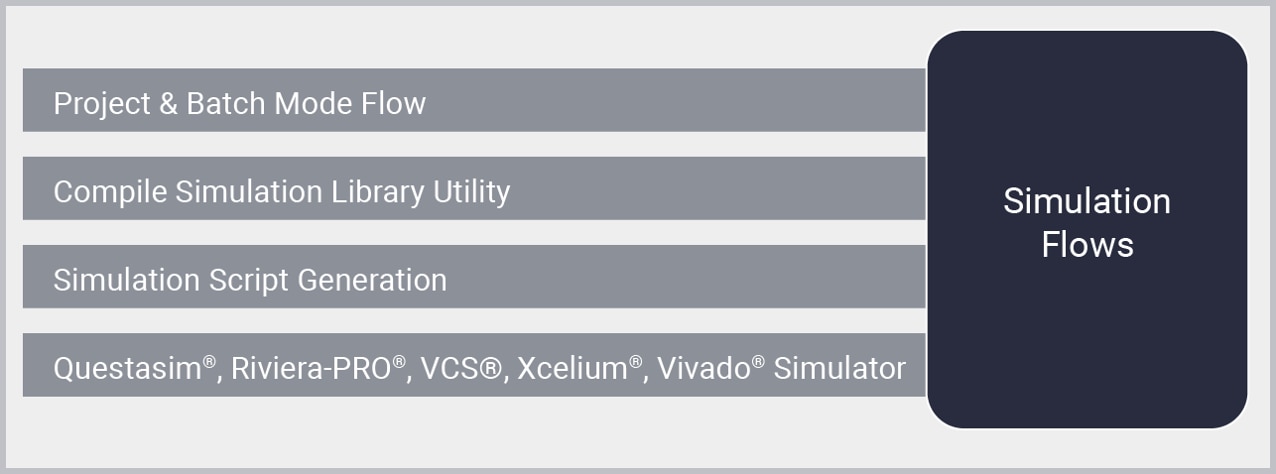

シミュレーション フロー

AMD Vivado™ Design Suite は、デザイン入力、タイミング解析、ハードウェア デバッグ、シミュレーションなどの機能を提供する最先端の統合設計環境 (IDE) です。このフローは、Vivado 統合環境に統合されている検証機能とサードパーティの検証機能の両方に対応します。

Vivado 環境では、完全統合された Vivado シミュレータおよびサードパーティの HDL シミュレータを使用するシミュレーション (合成後またはインプリメンテーション後の論理シミュレーションおよびタイミング シミュレーション) が可能です。設計の早い段階でシミュレーションを行うことにより、早期に問題を解決でき、フローの最終段階で行う場合よりも開発時間を大幅に削減できます。

ユーザー検証環境に柔軟に対応できるように、Vivado では統合環境のサポートはもちろんのこと、外部の検証環境でも使用できるスクリプトを生成できます。

Vivado IDE は、インタラクティブ シミュレーション ユーザー向けの統合モードとアドバンス検証エンジニア向けのスクリプト モードのすべての主要シミュレータをサポートしています。

Aldec の Active-HDL® および Riviera-PRO®、Cadence の Xcelium® Simulator、Siemens EDA の ModelSim® および Questasim®、Synopsys の VCS®、AMD の Vivado Simulator が含まれます。

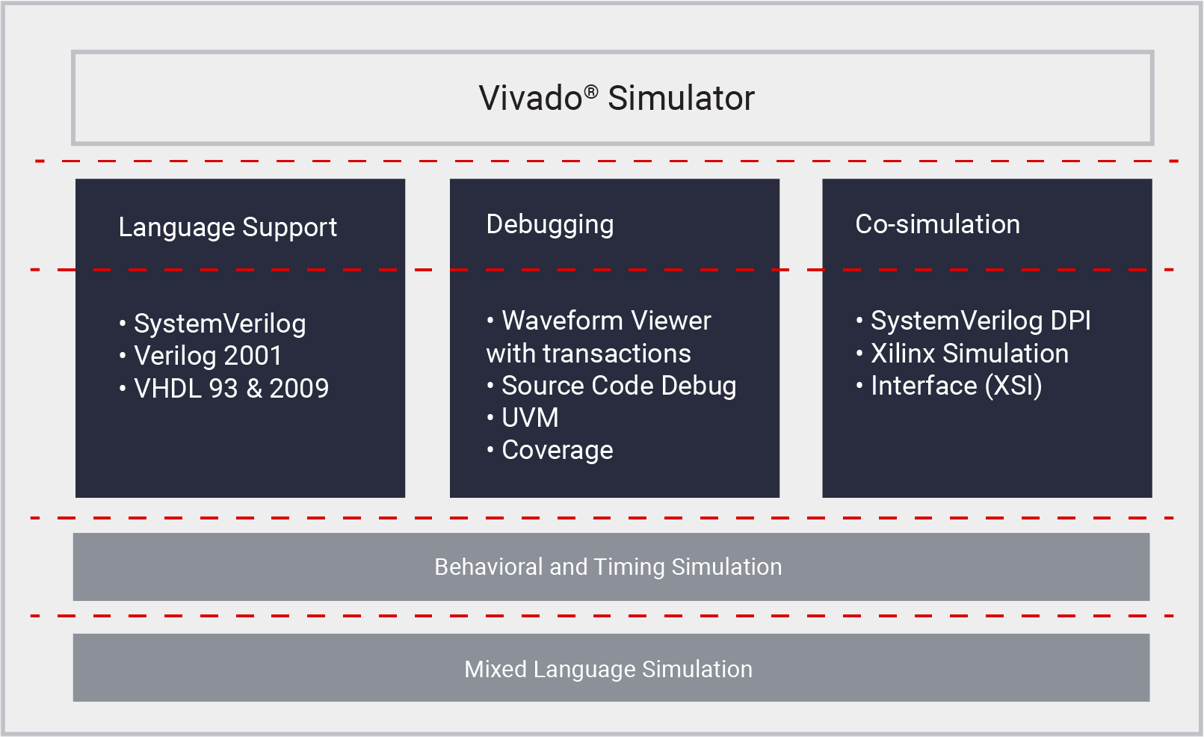

Vivado シミュレータ

Vivado™ シミュレータは、豊富な機能を備えた Verilog、SystemVerilog および VHDL 言語に対応する混合言語シミュレータです。Vivado の一部として含まれており、追加料金は不要です。デザイン サイズ、インスタンス、または行数の制限がないため、1 つの Vivado ライセンスで無制限のインスタンスの混合言語シミュレーションを実行できます。

Vivado Simulator は、Windows® および Linux® の両方のオペレーティング システムをサポートし、AMD のお客様の検証ニーズに対応するための強力なデバッグ機能を備えています。

Vivado シミュレータは、ハードウェア記述言語 (HDL) のイベントドリブン シミュレータで、単一言語および混合言語デザインのビヘイビアーおよびタイミング シミュレーションをサポートします。

-

主な特長

- 言語サポート

- SystemVerilog (制約付きランダム化と機能カバレッジを含む)

- Verilog 2001

- VHDL 93 および VHDL 2008

- デバッグと検証

- デジタル/アナログ波形とトランザクション ビューをサポートする高度な波形ビューアー

- ブレークポイント、サブプログラムのデバッグ、クロスプローブなどに対応できる包括的なデバッグツール

- UVM 1.2 ライブラリをサポート

- 機能カバレッジ

- GUI モードとスクリプト モードの両方をサポート

- 協調シミュレーション

- ダイレクト プログラミング インターフェイス (DPI)

- ザイリンクス シミュレーション インターフェイス (XSI)

Verification IP

Verification IP (VIP) ポートフォリオにより、シミュレーション環境でのデザインの検証とデバッグを容易に、迅速に、より効果的に実行できます。Verification IP コアは、適切な相互運用性とシステム動作を確保することを目的とした検証モデルです。DA 業界の企業は、規格ベース インターフェイス (AXI、PCIe、SAS、SATA、USB、HDMI、ENET など) に対応する VIP を開発しています。VIP を使用するメリットには、デザインの品質向上、再利用によるスケジュールの短縮などがあります。

AMD の VIP コアは、ARM ライセンスのアサーションを使用する完全 AXI プロトコル チェック機能を提供する SystemVerilog ベースのシミュレーション モデルで、主要シミュレータをすべてサポートし、Vivado に含まれる無償のコアです。AMD は、AXI コンポーネント レベル (AXI-MM、AXI_Stream) を使用するデザインやプロセッシング システム (Zynq™ 7000) デザインで使用するための VIP を提供しています。

-

主な特長

- トラフィック ジェネレーター

AXI4、AXI4-Stream、AXI4-Lite 用 AXI トラフィック ジェネレーター

- AXI VIP および AXI Stream VIP

AXI および AXI Stream プロトコル チェッカーを完全サポート

- Zynq 7000 VIP および Zynq UltraScale+™ MPSoC VIP

Zynq 7000 および Zynq UltraScale+ MPSoC をベースとするアプリケーションの論理シミュレーションをサポート

- Versal™ CIPS VIP (Control, Interfaces, and Processing System VIP)

CIPS (Control, Interface and Processing System) IP の論理シミュレーションをサポート