-

Hauptmerkmale

- Simulationsfunktionen

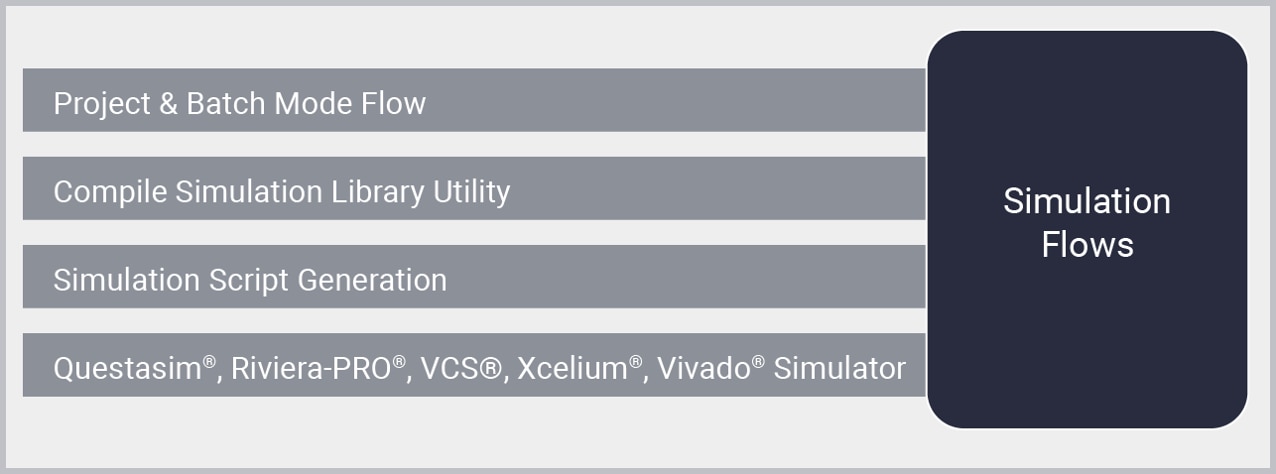

- Simulations-Flows bieten die Möglichkeit, Simulationsbibliotheken für die unterstützten Simulatoren in der Benutzerumgebung zu kompilieren, um die Wiederverwendung kompilierter Bibliotheken zu ermöglichen.

- Fähigkeit zur Simulation und Verifizierung der Designintegrität in verschiedenen Phasen des Designprozesses, z. B. Verhaltens-, Post-Synthese-Funktions- und Timing-Simulation sowie Funktions- und Timing-Simulation nach der Implementierung.

- Einheitliche Simulationsintegration mit konsistentem 3-Schritte-Prozess (Kompilieren, Ausarbeiten, Simulieren) für alle Simulatoren

- Simulationsskriptgenerierung für Simulatoren von Drittanbietern auf Unternehmensebene, um die Verifizierung mithilfe von benutzereigenen Umgebungen zu ermöglichen.

Übersicht

Verifizierung und Hardware-Debugging sind wichtig, um die Funktionalität, Leistung und Zuverlässigkeit der finalen FPGA-Implementierung zu gewährleisten. Die Verifizierungsfunktionen von Vivado ermöglichen eine effiziente Validierung der Designfunktionalität, während die umfassenden Debugging-Funktionen Ingenieuren die effiziente Lokalisierung und Behebung von Problemen in komplexen FPGA-Designs ermöglichen.

Funktionen

- Logische Simulation

- Verification IP

Simulations-Flow

AMD Vivado™ Design Suite bietet eine Vielzahl von Designeinstiegs-, Timing-Analyse-, Hardware-Debugging- und Simulationsfunktionen, die alle in einer einzigen, hochmodernen integrierten Designumgebung (IDE) enthalten sind. Dieser Flow ermöglicht sowohl die integrierte als auch die unternehmensweite Verifizierung aller unterstützten Simulatoren.

Vivado ermöglicht Verhaltens-, Post-Synthese- und Post-Implementierungssimulationen (für Funktionen oder Timing) für den vollständig integrierten Vivado Simulator und HDL-Simulatoren von Drittanbietern. Der Zeitaufwand für die Simulation zu Beginn des Designzyklus hilft dabei, Probleme frühzeitig zu erkennen und die Bearbeitungszeiten im Vergleich zu späteren Phasen des Flows erheblich zu verkürzen.

Um die Flexibilität in Umgebungen zur Benutzerüberprüfung zu steigern, bietet Vivado sowohl Unterstützung für eine integrierte Umgebung als auch Skripte zur Verwendung mit externen Verifizierungseinstellungen.

Die Vivado IDE unterstützt alle wichtigen Simulatoren im integrierten Modus für interaktive Simulationsbenutzer und im Skriptmodus für fortgeschrittene Verifikationsingenieure.

Aldec – Active-HDL® und Riviera-pro®, Cadence Xcelium® Simulator, Siemens EDA – ModelSim® und Questasim®, Synopsys VCS® und AMD Vivado Simulator

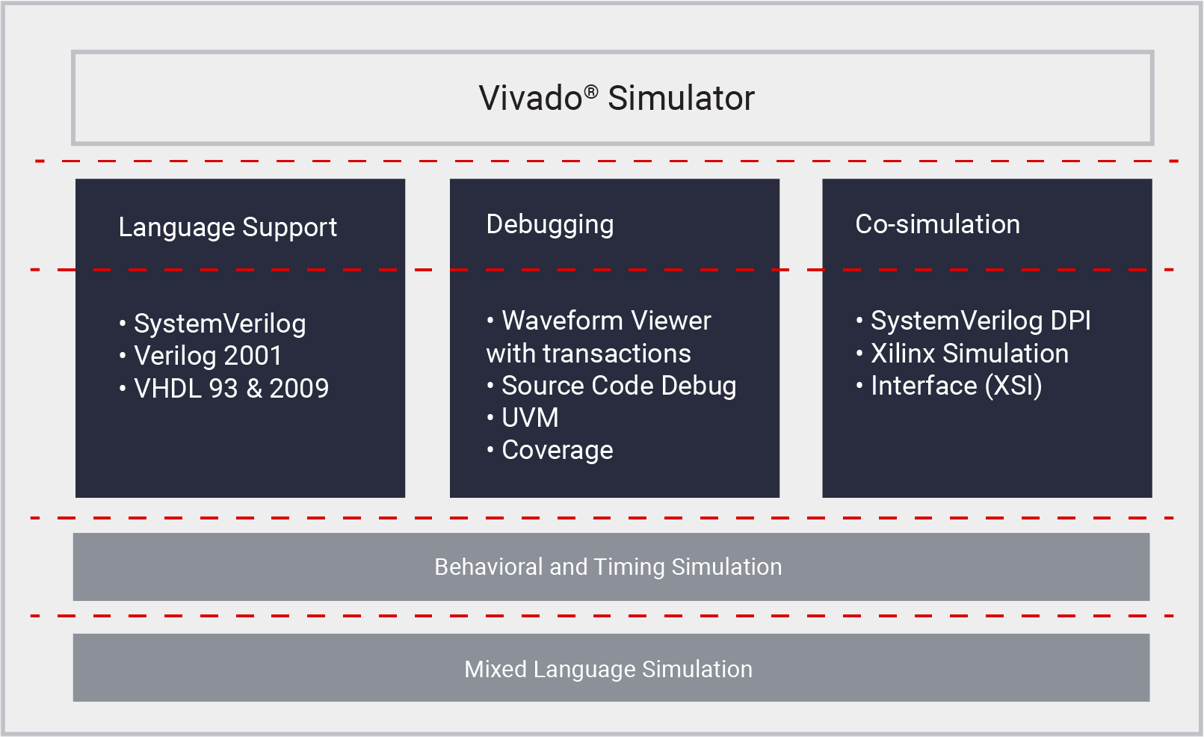

Vivado Simulator

Der Vivado™ Simulator ist ein vielseitiger Simulator für gemischte Sprachen, der Verilog-, SystemVerilog- und VHDL-Sprachen unterstützt. Der Vivado Simulator ist im Preis von Vivado inbegriffen. Er hat keine Begrenzungen in Bezug auf Designgröße, Instanzen oder Linien und ermöglicht die Ausführung von unbegrenzten Instanzen von Simulationen mit gemischten Sprachen mit einer einzigen Vivado-Lizenz.

Vivado Simulator unterstützt sowohl Windows® als auch Linux® Betriebssysteme mit leistungsstarken Debugging-Funktionen, die auf die Verifizierungsanforderungen von AMD Kunden ausgerichtet sind.

Vivado Simulator ist ein ereignisgesteuerter Simulator für Hardware-Beschreibungssprachen (HDL), der Verhaltens- und Timing-Simulationen für Designs mit einer Sprache und gemischten Sprachen unterstützt.

-

Hauptmerkmale

- Sprachunterstützung

- SystemVerilog (einschließlich Randomisierung und Funktionsabdeckung)

- Verilog 2001

- VHDL 93 und VHDL 2008

- Debugging und Verifizierung

- Erweiterter Waveform Viewer, der eine digitale/analoge Kurven- und Transaktionsansicht unterstützt

- Umfassende Debugging-Tools wie Breakpoints, Subprogramm-Debugging und Cross-Probing

- Unterstützung der UVM 1.2-Bibliothek

- Funktionale Abdeckung

- Unterstützt GUI- und Skriptmodus

- Co-Simulation

- Direkte Programmierschnittstelle (DPI)

- Xilinx Simulationsschnittstelle (XSI)

Verification IP

Das Verification IP(VIP)-Portfolio von AMD bietet Benutzern die Möglichkeit, ihre Designs in einer Simulationsumgebung einfach, schnell und effektiver zu verifizieren und zu debuggen. Verification IP-Kerne sind speziell entwickelte Verifizierungsmodelle, deren Ziel es ist, die korrekte Interoperabilität und das korrekte Systemverhalten sicherzustellen. Unternehmen in der EDA-Branche entwickeln VIP für standardbasierte Schnittstellen (AXI, PCIe, SAS, SATA, USB, HDMI, ENET usw.). Zu den Vorteilen der VIP-Nutzung gehören verbesserte Designqualität und eine verkürzte Zeitplanung aufgrund der Wiederverwendbarkeit.

AMD VIP Cores sind SystemVerilog-basierte Simulationsmodelle, die eine vollständige AXI-Protokollprüfung mit ARM-lizenzierten Assertions ermöglichen, alle wichtigen Simulatoren unterstützen und kostenlos in Vivado enthalten sind. AMD bietet VIP für die Verwendung in Designs auf AXI-Komponentenebene (AXI-MM, AXI_Stream) und in Verarbeitungssystemen (Zynq™ 7000).

-

Hauptmerkmale

- Traffic Generator

AXI Traffic Generator für AXI4, AXI4-Stream, AXI4-Lite

- AXI VIP und AXI STREAM VIP

Vollständige Unterstützung von AXI und AXI Stream Protocol Checker

- Zynq 7000 VIP und Zynq UltraScale+™ MPSoC VIP

Unterstützung für funktionale Simulationen für Zynq 7000 und Zynq UltraScale+ MPSoC-basierte Anwendungen

- Versal™ Steuerungs-, Schnittstellen- und Verarbeitungssystem (Control, Interfaces, and Processing System) (CIPS VIP)

Unterstützung der funktionalen Simulation von Control, Interfaces, and Processing System (CIPS) IP