개요

개발자가 새로운 기능을 추가하고 설계를 디버깅할 때는 설계를 반복하는 것이 일반적입니다. 대부분의 경우 이러한 반복은 점진적인 변경이며, 대개 설계의 작은 부분 내에서 변경되는 것입니다. AMD Vivado™ Design Suite는 설계 반복 시간을 크게 줄여주는 두 가지 핵심 기술인 증분 컴파일 및 추상 셸을 제공합니다.

증분 컴파일

빠르게 진화하는 FPGA 설계 분야에서는 크고 복잡한 설계를 작성할 때 설계 반복 속도를 높이는 것이 무엇보다 중요합니다. 일반적으로 설계 소스 코드, 제약 조건, 설정을 반복적으로 변경합니다. 기존의 흐름에서는 이러한 변경 작업을 수행하려면 전체 설계를 완전히 다시 컴파일해야 하므로 시간이 오래 걸리고 리소스도 많이 소모될 수 있습니다.

Vivado 증분 컴파일은 전체 컴파일이 아닌 설계에서 수정된 부분만 지능적으로 식별하고 다시 컴파일함으로써 이러한 문제를 해결합니다. 이 접근 방식을 이용하면 설계 변경이 작은 경우 컴파일 시간을 대폭 줄이고 설계자가 설계를 더 빠르게 반복하는 데 도움이 되어 엔지니어가 설계 변경 사항을 신속하게 검증할 수 있습니다.

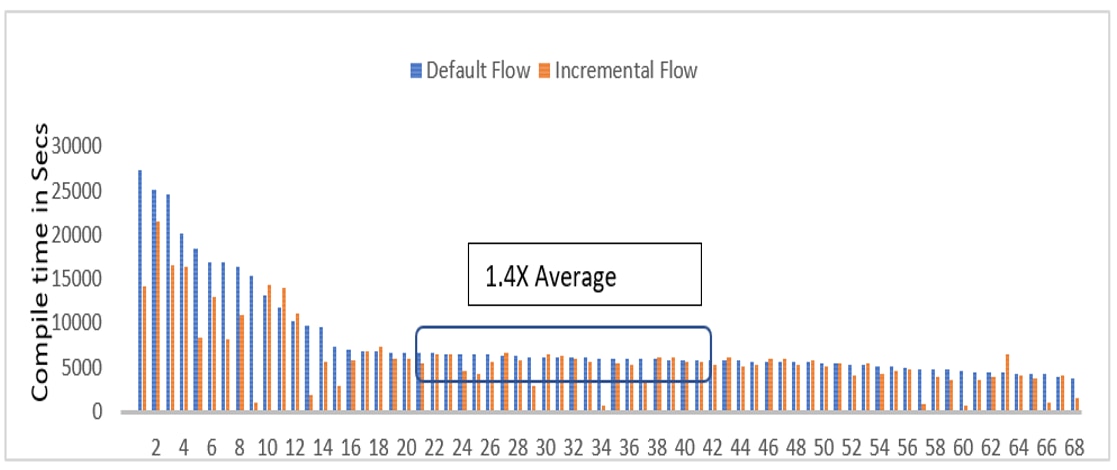

아래 벤치마크 데이터는 기본 컴파일의 컴파일 시간(파란색)과 Vivado Design Suite 2022.2 버전의 68개 설계의 증분 흐름(빨간색)을 보여줍니다. 이 벤치마크를 통해 증분 컴파일을 사용한 재컴파일 시간이 평균 1.4배 더 빠르다는 것을 확인할 수 있습니다.

2022.2를 사용한 UltraScale+™ 설계에 대한 증분 컴파일 벤치마크 결과

각주: 측정은 2022년 10월 현재 Vivado™ 엔지니어링 팀에서 68개 설계에 대해 Vivado 소프트웨어 도구 2022.2의 기본 컴파일과 증분 컴파일을 비교하여 수행했습니다. 더 대표적인 평균 성능을 제공하기 위해 6배가 넘는 6개의 이상값 비교는 폐기되었습니다. 비교를 위해 설계의 5%를 점진적으로 컴파일했습니다. 상용 시스템에서의 실제 개선 효과는 시스템 하드웨어, 소프트웨어 및 드라이버 버전, BIOS 설정 등의 요인에 따라 다를 수 있습니다.

요약하자면, Vivado 증분 컴파일은 Vivado Design Suite에 포함된 기능으로, FPGA 설계자가 보다 효과적으로 작업할 수 있도록 하여 설계 변경에 대한 처리 시간을 단축하고 FPGA의 개발을 가속화합니다.

추상 셸

추상 셸은 크고 복잡한 설계의 컴파일 속도를 높이기 위해 최첨단 접근 방식을 활용합니다. 설계의 일부에 대해 간소화된 버전을 생성하는 동시에 나머지 설계에 대한 컨텍스트를 제공할 수 있습니다. 추상 셸은 설계의 특정 영역을 격리함으로써 엔지니어가 전체 설계를 다시 컴파일하지 않고도 모듈을 독립적으로 구현하고 검증할 수 있게 해줍니다. 추상 셸을 사용하면 설계자가 설계에서 변경되는 부분과 그대로 유지되는 부분을 표시할 수 있습니다.

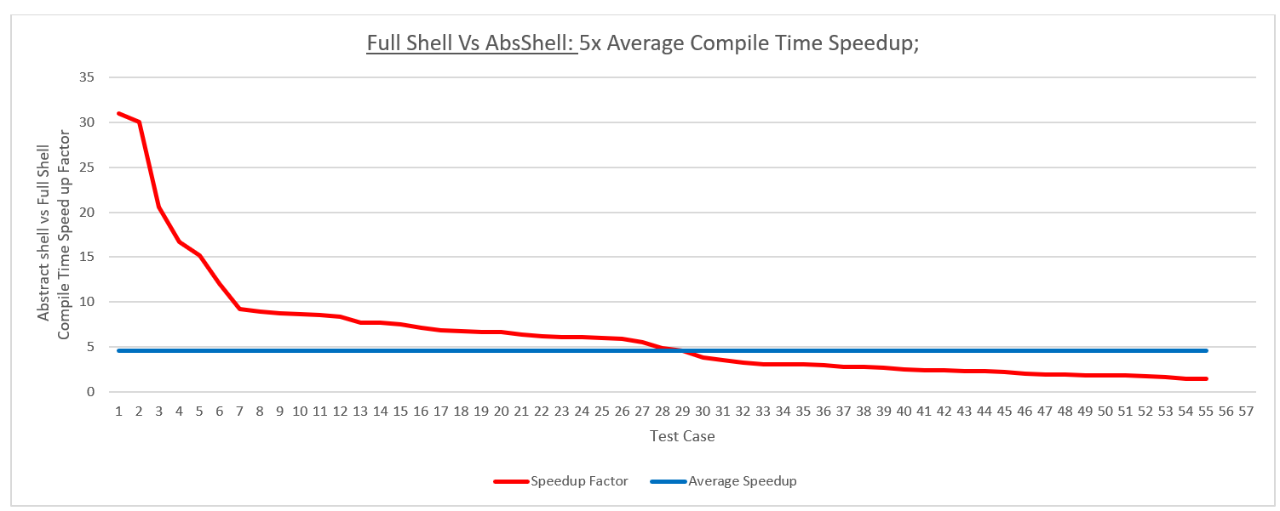

아래 벤치마크 데이터는 전체 셸에 비해 5배 높은 추상 셸의 평균 컴파일 시간 가속을 보여줍니다. 빨간색 선은 전체 셸 실행 대비 추상 셸 실행의 컴파일 시간 가속을 나타냅니다. 파란색 막대는 55개 테스트 케이스에서 5배 높은 평균 컴파일 시간 가속을 나타냅니다.

2021.1을 사용한 UltraScale+ 디바이스 설계에 대한 추상 셸의 이점 벤치마크 결과

각주: 측정은 2021년 6월 현재 Vivado™ 엔지니어링 팀에서 55개 설계에 대해 Vivado 소프트웨어 도구 2021.1의 기본 컴파일과 추상 셸 컴파일을 비교하여 수행했습니다. 상용 시스템에서의 실제 개선 효과는 시스템 하드웨어, 소프트웨어 및 드라이버 버전, BIOS 설정 등의 요인에 따라 다를 수 있습니다.

요약하자면, 추상 셸은 설계자가 FPGA 설계를 작성, 수정, 디버깅, 최적화하는 방식을 혁신하는 빠르고 효율적인 모듈식 접근 방식을 제공함으로써 FPGA 설계를 혁신합니다.