- Descripción general

- Introducción

Procesamiento de señal digital

AMD Vitis™ DSP Library contiene:

- Niveles L1, L2 y L3 para el procesamiento de señales digitales

- AI Engine DSP Library

- Programmable Logic (PL) DSP Library

Vitis AI Engine DSP Library: características clave

Vitis BLAS Library incluye las siguientes funciones de matriz y operación vectorial

Binarios de acelerador

Descarga binarios de acelerador en la plataforma

Evaluaciones comparativas

Se proporcionan evaluaciones comparativas y QoR (Quality of Results, calidad de los resultados)

Biblioteca de código abierto

Biblioteca de código abierto para aplicaciones de DSP

Ejemplo de diseño

Un ejemplo de diseño se proporciona con esta biblioteca

Kernels en C++

Los kernels están codificados en el conocido C++

Diseños complejos

Combina kernels y crea gráficos para diseños complejos

Vitis AI Engine DSP Library: funciones

Vitis AI Engine DSP Library es una biblioteca configurable de elementos que se pueden utilizar para desarrollar aplicaciones en motores Versal® AI Engine. Es una biblioteca de código abierto para aplicaciones de DSP. El punto de entrada de usuario para cada función de la biblioteca es un gráfico de nivel L2. Cada gráfico de punto de entrada contendrá uno o más kernels de nivel L1 y puede contener uno o más objetos de gráfico. No se recomienda el uso directo de kernels de nivel L1 o cualquier otra clase gráfica no identificada como punto de entrada.

Vitis AI Engine DSP Library consta de los siguientes elementos de DSP:

- Filtros:

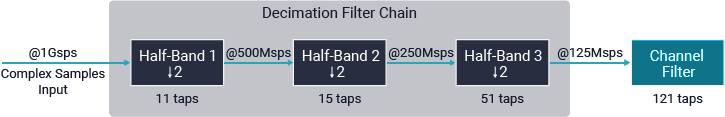

- FIR (Finite Impulse Response, respuesta finita al impulso) de tasa única

- FIR de interpolación/diezmado de media banda

- FIR enteros y fraccionarios de interpolación/diezmado

- FFT/iFFT

- Implementación de un solo canal y DIT (decimation in time, diezmado en tiempo)

- Multiplicación de matriz

- Multiplicación de matriz general

- Widget de conversión de API

- Flexibilidad al conectar otros kernels

- Widget real a complejo

- Utilidad para convertir datos reales en complejos o viceversa

- DDS/mezclador

- Único modo de síntesis digital directa

- Mezclador

Para obtener una lista completa de las funciones de DSP disponibles, consulta Funciones de la biblioteca DSP.

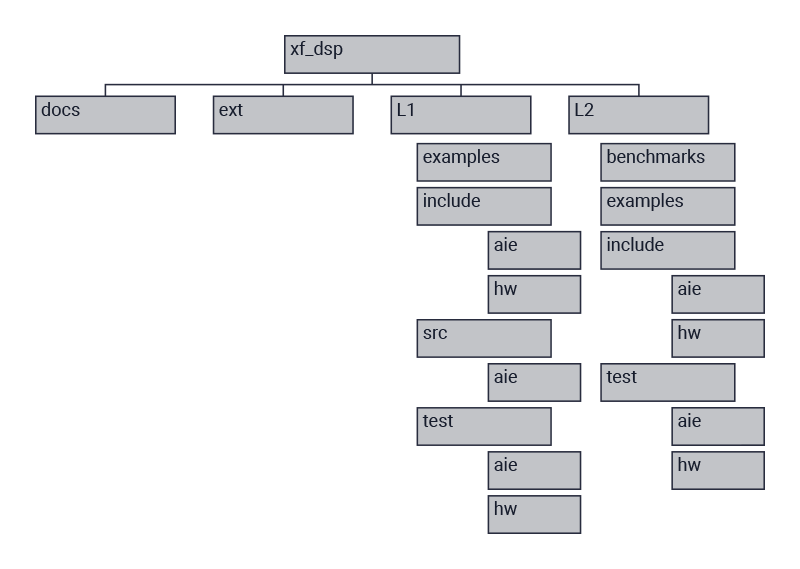

Vitis AI Engine DSP Library: organización

Vitis AI Engine DSP Library consiste en algoritmos de DSP optimizados para aprovechar al máximo la potencia de procesamiento de los dispositivos Versal, que contienen una variedad de motores de IA.

La biblioteca está organizada en tres tipos de diseños de motores de IA:

- Kernels de motores de IA L1

- Gráficos de motores de IA L2

- API de software L3

Nota: L3 aún no está disponible

Vitis Programmable Logic (PL) DSP Library: introducción

Vitis PL DSP Library implementa una transformada discreta de Fourier utilizando un algoritmo FFT para la aceleración en las FPGA de AMD Xilinx. La biblioteca consta de tres tipos de implementaciones:

- Primitivas de PL L1

- Kernels de PL L2

- API de software L3

Estas implementaciones están organizadas en subdirectorios de hardware de los tipos L1, L2 y L3 correspondientes.

| Primitivas de PL L1 | Puede ser aprovechadas por los desarrolladores que trabajan en la implementación del diseño de hardware o diseñando kernels de hardware para la aceleración. Especialmente adecuadas para diseñadores de hardware. |

| Kernels de PL L2 | Kernels prediseñados basados en HLS (high-level synthesis, síntesis de alto nivel) que se pueden utilizar directamente para la aceleración de FPGA de diferentes aplicaciones integradas en Vitis Runtime Library. |

| API de software L3 | Se proporciona en C, C++ y Python, lo cual permite a los desarrolladores de software descargar el cálculo de la FFT (Fast Fourier Transform, transformada rápida de Fourier) en las FPGA para la aceleración. |

Vitis PL DSP Library - Funciones

Vitis PL DSP Library proporciona una FFT con SSR (super sample rate, superfrecuencia de muestreo) totalmente sintetizable basada en PL, así como una versión bidimensional de FFT.

- Módulo FPGA de L1 con FFT de SSR unidimensional (lineal)

- Proporciona una FFT con SSR totalmente sintetizable con una arquitectura sistólica para procesar múltiples muestras de entrada en cada ciclo de reloj.

- Permite que el factor SSR procese el número de muestras en paralelo por ciclo.

- Se implementa como una función de plantilla de C++ que se sintetiza en una arquitectura de streaming.

- Se puede parametrizar a través de parámetros de plantilla.

- Módulo FPGA de L1 con SSR FFT bidimensional (matriz)

- Proporciona una FFT bidimensional totalmente sintetizable como primitiva L1.

- Se transforma en un kernel L2 del entorno de Vitis mediante la adición de adaptadores de memoria.

- Diseñado para tener una variedad de interfaces de stream tan amplia como las ranuras de la memoria DDR (double-data rate, tasa de datos doble) del dispositivo en las placas, por ejemplo, Alveo™ U200, U250 y U280.

Para ver la documentación detallada, dirígete a: Módulo FPGA de L1 de SSR FFT unidimensional (lineal) y Módulo FPGA de L1 de SSR FFT bidimensional (matriz).