- Übersicht

- Erste Schritte

Digitale Signalverarbeitung

Die AMD Vitis™ DSP-Bibliothek enthält:

- Die Ebenen L1, L2 und L3 für die digitale Signalverarbeitung

- KI-Engine-DSP-Bibliothek

- DSP-Bibliothek für programmierbare Logik (PL)

Vitis AI Engine DSP-Bibliothek – Hauptfunktionen

Die Vitis BLAS-Bibliothek umfasst die folgenden Funktionen für Matrix- und Vektoroperationen

Beschleuniger-Binärdateien

Download von Beschleuniger-Binärdateien auf die Plattform

Benchmarks

Benchmarks und Ergebnisqualität (Quality of Results, QoR) werden bereitgestellt

Open-Source-Bibliothek

Open-Source-Bibliothek für DSP-Anwendungen

Beispielkonzept

Diese Bibliothek enthält ein Beispielkonzept

Kernel in C++

Kernel sind im gängigen C++-Code programmiert

Komplexe Konzepte

Kernel kombinieren, um Graphen für komplexe Konzepte zu erstellen

Vitis AI Engine DSP-Bibliothek – Funktionen

Die Vitis AI Engine DSP-Bibliothek ist eine konfigurierbare Bibliothek von Elementen, die zur Entwicklung von Anwendungen auf Versal® AI Engines verwendet werden kann. Es handelt sich um eine Open-Source-Bibliothek für DSP-Anwendungen. Als Benutzereinstiegspunkt für die einzelnen Bibliotheksfunktionen dient ein Diagramm auf L2-Ebene. Jeder Einstiegspunktgraph enthält mindestens einen Kernel der Ebene L1 und kann mindestens ein Graphenobjekt enthalten. Die direkte Verwendung von L1-Kernels oder einer anderen Graphenklasse, die nicht als Einstiegspunkt identifiziert wurde, wird nicht empfohlen.

Die Vitis AI Engine DSP-Bibliothek besteht aus den folgenden DSP-Elementen:

- Filter:

- Einzelraten-FIR

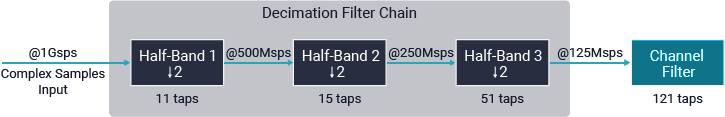

- Halbband-Interpolation-/Dezimierungs-FIR

- Ganzzahlige und fraktionale Interpolation-/Dezimierungs-FIR

- FFT/iFFT

- Einzelkanal-Implementierung mit Decimation in Time (DIT)

- Matrixmultiplikation

- Allgemeine Matrixmultiplikation

- Widget API Cast

- Flexibilität beim Verbinden anderer Kernel

- Widget Real to Complex

- Utility zur Konvertierung realer Daten in komplexe Daten oder umgekehrt

- DDS/Mixer

- Modus für nur direkte digitale Synthese

- Mixer

Eine vollständige Liste der verfügbaren DSP-Funktionen finden Sie unter DSP-Bibliotheksfunktionen.

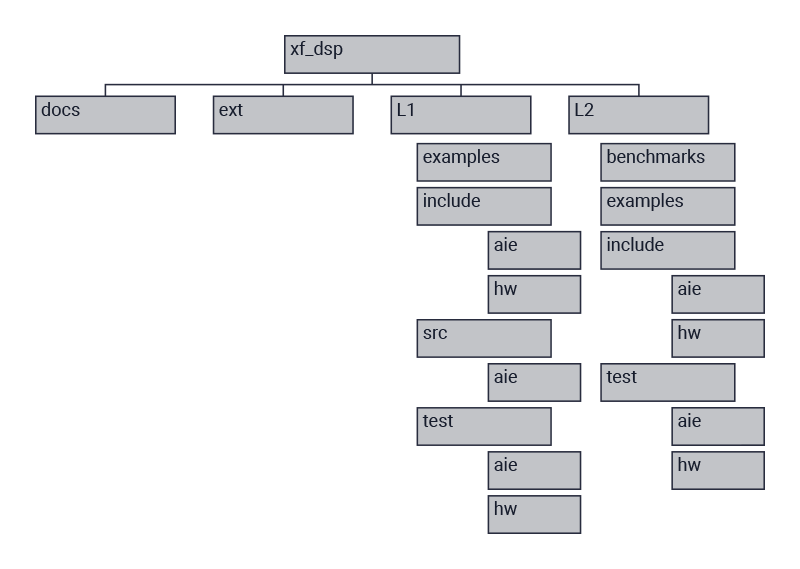

Vitis AI Engine DSP-Bibliothek – Organisation

Die Vitis AI Engine DSP-Bibliothek besteht aus speziell optimierten DSP-Algorithmen, mit der Sie die Verarbeitungsleistung von Versal Chips, die eine Reihe von KI-Engines enthalten, voll ausschöpfen können.

Die Bibliothek ist in drei Arten von KI-Engine-Designs unterteilt:

- L1-KI-Engine-Kernel

- L2-KI-Engine-Graphen

- L3-Software-APIs

Hinweis: L3 ist noch nicht verfügbar

Vitis DSP-Bibliothek für programmierbare Logik (PL) –Einführung

Die Vitis PL DSP-Bibliothek implementiert eine diskrete Fourier-Transformation mit einem FFT-Algorithmus zur Beschleunigung auf AMD Xilinx FPGAs. Die Bibliothek besteht aus drei Arten von Implementierungen:

- L1-PL-Primitive

- L2-PL-Kernel

- L3-Software-APIs

Diese Implementierungen sind in Hardware-Unterverzeichnissen der entsprechenden L1-, L2- und L3-Typen organisiert.

| L1-PL-Primitive | Kann von Entwicklern genutzt werden, die an der Implementierung von Hardwarekonzepten oder am Design von Hardware-Kernels zur Beschleunigung arbeiten. Besonders geeignet für Hardwareentwickler. |

| L2-PL-Kernel | Vordefinierte HLS-basierte Kernel, die direkt zur FPGA-Beschleunigung verschiedener Anwendungen bei der Integration mit der Vitis Laufzeitbibliothek verwendet werden können. |

| L3: Software-APIs | Werden in C, C++ und Python bereitgestellt. Softwareentwickler können mit ihnen zur Beschleunigung FFT-Berechnungen auf FPGAs auslagern. |

Vitis PL DSP-Bibliothek – Funktionen

Die Vitis PL DSP-Bibliothek bietet eine vollständig synthetisierbare PL-basierte SSR-FFT sowie eine 2-dimensionale FFT-Version.

- 1-dimensionales (Linien)-Modul für SSR-FFT auf L1-FPGA

- Bietet eine vollständig synthetisierbare SSR-FFT mit einer systolischen Architektur zur Verarbeitung mehrerer Eingangsabtastungen pro Taktzyklus

- Ermöglicht die Anzahl der parallel verarbeiteten Abtastungen pro Zyklus anhand des SSR-Faktors

- Wird als C++-Vorlagenfunktion implementiert, die zu einer Streaming-Architektur synthetisiert wird

- Kann über Vorlagenparameter parametriert werden

- 2-dimensionales (Matrix)-Modul für SSR-FFT auf L1-FPGA

- Bietet eine vollständig synthetisierbare 2-dimensionale FFT als L1-Primitiv

- Wird durch Hinzufügen von Speicheradaptern in einen L2-Umgebungs-Kernel von Vitis transformiert

- Entwickelt für eine Reihe von Stream-Schnittstellen, die so breit sind wie DDR-Speicherchips auf Platinen, z. B. Alveo™ U200-, U250- und U280-Karten

Ausführliche Dokumentation finden Sie unter: 1-dimensionales (Linien)-Modul für SSR-FFT auf L1-FPGA und 2-dimensionales (Matrix)-Modul für SSR-FFT auf L1-FPGA.