- 概述

- 現在開始

數位訊號處理

AMD Vitis™ DSP 程式庫包含:

- L1、L2 和 L3 三種數位訊號處理層級

- AI 引擎 DSP 程式庫

- 可程式化邏輯 (PL) DSP 程式庫

Vitis AI 引擎 DSP 程式庫 - 主要功能

Vitis DSP 程式庫包含下列矩陣與向量運算函數

二進位加速碼

下載二進位加速碼至平台上

基準測試

提供基準測試和結果品質 (quality of results, QoR)

開放原始碼程式庫

適用於 DSP 應用的開放原始碼程式庫

範例設計

此程式庫提供範例設計

C++ 內核

內核使用熟悉的 C++ 語言編寫

複雜設計

合併內核以建構用於複雜設計的圖形

Vitis AI 引擎 DSP 程式庫 - 函數

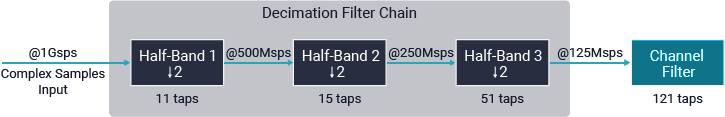

Vitis AI 引擎 DSP 程式庫是可配置的元素程式庫,能用於在 Versal® AI Engine 上的應用程式開發。這是用於 DSP 應用的開放原始碼程式庫。建議使用者要使用任一程式庫函數時,都先從有標示為進入點的 L2 層級圖形著手。每個進入點圖形都至少有一個 L1 層級內核,還可能包含不只一個圖形物件。不建議直接使用 L1 層級內核,或是其他未標識為進入點的任何圖形類別。

Vitis AI 引擎 DSP 程式庫內含下列 DSP 元素:

- 濾波器:

- 單取樣率有限脈衝響應 (finite impulse response, FIR)

- 半頻帶插值/降頻 FIR

- 整數和小數插值/降頻 FIR

- FFT/iFFT

- 單通道、分時法 (DIT) 實作

- 矩陣乘法

- 一般矩陣乘法

- 小工具 API 投射器

- 提供連接其他內核的靈活性

- 小工具實數資料轉複數資料

- 用於將實數資料轉換為複數資料或反向為之的公用程式

- DDS/混頻器

- 僅限直接數位合成的模式

- 混頻器

如需現有 DSP 函數的完整清單,請參閱 DSP 程式庫函數。

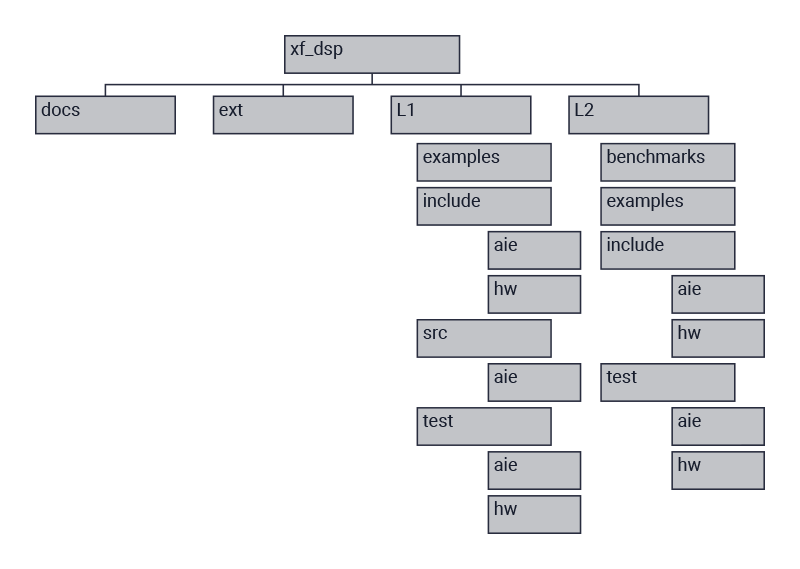

Vitis AI 引擎 DSP 程式庫 - 結構

Vitis AI 引擎 DSP 程式庫由各種最佳化 DSP 演算法構成,其用意是為了充分運用 Versal 器件處理能力,尤其是器件上的 AI 引擎陣列。

此程式庫分為三種 AI 引擎設計類型:

- L1 AI 引擎內核

- L2 AI 引擎圖形

- L3 軟體 API

附註:L3 尚未開放使用

Vitis 可程式化邏輯 (PL) DSP 程式庫 - 簡介

Vitis PL DSP 程式庫使用 FFT 演算法,在 AMD 賽靈思 FPGA 上加速實作離散傅立葉轉換。此程式庫包含三種類型的實作:

- L1 PL 基元

- L2 PL 內核

- L3 軟體 API

這些實作都整理在對應的 L1、L2 和 L3 類型硬體子目錄中。

| L1 PL 基元 | 可供開發人員用於硬體設計實作或設計硬體加速內核。特別適合硬體設計人員。 |

| L2 PL 內核 | 根據 HLS 產生的預先設計內核,可在 Vitis 執行階段程式庫的整合之下,直接用於不同應用的 FPGA 加速。 |

| L3 軟體 API | 以 C、C++ 和 Python 語言編寫,便於軟體開發人員將 FFT 計算工作卸載至 FPGA,以達加速之目的。 |

Vitis PL DSP 程式庫 - 函數

Vitis PL DSP 程式庫提供可完整合成的 PL 型 SSR FFT,以及一個二維版本的 FFT。

- 一維(直線)SSR FFT L1 FPGA 模組

- 提供採用脈動結構且可完整合成的 SSR FFT,進而在每個時脈週期,處理多個輸入樣本

- 透過 SSR 係數,提供各週期平行處理的樣本數控制功能

- 實作成為以合成串流架構為目標的 C++ 範本函數

- 可透過範本參數進行參數化

- 二維(矩陣)SSR FFT L1 FPGA 模組

- 以 L1 基元之形式,提供可完整合成的二維 FFT

- 可藉由新增記憶體轉接器,轉換為 L2 層級的 Vitis 環境內核

- 在設計上,其所具備的串流介面陣列,能夠與板卡器件的 DDR 記憶體寬度等寬,例如 Alveo™ U200、U250 和 U280 等卡

如需詳細說明文件,請參閱:一維(直線)SSR FFT L1 FPGA 模組和二維(矩陣)SSR FFT L1 FPGA 模組。