- 概要

- 利用開始

デジタル信号処理

AMD Vitis™ DSP ライブラリには、以下が含まれます。

- デジタル信号処理向け L1、L2、L3 レベル

- AI エンジン DSP ライブラリ

- プログラマブル ロジック (PL) DSP ライブラリ

Vitis AI エンジン DSP ライブラリ - 主な機能

Vitis BLAS ライブラリでは、次のような行列やベクトルの演算関数を提供しています。

アクセラレータ バイナリ

アクセラレータ バイナリをプラットフォームにダウンロード

ベンチマーク

ベンチマークと QoR (Quality of Results) を提供

オープンソース ライブラリ

DSP アプリケーション向けのオープンソース ライブラリ

サンプル デザイン

ライブラリにはサンプル デザインが付属

C++ で記述されたカーネル

カーネルは使い慣れた C++ で記述

複雑なデザイン

カーネルを組み合わせて複雑なデザインのグラフを構成

Vitis AI エンジン DSP ライブラリ - 関数

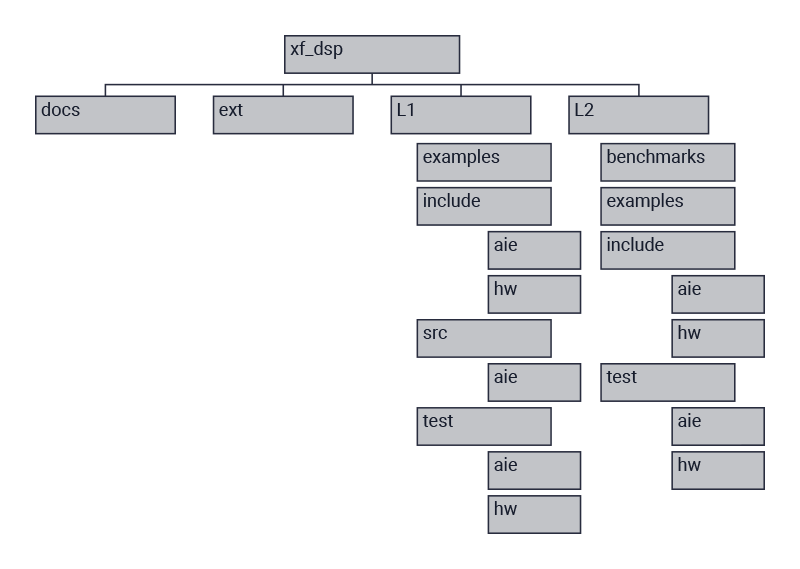

Vitis AI エンジン DSP ライブラリは、Versal® AI Engine ベースのアプリケーション開発に使用できる、コンフィギュレーション可能なエレメントのライブラリです。DSP アプリケーション用のオープンソース ライブラリです。各ライブラリ関数のユーザー エントリ ポイントは、L2 レベルのグラフです。各エントリ ポイントのグラフには、1 つ以上の L1 レベルのカーネルが含まれ、1 つ以上のグラフ オブジェクトを含めることができます。L1 レベルのカーネルや、エントリ ポイントとして認識されていないその他のグラフ クラスを直接使用することは推奨されていません。

Vitis AI エンジン DSP ライブラリは、次の DSP エレメントで構成されています。

- Filter:

- シングルレート FIR

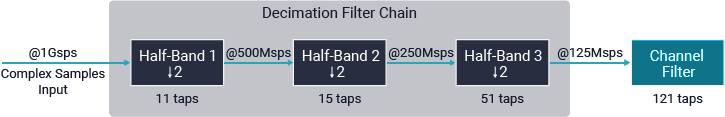

- ハーフバンド インターポレーション/デシメーション FIR

- 整数および分数インターポレーション/デシメーション FIR

- FFT/iFFT

- シングル カーネルの DIT (Decimation in Time) 実装

- Matrix Multiply

- 一般的な行列乗算

- Widget API Cast

- ほかのカーネルを接続する際の柔軟性を提供

- Widget Real to Complex

- 実数データから複素数データ (またはその逆) への変換ユーティリティ

- DDS/Mixer

- ダイレクト デジタル合成専用モード

- Mixer

利用できるすべての DSP 関数の一覧は、DSP ライブラリ関数を参照してください。

Vitis AI エンジン DSP ライブラリ - 構成

Vitis AI エンジン DSP ライブラリは、複数の AI エンジンを搭載した Versal デバイスの処理能力を最大限に活用するように最適化された DSP アルゴリズムを実装します。

このライブラリは、3 つの AI エンジン デザインに分かれています。

- L1 AI エンジン カーネル

- L2 AI エンジン グラフ

- L3 ソフトウェア API

注記: L3 は、まだ対応していません。

Vitis プログラマブル ロジック (PL) DSP ライブラリ - 概要

Vitis PL DSP ライブラリは、FFT アルゴリズムを使用して離散フーリエ変換を実装し、AMD ザイリンクスの FPGA デザインを高速化します。このライブラリは 3 つの実装で構成されています。

- L1 PL プリミティブ

- L2 PL カーネル

- L3 ソフトウェア API

これらの実装は、タイプ (L1、L2、L3) 別にハードウェア サブディレクトリ内で管理されます。

| L1 PL プリミティブ | ハードウェア デザインの実装、およびアクセラレーション用のハードウェア カーネル設計に携わる開発者が使用。特に、ハードウェア設計者の利用に最適。 |

| L2 PL カーネル | Vitis ランタイム ライブラリとの統合により、さまざまなアプリケーションの FPGA アクセラレーションに直接使用できる HLS ベースの設計済みカーネル。 |

| L3 ソフトウェア API | C、C++、Python で記述されており、ソフトウェア開発者は FFT の演算負荷を FPGA にオフロードして高速化できる。 |

Vitis PL DSP ライブラリ - 関数

Vitis PL DSP ライブラリは、2 次元 FFT バージョンと同様に、完全に合成可能な PL ベースの SSR FFT を提供します。

- 1 次元 (ライン) SSR FFT L1 FPGA モジュール

- 毎クロック サイクルで複数の入力サンプルを処理可能なシストリック アーキテクチャを含む完全に合成可能な SSR FFT を提供

- 各サイクルで並列で処理されるサンプル数は SSR 係数で表される

- ストリーミング アーキテクチャに合成される C++ テンプレート関数として実装

- テンプレート パラメーターでパラメーター指定可能

- 2 次元 (行列) SSR FFT L1 FPGA モジュール

- L1 プリミティブとして完全に合成可能な 2 次元 FFT を提供

- メモリ アダプターを追加して、L2 Vitis 環境のカーネルに変換

- Alveo™ U200、U250、U280 カードなどオンボード デバイスの DDR メモリと同じ幅のストリーム インターフェイスを備える

詳細は、1 次元 (ライン) SSR FFT L1 FPGA モジュールおよび 2 次元 (行列) SSR FFT L1 FPGA モジュールを参照してください。