- Visão geral

- Introdução

Processamento de sinal digital

A biblioteca de DSP do AMD Vitis™ contém:

- Níveis L1, L2 e L3 para processamento de sinal digital

- Biblioteca de DSP de mecanismo de IA

- Biblioteca de DSP de lógica programável (PL)

Biblioteca de DSP de AI Engine do Vitis — Principais recursos

A Biblioteca Vitis BLAS inclui as seguintes funções de operação de matriz e vetor

Binários do acelerador

Baixar binários do acelerador na plataforma

Avaliações de desempenho

Valores de referência e Qualidade dos resultados (QoR) são fornecidos

Biblioteca de código aberto

Biblioteca de código aberto para aplicativos de DSP

Exemplo de projeto

Um exemplo de projeto é fornecido com esta biblioteca

Kernels em C++

Os kernels são codificados em sua linguagem C++ conhecida

Projetos complexos

Combine kernels para construir grafos para projetos complexos

Biblioteca de DSP do Vitis AI Engine — Funções

A biblioteca de DSP do Vitis AI Engine é uma biblioteca configurável de elementos que pode ser usada para desenvolver aplicações nos mecanismos de IA do Versal®. Esta é uma biblioteca de código aberto para aplicativos de DSP. O ponto de entrada do usuário para cada função da biblioteca é um grafo de nível L2. Cada grafo de ponto de entrada conterá um ou mais kernels de nível L1 e pode conter um ou mais objetos de grafo. O uso direto de kernels de nível L1 ou qualquer outra classe de grafo não identificada como ponto de entrada não é recomendado.

A biblioteca de DSP do Vitis AI Engine consiste nos seguintes elementos de DSP:

- Filtros:

- FIRs de taxa única

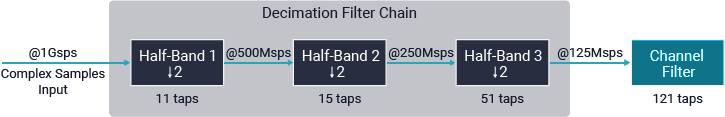

- FIRs de interpolação/decimação de meia-banda

- FIRs de interpolação/decimação de números inteiros e fracionários

- FFT/iFFT

- Implementação de um único canal, decimação no tempo (DIT)

- Multiplicação de matriz

- Multiplicação geral da matriz

- Widget API Cast

- Flexibilidade ao conectar outros kernels

- Widget real para complexo

- Utilitário para converter dados reais em complexos ou vice-versa

- DDS/Mixer

- Modo somente síntese digital direta

- Mixer

Para obter uma lista completa das funções de DSP disponíveis, consulte Funções da biblioteca de DSP.

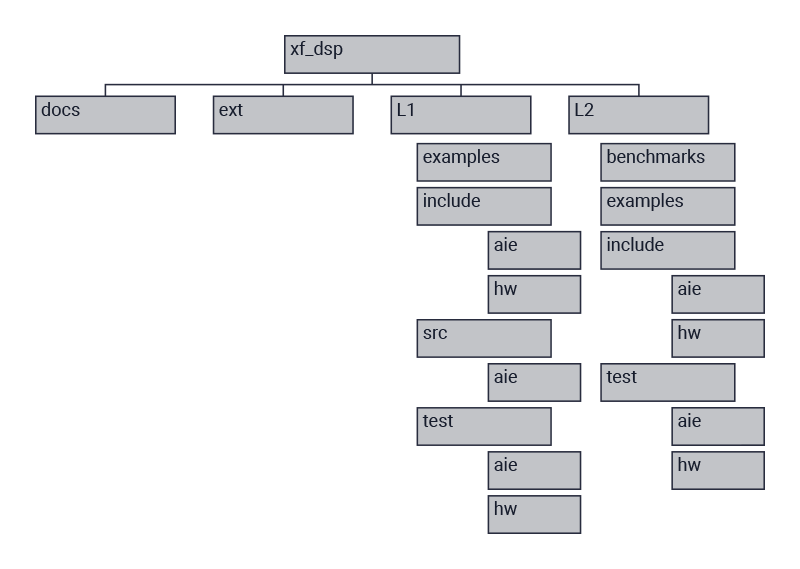

Biblioteca de DSP do Vitis AI Engine — Organização

A biblioteca de DSP do Vitis AI Engine consiste em algoritmos de DSP otimizados para aproveitar ao máximo o poder de processamento dos dispositivos Versal, que contêm uma variedade de mecanismos de IA.

A biblioteca é organizada em três tipos de projetos de mecanismo de IA:

- Kernels de mecanismo de IA L1

- Grafos de mecanismo de IA L2

- APIs de software L3

Nota: L3 ainda não está disponível

Biblioteca de DSP de lógica programável (PL) do Vitis — Introdução

A biblioteca de DSP de PL do Vitis implementa uma transformada de Fourier dedicada usando um algoritmo FFT para aceleração em FPGAs AMD Xilinx. A biblioteca consiste em três tipos de implementações:

- Primitivas de PL L1

- Kernels de PL L2

- APIs de software L3

Essas implementações são organizadas em subdiretórios de hardware dos tipos L1, L2 e L3 correspondentes.

| Primitivas de PL L1 | Pode ser usado por desenvolvedores que trabalham na implementação de projeto de hardware ou que projetam kernels de hardware para aceleração. Especialmente adequado para projetistas de hardware. |

| Kernels de PL L2 | Kernels pré-projetados baseados em HLS que podem ser usados diretamente para aceleração da FPGA de diferentes aplicativos na integração com a Biblioteca de tempo de execução do Vitis. |

| APIs de software L3 | Fornecidas em C, C++ e Python, que permitem que os desenvolvedores de software descarreguem o cálculo de FFT para FPGAs para aceleração. |

Biblioteca de DSP de PL do Vitis — Funções

A Biblioteca de DSP de PL do Vitis fornece um FFT SSR totalmente sintetizável baseado em PL, bem como uma versão FFT 2-dimensional.

- Módulo de FPGA L1 FFT SSR 1-dimensional (Linha)

- Fornece um FFT SSR totalmente sintetizável com uma arquitetura sistólica para processar várias amostras de entrada a cada ciclo do clock

- Permite o número de amostras processadas em paralelo por ciclo pelo fator SSR

- Implementa como uma função de modelo C++ que sintetiza em uma arquitetura de streaming

- Pode ser parametrizado por meio de parâmetros de modelo

- Módulo de FPGA L1 FFT SSR 2-dimensional (Matriz)

- Fornece um FFT 2-dimensional totalmente sintetizável como uma primitiva L1

- Transforma-se em um kernel do ambiente L2 do Vitis adicionando adaptadores de memória

- Projetado para ter uma variedade de interfaces de fluxo tão amplas quanto as larguras de memória DDR de dispositivo em placas, por exemplo, placas Alveo™ U200, U250 e U280

Para obter a documentação detalhada, consulte: Módulo de FPGA L1 FFT SSR 1-dimensional (Linha) e Módulo de FPGA L1 FFT SSR 2-dimensional (Matriz).