- 개요

- 시작하기

DSP(Digital Signal Processing)

AMD Vitis™ DSP 라이브러리에는 다음이 포함되어 있습니다.

- DSP(Digital Signal Processing)를 위한 L1, L2 및 L3 레벨

- AI 엔진 DSP 라이브러리

- PL(프로그래밍 가능 로직) DSP 라이브러리

Vitis AI Engine DSP 라이브러리 - 주요 기능

Vitis BLAS 라이브러리에는 다음과 같은 행렬 및 벡터 연산 함수가 포함되어 있습니다.

가속기 바이너리

플랫폼에 가속기 바이너리 다운로드

벤치마크

벤치마크 및 QoR(Quality of Results) 제공

오픈 소스 라이브러리

DSP 애플리케이션용 오픈 소스 라이브러리

예제 설계

이 라이브러리에는 예제 설계가 제공됩니다.

C++로 작성된 커널

커널은 익숙한 C++로 코딩됩니다.

복잡한 설계

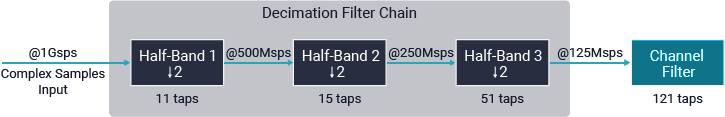

커널을 결합하여 복잡한 설계를 위한 그래프 작성

Vitis AI Engine DSP 라이브러리 - 함수

Vitis AI Engine DSP 라이브러리는 Versal® AI Engine에서 애플리케이션을 개발하는 데 사용할 수 있는 요소의 구성 가능한 라이브러리입니다. 이 라이브러리는 DSP 애플리케이션용 오픈 소스 라이브러리입니다. 각 라이브러리 함수의 사용자 진입점은 L2 레벨 그래프입니다. 각 진입점 그래프에는 하나 이상의 L1 레벨 커널이 포함되며 하나 이상의 그래프 객체가 포함될 수 있습니다. L1 레벨의 커널이나 진입점으로 식별되지 않은 다른 그래프 클래스를 직접 사용하는 것은 권장되지 않습니다.

Vitis AI Engine DSP 라이브러리는 다음과 같은 DSP 요소로 구성됩니다.

- 필터:

- 단일 속도 FIR

- 반대역 보간/데시메이션 FIR

- 정수 및 분수 보간/데시메이션 FIR

- FFT/iFFT

- 단일 채널, DIT(Decimation in Time) 구현

- 행렬곱

- 일반 행렬곱

- 위젯 API 캐스트

- 다른 커널 연결 시 유연성

- 실수-복소수 위젯

- 실수 데이터를 복소수 데이터로 또는 그 반대로 변환하는 유틸리티

- DDS/믹서

- 직접 디지털 합성 전용 모드

- 믹서

사용 가능한 DSP 함수의 전체 목록은 DSP 라이브러리 함수를 참조하세요.

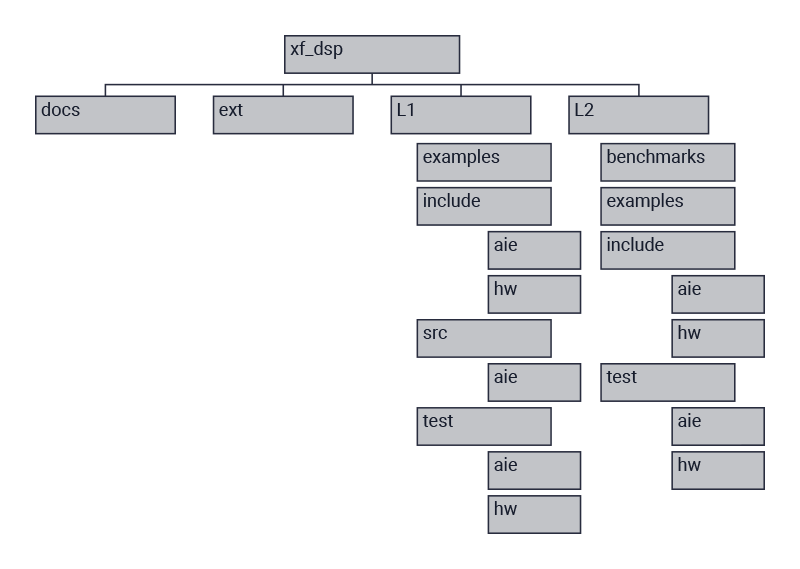

Vitis AI Engine DSP 라이브러리 - 구성

Vitis AI Engine DSP 라이브러리는 AI 엔진 어레이를 포함하는 Versal 디바이스의 프로세싱 파워를 최대한 활용하도록 최적화된 DSP 알고리즘으로 구성되어 있습니다.

이 라이브러리는 세 가지 유형의 AI 엔진 설계로 구성됩니다.

- L1 AI 엔진 커널

- L2 AI 엔진 그래프

- L3 소프트웨어 API

참고: L3는 아직 제공되지 않습니다.

Vitis PL(프로그래밍 가능 로직) DSP 라이브러리 - 소개

Vitis PL DSP 라이브러리는 AMD Xilinx FPGA에서 가속을 위해 FFT 알고리즘을 사용하여 이산 푸리에 변환을 구현합니다. 라이브러리는 세 가지 유형의 구현으로 구성됩니다.

- L1 PL 프리미티브

- L2 PL 커널

- L3 소프트웨어 API

이러한 구현은 해당 L1, L2 및 L3 유형의 하드웨어 하위 디렉토리로 구성됩니다.

| L1 PL 프리미티브 | 하드웨어 설계 구현을 수행하거나 가속을 위해 하드웨어 커널을 설계하는 개발자가 활용할 수 있습니다. 특히 하드웨어 설계자에게 적합합니다. |

| L2 PL 커널 | Vitis 런타임 라이브러리와의 통합에서 다양한 애플리케이션의 FPGA 가속에 직접 사용할 수 있는 HLS 기반의 사전 설계된 커널입니다. |

| L3 소프트웨어 API | C, C++ 및 Python으로 제공되며, 이를 통해 소프트웨어 개발자는 가속을 위해 FFT 계산을 FPGA로 오프로드할 수 있습니다. |

Vitis PL DSP 라이브러리 - 함수

Vitis PL DSP 라이브러리는 2차원 FFT 버전뿐만 아니라 완전히 합성 가능한 PL 기반 SSR FFT도 제공합니다.

- 1차원(라인) SSR FFT L1 FPGA 모듈

- 클럭 주기마다 여러 입력 샘플을 처리하기 위한 수축 아키텍처를 갖춘 완전히 합성 가능한 SSR FFT를 제공합니다.

- SSR 인수로 주기당 병렬 처리되는 샘플 수를 활성화합니다.

- 스트리밍 아키텍처로 합성되는 C++ 템플릿 함수로 구현합니다.

- 템플릿 파라미터를 통해 파라미터화될 수 있습니다.

- 2차원(행렬) SSR FFT L1 FPGA 모듈

- 완전히 합성 가능한 2차원 FFT를 L1 프리미티브로 제공합니다.

- 메모리 어댑터를 추가하여 L2 Vitis 환경 커널로 변환합니다.

- 보드의 디바이스 DDR 메모리 폭만큼 넓은 스트림 인터페이스 어레이를 갖도록 설계되었습니다(예: Alveo™ U200, U250, U280 카드).

자세한 문서는 1차원(라인) SSR FFT L1 FPGA 모듈 및 2차원(행렬) SSR FFT L1 FPGA 모듈을 참조하세요.