- Présentation

- Introduction

Traitement de signalétique numérique

La bibliothèque AMD Vitis™ DSP contient :

- Niveaux L1, L2 et L3 pour le traitement de signal numérique

- Bibliothèque DSP AI Engine

- Bibliothèque DSP Programmable Logic (PL)

Bibliothèque DSP Vitis AI Engine - Principales fonctionnalités

La bibliothèque Vitis BLAS comprend les fonctions de fonctionnement de matrice et de vecteur suivantes

Binaires d'accélération

Télécharger les binaires d'accélération sur la plateforme

Benchmarks

Les benchmarks et la qualité des résultats (QoR) sont fournis

Bibliothèque open source

Bibliothèque open source pour les applications DSP

Exemple de conception

Cette bibliothèque contient un exemple de conception

Noyaux en C++

Les noyaux sont codés dans votre langage de programmation C++ habituel

Conceptions complexes

Combinez les noyaux pour construire des graphiques pour des conceptions complexes

Bibliothèque DSP Vitis AI Engine - Fonctions

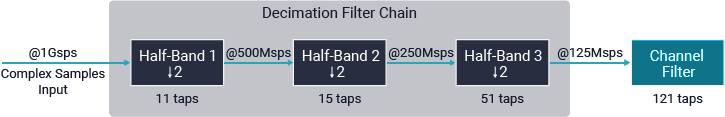

La bibliothèque DSP AI Engine Vitis est une bibliothèque configurable d'éléments qui peut être utilisée pour développer des applications sur les Versal® AI Engines. Il s'agit d'une bibliothèque open source pour les applications DSP. Le point d'entrée utilisateur de chaque fonction de bibliothèque est un graphe de niveau L2. Chaque graphique de point d'entrée contient un ou plusieurs noyaux de niveau L1 et peut contenir un ou plusieurs objets graphiques. L'utilisation directe de noyaux de niveau L1 ou de toute autre classe de graphique non identifiée comme point d'entrée n'est pas recommandée.

La bibliothèque Vitis AI Engine DSP se compose des éléments DSP suivants :

- Filtres :

- FIR à taux unique

- Interpolation/décimation de FIR à demi-bande

- FIR d'interpolation/décimation entiers et fractionnels

- FFT/iFFT

- Mise en œuvre de DIT (Decimation In Time) à canal unique

- Multiplication de matrice

- Multiplication de matrice générale

- Diffusion d'API de widget

- Flexibilité lors de la connexion d'autres noyaux

- Widget réel à complexe

- Utilitaire permettant de convertir des données réelles en données complexes et vice versa

- DDS/mélangeur

- Mode de synthèse numérique directe uniquement

- Mélangeur

Pour obtenir la liste complète des fonctions DSP disponibles, reportez-vous à la section Fonctions de la bibliothèque DSP.

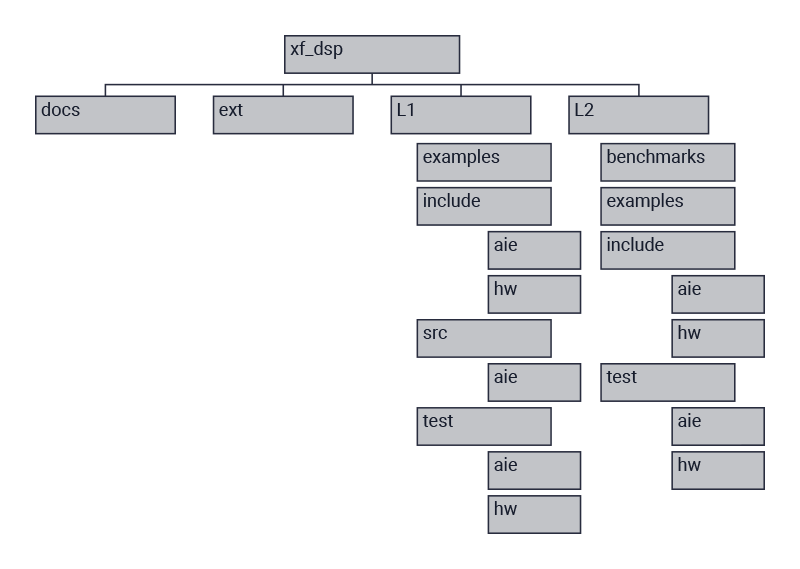

Bibliothèque Vitis AI Engine DSP - Organisation

La bibliothèque DSP Vitis AI Engine se compose d'algorithmes DSP optimisés pour tirer pleinement parti de la puissance de traitement des appareils Versal, qui contiennent une gamme d'AI Engines.

La bibliothèque est organisée en trois types de conceptions AI Engine :

- Noyaux L1 AI Engine

- Graphiques L2 AI Engine

- API software L3

Remarque : L3 n'est pas encore disponible

Bibliothèque DSP Vitis Programmable Logic (PL) - Introduction

La bibliothèque DSP Vitis PL met en œuvre une transformation de Fourier discrète à l'aide d'un algorithme FFT pour l'accélération sur les FPGA AMD Xilinx. La bibliothèque se compose de trois types de mises en œuvre :

- Primitives L1 PL

- Noyaux L2 PL

- API software L3

Ces mises en œuvre sont organisées en sous-répertoires hardware des types L1, L2 et L3 correspondants.

| Primitives L1 PL | Peut être exploité par les développeurs travaillant sur la mise en œuvre de la conception hardware ou la conception de noyaux hardware pour l'accélération. Particulièrement adapté aux concepteurs de hardware. |

| Noyaux L2 PL | Noyaux préconçus basés sur HLS qui peuvent être directement utilisés pour l'accélération FPGA de différentes applications lors de l'intégration avec Vitis Runtime Library. |

| API software L3 | Fournis en C, C++ et Python, qui permettent aux développeurs de software de décharger le calcul FFT vers les FPGA pour l'accélération. |

Bibliothèque Vitis PL DSP - Fonctions

La bibliothèque DSP Vitis PL fournit une FFT SSR basée sur PL entièrement synthétisable ainsi qu'une version FFT en 2 dimensions.

- Module FPGA FFT L1 SSR 1 dimension (ligne)

- Fournit une FFT SSR entièrement synthétisable avec une architecture systolique pour traiter plusieurs échantillons d'entrée à chaque cycle d'horloge

- Active le nombre d'échantillons traités en parallèle par cycle par le facteur SSR

- Mise en œuvre sous forme de fonction de modèle C++ qui synthétise dans une architecture de streaming

- Peut être paramétré à l'aide des paramètres de modèle

- Module FPGA FFT L1 SSR 2 dimensions (matrice)

- Fournit une FFT 2 dimensions entièrement synthétisable en tant que primitive L1

- Se transforme en noyau d'environnement L2 Vitis en ajoutant des adaptateurs mémoire

- Conçu pour disposer d'une gamme d'interfaces de flux aussi large que les mémoires DDR sur les cartes, par exemple, les cartes Alveo™ U200, U250 et U280

Pour obtenir une documentation détaillée, reportez-vous à : Module FPGA FFT L1 SSR 1 dimension (ligne) et module FPGA FFT L1 SSR 2 dimensions (matrice).