- 概观

- 开始体验

数字信号处理

AMD Vitis™ DSP 库包含:

- 数字信号处理的 L1、L2 和 L3 层级

- AI 引擎 DSP 库

- 可编程逻辑 (PL) DSP 库

Vitis AI Engine DSP 库 - 主要特性

Vitis BLAS 库包含以下矩阵及矢量运算函数

加速器二进制文件

将加速器二进制文件下载到平台上

基准测试

提供基准测试和结果质量 (QoR)

开源库

DSP 应用的开源库

设计示例

该库提供一个示例设计

用 C++ 编码的内核

内核是用您熟悉的 C++ 编码的

复杂设计

结合内核构造复杂设计的图

Vitis AI Engine DSP 库 - 函数

Vitis AI Engine DSP 库是一个可配置的元件库,可用于通过 Versal® AI Engine 开发应用。这是 DSP 应用的开源库。每个库函数的用户入口点都是一个 L2 层级图。每个入口点图都将包含一个或多个 L1 层级内核,而且可能包含一个或多个图对象。不建议直接使用 L1 层级内核或任何未确定为入口点的其他图类。

Vitis AI Engine DSP 库包含以下 DSP 元件:

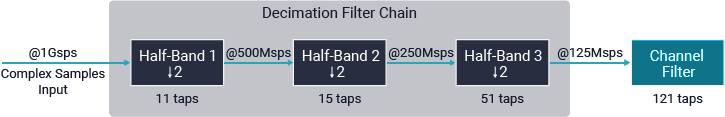

- 滤波器:

- 单一速率 FIR

- 半带内插/抽取 FIR

- 整数及分数内插/抽取 FIR

- FFT/iFFT

- 单通道时域抽取 (DIT) 实现

- 矩阵乘法

- 一般矩阵乘法

- Widget API 类型转换

- 连接其他内核时的灵活性

- widget 实数到复数转换

- 用于将实数数据转换为复数数据(或反之)的实用工具

- DDS/混频器

- 仅直接数字综合模式

- 混频器

有关可用 DSP 函数的完整列表,请参阅 DSP 库函数。

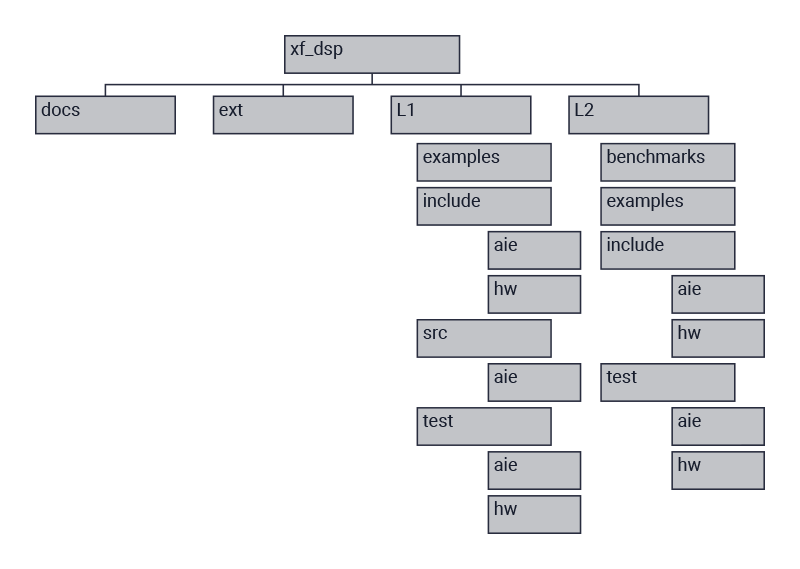

Vitis AI Engine DSP 库 - 组织结构

Vitis AI Engine DSP 库由经过优化的 DSP 算法组成,可充分利用 Versal 器件的处理能力,其中包含一系列 AI 引擎。

该库分为三种类型的 AI 引擎设计:

- L1 AI 引擎内核

- L2 AI 引擎图

- L3 软件 API

注意:L3 尚不可用

Vitis 可编程逻辑 (PL) DSP 库 - 介绍

Vitis PL DSP 库使用 FFT 算法实现离散傅立叶变换,以便在 AMD Xilinx FPGA 上加速。该库有三种类型的实现方案:

- L1 PL 原语

- L2 PL 内核

- L3 软件 API

这些实现方案分别位于相应的 L1、L2 及 L3 类硬件子目录下。

| L1 PL 原语 | 可供从事硬件设计实施或设计硬件内核以实现加速的开发者使用。特别适合硬件设计人员。 |

| L2 PL 内核 | 基于 HLS 预先设计的内核,可直接用于为与 Vitis 运行时库集成的不同应用执行 FPGA 加速。 |

| L3 软件 API | 采用 C、C++ 和 Python 提供,可让软件开发者将 FFT 计算交由 FPGA 完成,以实现加速。 |

Vitis PL DSP 库 - 函数

Vitis PL DSP 库不仅提供一个完全可综合的、基于 PL 的 SSR FFT,而且还提供一个二维 FFT 版本。

- 一维(线性)SSR FFT L1 FPGA 模块

- 提供完全合成的 SSR FFT,具有脉动架构,可在每个时钟周期处理多个输入样本

- 每个周期内并行处理的样本数量以 SSR 因子来表示

- 按照 C++ 模板函数执行,其可合成一个串流架构

- 可通过模板参数进行参数化

- 二维(矩阵)SSR FFT L1 FPGA 模块

- 提供完全合成的二维 FFT 作为 L1 原语

- 通过添加内存适配器转换为 L2 Vitis 环境内核

- 旨在在电路板上提供一列列与器件 DDR 内存位宽一样的串流接口,例如 Alveo™ U200、U250 和 U280 卡

有关详细文档,请参阅:一维(线性)SSR FFT L1 FPGA 模块和二维(矩阵)SSR FFT L1 FPGA 模块。