Funciones y capacidades de ChipScope

Muchos problemas de hardware solo se hacen evidentes cuando el sistema completo e integrado se ejecuta en tiempo real. Vivado ChipScope ofrece un flujo integral a fin de maximizar la visibilidad de la lógica programable para la depuración de diseño durante el funcionamiento del sistema.

Visibilidad de diseño

Escala a cientos de nodos internos para tener una vista clara sobre cómo funciona internamente tu diseño.

Análisis en detalle

Implementa condiciones de activación complejas y realiza análisis en diversas perspectivas del diseño.

Cambios de depuración rápidos

Aprovecha los flujos de compilación incrementales para una iteración rápida y Python™ a fin de automatizar tareas.

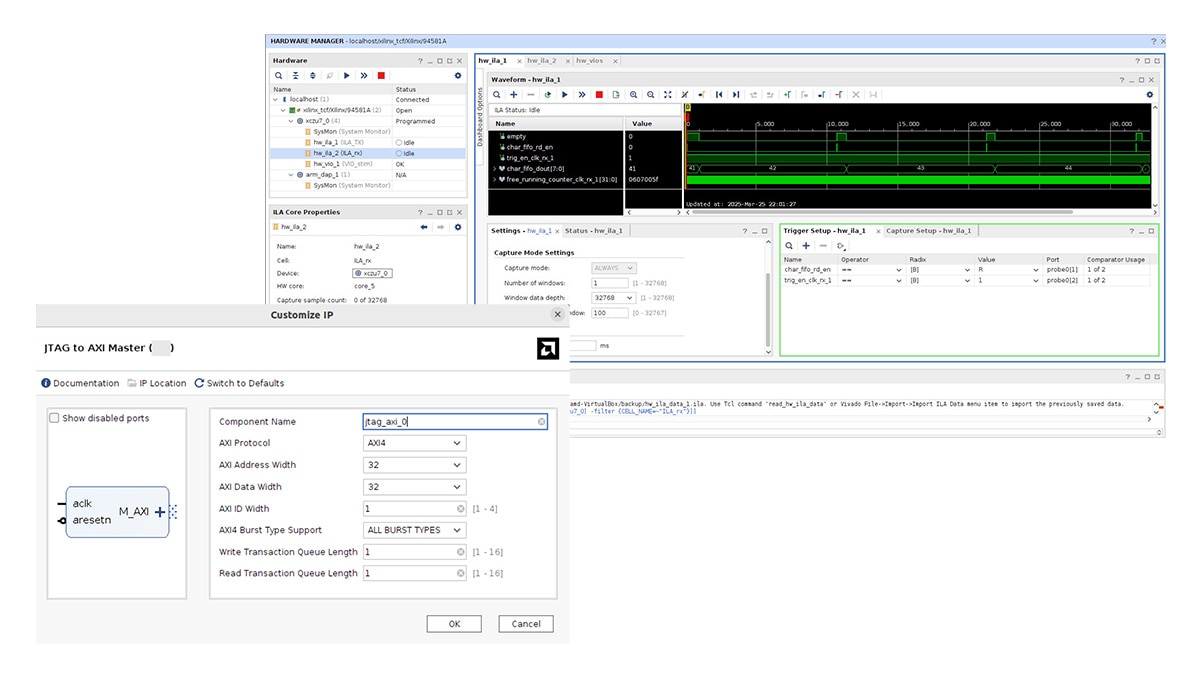

AMD Vivado™ ChipScope Analyzer

En este video, se ofrece una visión general práctica de cómo implementar y usar ChipScope para la depuración de hardware. Abarca el proceso de integración del analizador lógico interno y los núcleos de depuración en la lógica programable, la configuración de activadores y el análisis de datos recopilados para identificar y resolver problemas rápidamente.

Depuración de hardware paso a paso con Adam Taylor

Aprende a depurar hardware en sistemas reales con Vivado ChipScope en dos tutoriales distintos para dispositivos AMD Versal™ y UltraScale+™, realizados por Adam Taylor. En cada guía, se resalta la metodología de depuración, se demuestra cómo instrumentar diseños de manera eficaz y se incluyen proyectos descargables que puedes ejecutar y estudiar.

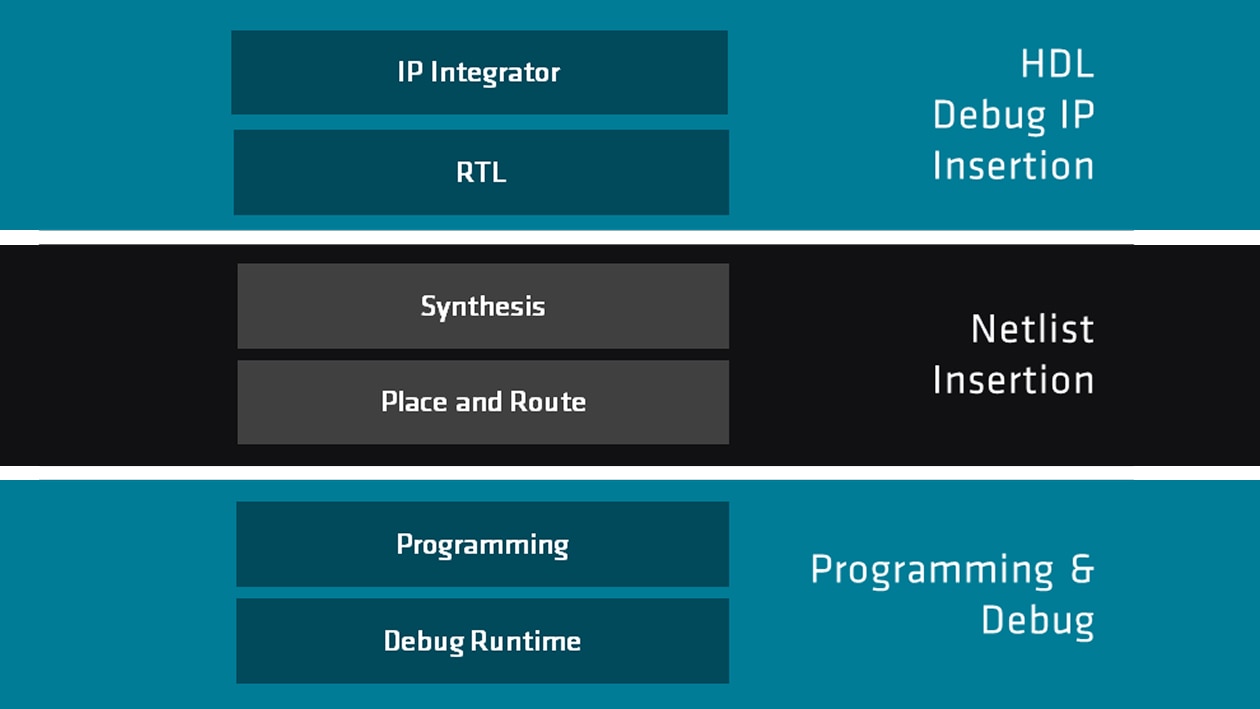

Flujo de depuración integral

Metodologías flexibles para la instrumentación de depuración de IP, análisis de diseño, configuración de tiempo de ejecución y compilación incremental para cambios de depuración rápidos.

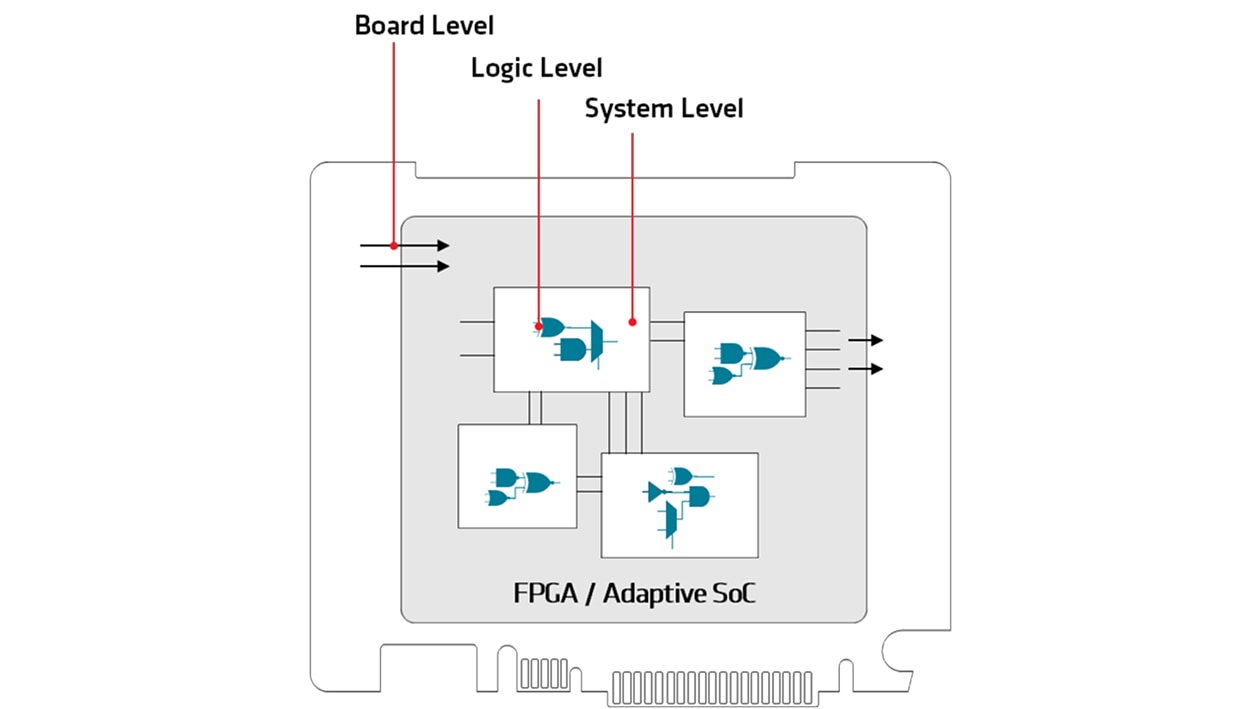

Visibilidad del sistema

ChipScope proporciona varios niveles de abstracción para analizar el sistema con un conjunto integral de IP a fin de maximizar la visibilidad.

- Depuración de nivel lógico: los núcleos de ILA (Integrated Logic Analyzer, analizador lógico integrado) proporcionan un activador avanzado de señales internas y funciones de recopilación para solucionar problemas en tiempo real.

- Depuración de nivel de sistema: compatibilidad para interfaces AXI y protocolos de E/S, lo que permite la inspección a nivel de transacción en los bloques de diseño.

- Depuración de nivel de placa: analiza la interacción de nivel de placa con núcleos de E/S virtuales (VIO), lo que permite el monitoreo de la señal y la inyección de valores de prueba para examinar el comportamiento del diseño.

IP de depuración

Es esencial para la composición del flujo de depuración, ya que es un conjunto de núcleos de IP que permite la visibilidad del diseño sin obstruir la funcionalidad de este. Toda la IP de depuración de AMD está disponible en línea, y también en el catálogo de IP de Vivado Design Suite. Ten en cuenta que la depuración lógica programable para los SoC adaptables de Versal™ está estrictamente basada en AXI.

SoC adaptables de FPGA y Zynq™ |

SoC adaptables de AMD Versal |

|

Integrated Logic Analyzer (ILA) |

||

Sistema ILA |

||

Entrada/Salida Virtual VIO |

||

Convertidor BSCAN a JTAG |

- |

|

Debug Hub* |

Bus de depuración del sistema (XSDB): integrado |

* Debug Hub facilita la comunicación con los núcleos IP de depuración a través de JTAG

Módulos de cable de datos

AMD ofrece una gama de cables de datos para la depuración JTAG estándar y la depuración de alta velocidad de sistemas heterogéneos. Sin importar si tu prioridad es recopilar grandes volúmenes de datos, minimizar la utilización de recursos del dispositivo o lograr un rendimiento de depuración más rápido, la elección de un cable de datos adecuado puede incidir en la eficiencia de tu flujo de trabajo.

Además de los módulos de cable de datos, la mayoría de los kits de evaluación ofrecen interfaces de depuración USB a JTAG integradas y las familias de dispositivos determinadas ofrecen depuración a través de Ethernet o PCI-Express®. Obtén más información sobre los módulos de cable de datos a continuación.

| Compatibilidad de dispositivos | USB para el cable de plataforma II | SmartLynq | SmartLynq+ |

|---|---|---|---|

| FPGA de AMD | ✓ | ✓ | |

| SoC adaptables Zynq | ✓ | ✓ | |

| SoC adaptables a Versal | ✓ | ✓ |

Análisis de diseño

ChipScope proporciona varias interfaces y métodos de automatización para el seguimiento y la depuración dentro del sistema. Dentro del IDE de Vivado, los diseñadores pueden navegar sin interrupciones entre formas de onda de alto nivel y elementos de diseño, como también automatizar la interacción a través de TCL o Python.

- Activación compleja: establece activadores de varios niveles con dependencias basadas en el estado para reproducir situaciones de diseño complejas.

- Sondeo cruzado: es la capacidad de sondear de forma cruzada desde la salida de depuración hasta el RTL o la lista de conexiones para analizar e identificar el caso raíz de los errores de diseño.

- Análisis en forma de onda: indica las transiciones de señal capturadas, lo que permite registrar la información del activador con la capacidad de hacer un seguimiento hasta la fuente de diseño.

- Depuración de protocolo: análisis específico del protocolo con plazos de transacción para identificar cuellos de botella y sondeo cruzado de eventos de protocolo a RTL.

- Interfaz VIO: impulsa las señales para la prueba interactiva y monitorea sin detener o reprogramar el diseño.

Cambios de depuración rápidos

Flujos incrementales

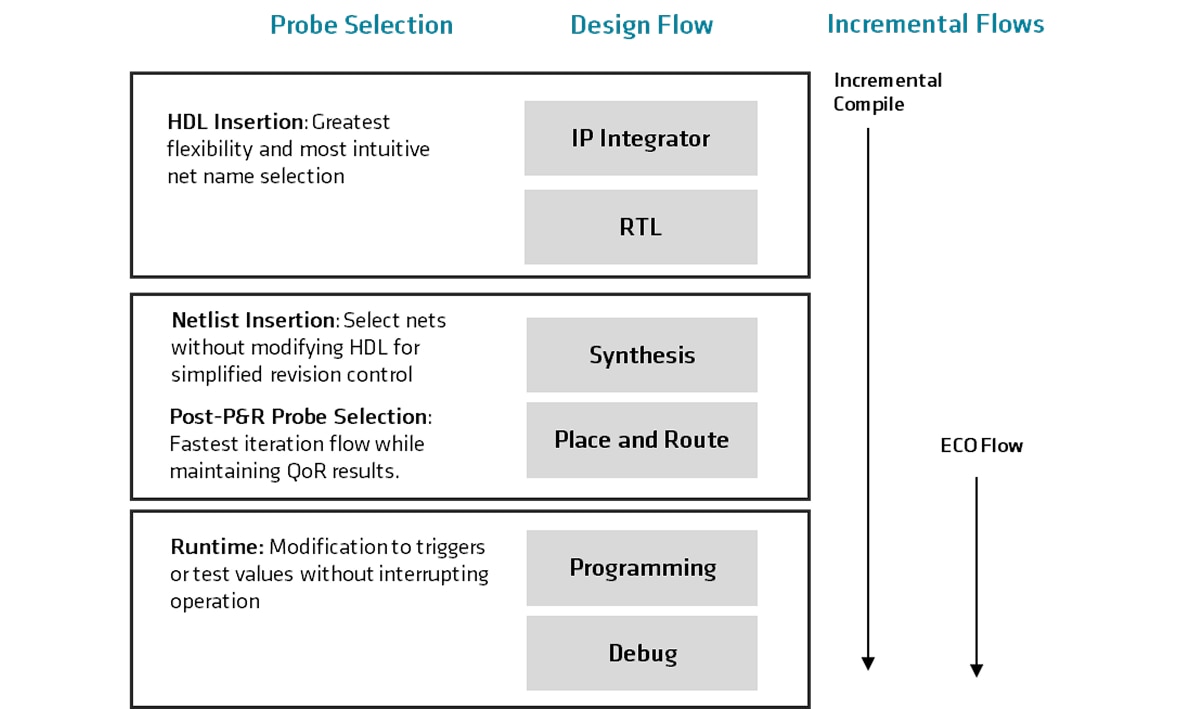

La modificación del activador, de las sondas y de los núcleos de depuración es inevitable a medida que se descubren errores, lo que hace que la iteración rápida sea fundamental. ChipScope aprovecha los varios tipos de flujos de compilación incrementales para modificar solo las partes cambiadas del diseño, lo que evita que se tenga que rediseñar por completo durante los ciclos de depuración.

Varios flujos incrementales están disponibles según el método de instrumentación de depuración:

- Compilación incremental: Realiza la síntesis y ubicación y enrutamiento de las partes cambiadas del diseño

- Flujo ECO (Engineering Change Order, orden de cambio de ingeniería): para la selección de sondas posterior a la ubicación y enrutamiento, lo que es ideal para cambios menores y es la forma más rápida de iterar con la máxima preservación del diseño

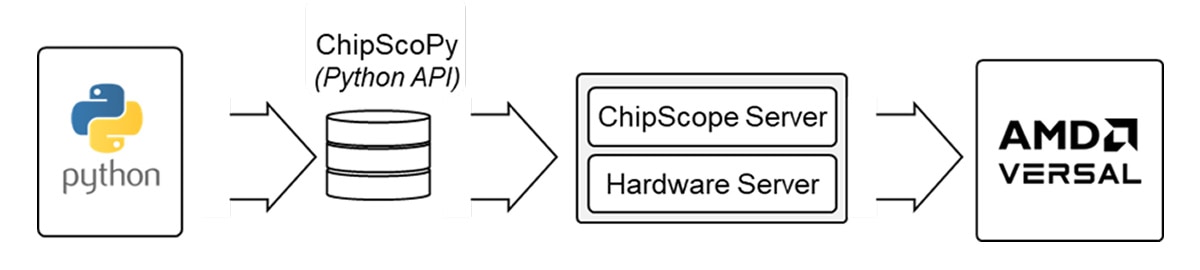

ChipScoPy: API de Python para la automatización

Para los dispositivos Versal, ChipScoPy es una interfaz Python sencilla para automatizar las capacidades de ChipScope sin la necesidad del IDE de Vivado, lo que permite una mayor automatización de depuración y control para la lógica programable y varias IP duras.

Entre las ventajas, se incluyen las siguientes:

- Flujo flexible y personalizable por el usuario que se puede programar completamente

- Flujo extensible que puede usar paquetes de terceros y de código abierto, como el visualizador de trazados

- Proceso simple de instalación, ya que la instalación de la herramienta de Vivado no es necesaria