Recursos e capacidades do ChipScope

Muitos problemas de hardware só ficam aparentes quando o sistema completo e integrado está sendo executado em tempo real. O Vivado ChipScope fornece um fluxo abrangente para maximizar a visibilidade da lógica programável para depuração do projeto durante a operação do sistema.

Visibilidade do projeto

Dimensione para centenas de nós internos para obter uma visão clara do funcionamento interno do seu projeto.

Análise detalhada

Implemente condições de acionamento complexas e analise em várias visualizações do projeto.

Turnos rápidos de depuração

Aproveite os fluxos de compilação incremental para iteração rápida e o Python™ para automatizar tarefas.

AMD Vivado™ ChipScope Analyzer

Este vídeo oferece uma visão geral prática de como implementar e usar o ChipScope para depuração de hardware. Ele abrange o processo de integração do analisador lógico interno e dos núcleos de depuração na lógica programável, a configuração de acionadores e a análise de dados capturados para identificar e resolver problemas rapidamente.

Depuração de hardware passo a passo com Adam Taylor

Aprenda a depurar hardware em sistemas reais usando o Vivado ChipScope em dois tutoriais distintos para os dispositivos AMD Versal™ e UltraScale+™, criados por Adam Taylor. Cada tutorial enfatiza a metodologia de depuração, mostra como instrumentar projetos com eficiência e inclui projetos para download que você pode executar e explorar.

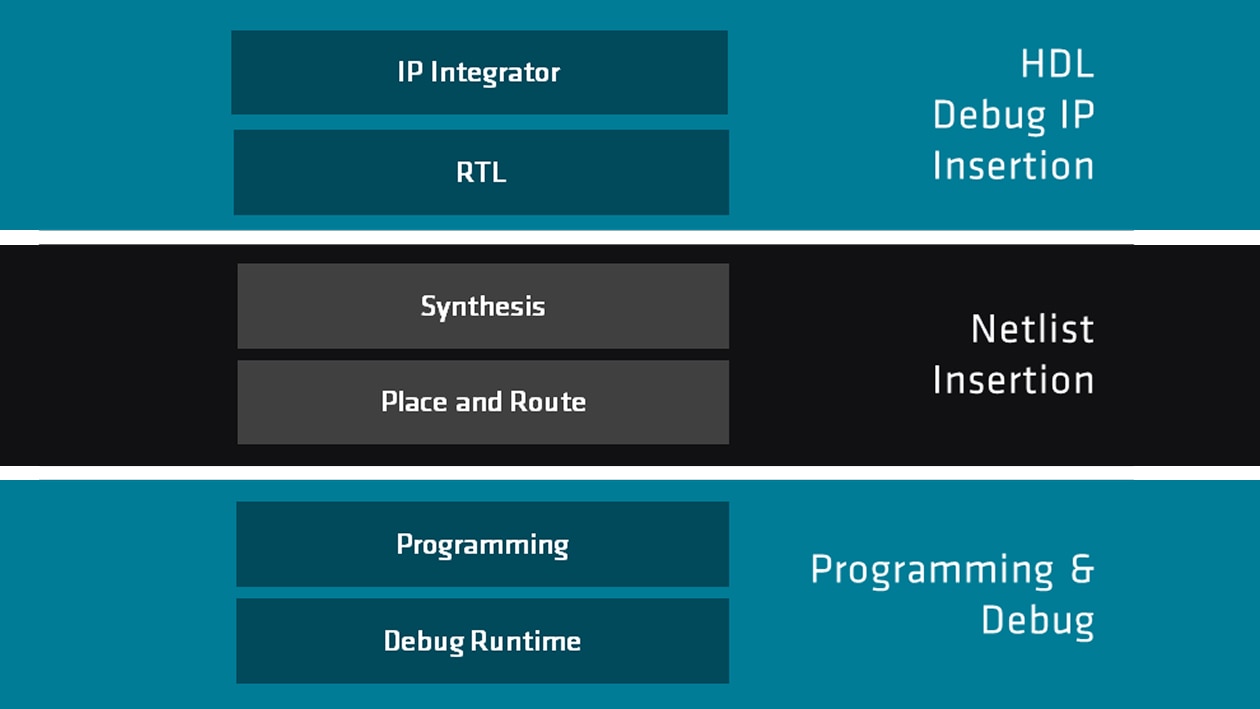

Fluxo de depuração abrangente

Metodologias flexíveis para depuração de instrumentação IP, análises de projeto, configuração de tempo de execução e compilação incremental para turnos rápidos de depuração.

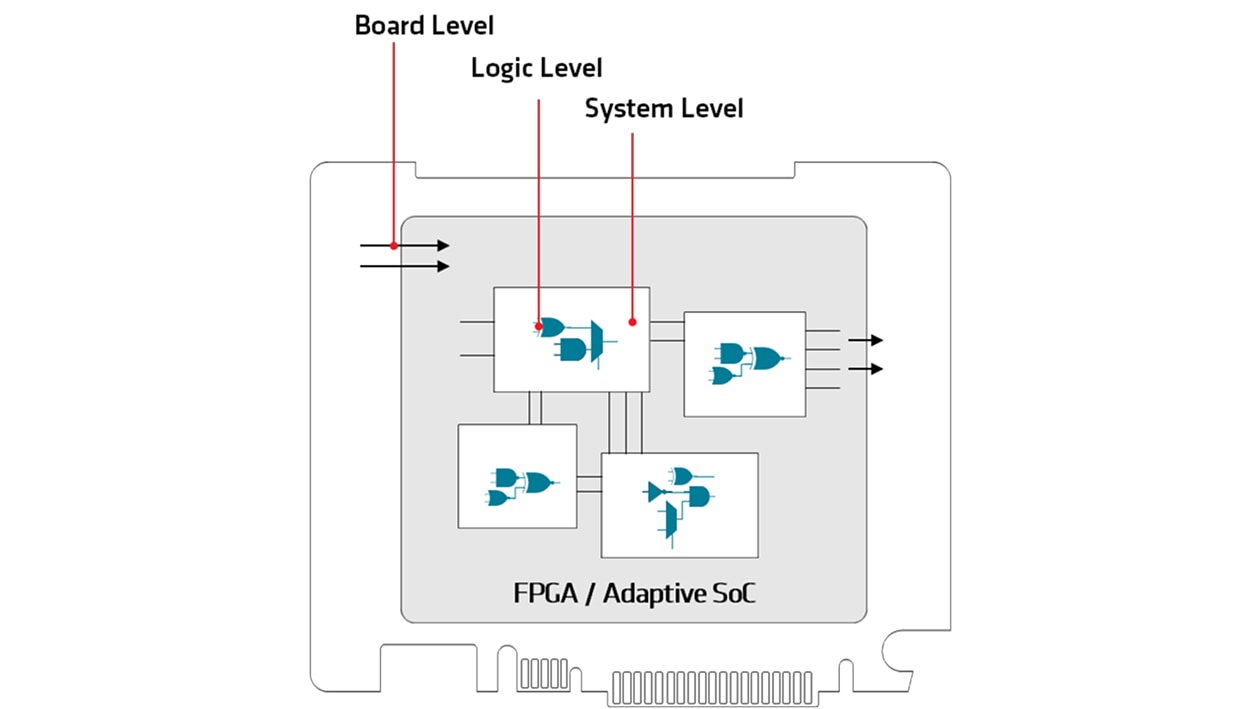

Visibilidade do sistema

O ChipScope fornece vários níveis de abstração para analisar seu sistema com um conjunto abrangente de IP para maximizar a visibilidade.

- Depuração no nível lógico: os núcleos do Integrated Logic Analyzer (ILA) fornecem acionamento avançado de sinais internos e recursos de captura para solucionar erros em tempo real.

- Depuração no nível do sistema: suporte para interfaces AXI e protocolos de E/S, permitindo a inspeção no nível da transação entre blocos de projeto.

- Depuração no nível da placa: explore a interação no nível da placa com núcleos de VIO (Virtual I/O, E/S virtual), permitindo o monitoramento de sinal e injetando valores de teste para examinar o comportamento do projeto.

IP de depuração

Essencial para o fluxo de depuração do fabric, é um conjunto de núcleos de IP para permitir a visibilidade do projeto sem obstruir a funcionalidade dele. Todos os IPs de depuração da AMD estão disponíveis on-line e também no catálogo de IPs no Vivado Design Suite. Observe que a depuração lógica programável para SoCs adaptativos Versal™ é estritamente baseada em AXI.

FPGAs e SoCs adaptativos Zynq™ |

SoCs adaptativos AMD Versal |

|

Integrated Logic Analyzer (ILA) |

||

ILA do sistema |

||

Entrada/Saída virtual (VIO) |

||

Conversor de BSCAN para JTAG |

- |

|

Hub de depuração* |

Barramento de depuração do sistema (XSDB) – incorporado |

*O Hub de depuração facilita a comunicação com os núcleos de IP de depuração por meio do JTAG

Módulos de cabos de dados

A AMD oferece uma variedade de cabos de dados para depuração JTAG padrão e depuração de alta velocidade de sistemas heterogêneos. Se sua prioridade for capturar grandes volumes de dados, minimizar a utilização de recursos do dispositivo ou alcançar um desempenho de depuração mais rápido, escolher o cabo de dados certo pode afetar a eficiência do seu fluxo de trabalho.

Além dos módulos de cabos de dados, a maioria dos kits de avaliação oferece interfaces de depuração USB para JTAG incorporadas e determinadas famílias de dispositivos oferecem depuração via Ethernet ou PCI-Express®. Saiba mais sobre os módulos de cabos de dados abaixo.

| Suporte ao dispositivo | Cabo de plataforma USB II | SmartLynq | SmartLynq+ |

|---|---|---|---|

| AMD FPGAs | ✓ | ✓ | |

| SoCs adaptativos Zynq | ✓ | ✓ | |

| SoCs adaptativos Versal | ✓ | ✓ |

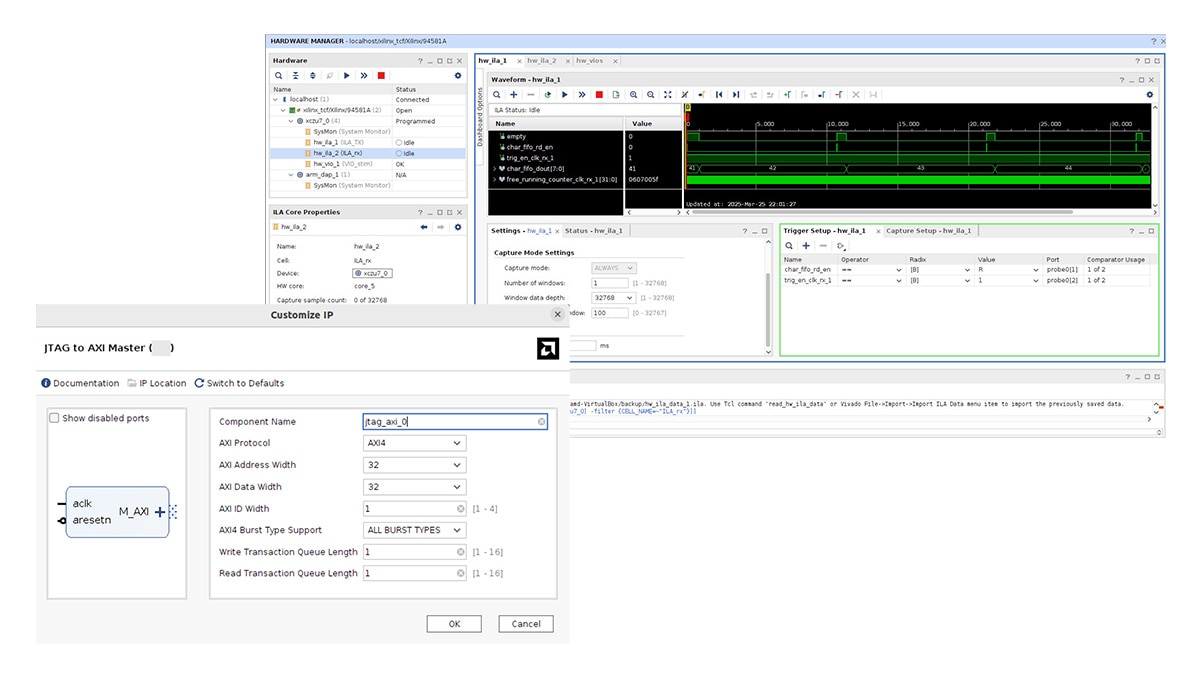

Análise de projetos

O ChipScope fornece várias interfaces e métodos de automação para depuração e rastreamento no sistema. No Vivado IDE, os projetistas podem navegar facilmente entre formas de onda de alto nível e elementos de projeto, bem como automatizar a interação por meio de TCL ou Python.

- Acionamento complexo: defina acionadores de vários níveis com dependências baseadas em estado para reproduzir cenários de projeto complexos.

- Teste cruzado: capacidade de fazer um teste cruzado do resultado de depuração para RTL ou netlist para analisar e identificar a causa raiz dos bugs do projeto.

- Análise de forma de onda: exibe transições de sinal capturadas, anotando informações de acionamento com capacidade de rastrear até a fonte do projeto.

- Depuração de protocolo: análise específica do protocolo com cronogramas de transação para identificar gargalos e fazer testes cruzados de eventos de protocolo para RTL.

- Interface VIO: sinais de acionamento para teste e monitoramento interativos sem interromper ou reprogramar o projeto.

Turnos rápidos de depuração

Fluxos incrementais

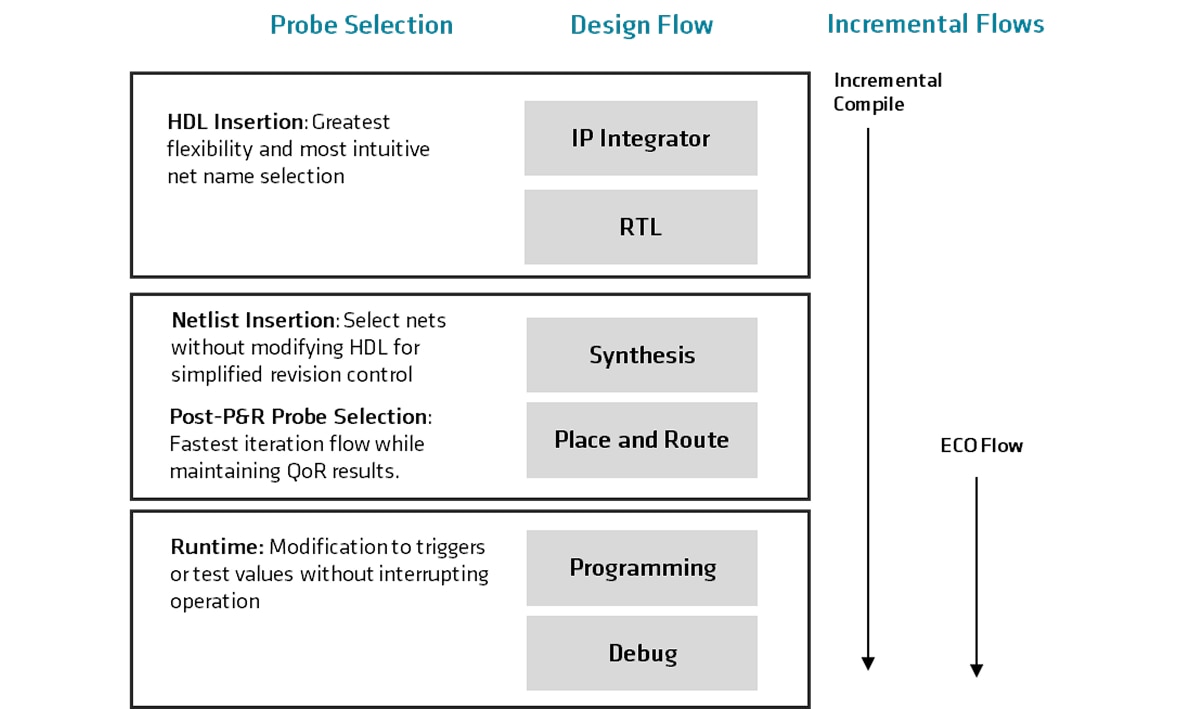

A modificação de acionamento, sondas e núcleos de depuração é inevitável à medida que os bugs são descobertos, tornando a iteração rápida essencial. O ChipScope aproveita vários tipos de fluxos de compilação incrementais para modificar apenas partes alteradas do projeto, evitando uma reconstrução completa durante os ciclos de depuração.

Vários fluxos incrementais estão disponíveis, dependendo do método de instrumentação de depuração:

- Compilação incremental: realiza síntese e P&R em partes alteradas do projeto

- Fluxo ECO: para seleção de sonda após o local e rota, é ideal para pequenas alterações e a maneira mais rápida de iterar com máxima preservação do projeto

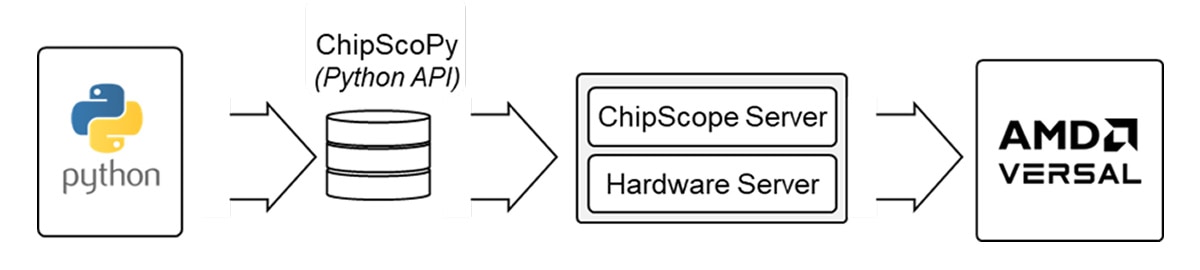

ChipScoPy: API Python para automação

Para dispositivos Versal, o ChipScoPy é uma interface Python simples para automatizar os recursos do ChipScope sem a necessidade do Vivado IDE, permitindo maior automação de depuração e controle para lógica programável e vários IPs rígidos.

As vantagens incluem:

- Fluxo flexível e personalizável pelo usuário que pode ser totalmente controlado por script

- Fluxo extensível que pode usar pacotes de terceiros e de código aberto, como o visualizador de gráficos

- Menor espaço de instalação, pois a instalação da ferramenta Vivado não é necessária