ChipScope 특징 및 기능

전체 통합 시스템이 실시간으로 실행될 때만 분명해지는 하드웨어 문제가 많습니다. Vivado ChipScope는 시스템 작동 중 설계 디버그용 프로그래밍 가능 로직에 대한 가시성을 극대화하여 포괄적인 흐름을 제공합니다.

설계 가시성

수백 개의 내부 노드로 확장하여 설계의 내부 작동을 명확하게 확인할 수 있습니다.

심층 해석

복잡한 트리거 조건을 구현하고 다양한 설계 관점을 해석합니다.

빠른 디버그 턴

빠른 반복에는 증분 컴파일 플로우를, 작업 자동화에는 Python™을 활용하세요.

Adam Taylor와 함께 살펴보는 하드웨어 디버그 단계

Adam Taylor가 작성한 AMD Versal™ 및 UltraScale+™ 디바이스 관련 두 가지 튜토리얼에서 Vivado ChipScope를 사용하여 실제 시스템에서 하드웨어를 디버깅하는 방법을 알아보세요. 각 튜토리얼은 디버그 방법론을 강조하고, 설계를 효과적으로 계측하는 방법을 보여 주며, 다운로드하여 실행 및 탐색할 수 있는 프로젝트를 포함합니다.

포괄적인 디버그 흐름

빠른 디버그 턴을 위해 디버그 IP 계측, 설계 분석, 런타임 구성, 증분 컴파일을 활용하는 유연한 방법론입니다.

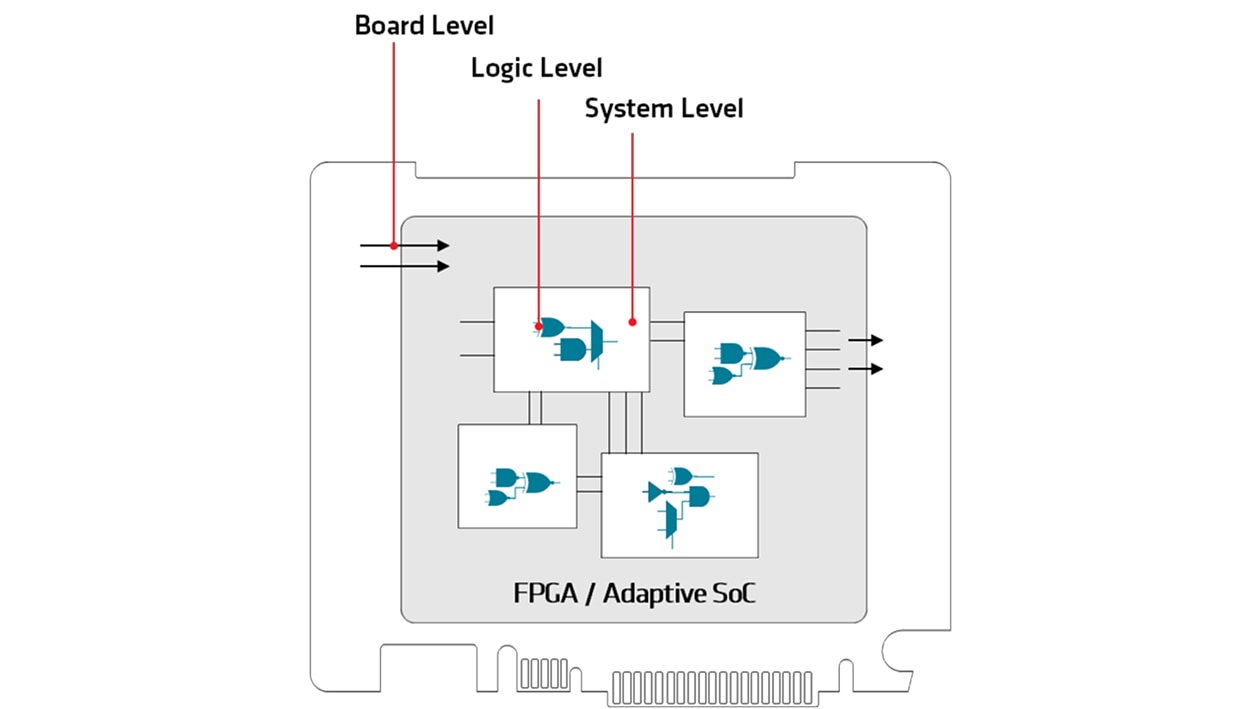

시스템 가시성

ChipScope는 시스템 분석을 위한 다양한 추상화 수준을 제공하며, 가시성을 극대화하기 위한 포괄적인 IP 세트를 갖추고 있습니다.

- 로직 수준 디버그: 통합 로직 분석기(ILA) 코어는 실시간으로 버그를 해결할 수 있도록 내부 신호의 고급 트리거와 캡처 기능을 제공합니다.

- 시스템 수준 디버그: 설계 블록 전반에서 트랜잭션 수준으로 검사를 수행할 수 있도록 AXI 인터페이스 및 I/O 프로토콜을 지원합니다.

- 보드 수준 디버그: 가상 I/O(VIO) 코어와의 보드 수준 상호 작용을 살펴보고 신호 모니터링과 테스트 값 주입을 통해 설계 동작을 검사합니다.

디버그 IP

패브릭 디버그 흐름의 핵심은 설계 기능을 방해하지 않으면서 설계 가시성을 확보할 수 있는 IP 코어 집합입니다. 모든 AMD 디버그 IP는 온라인뿐만 아니라 Vivado Design Suite 내의 IP 카탈로그를 통해 사용할 수 있습니다. Versal™ Adaptive SoC에 대한 프로그래밍 가능 로직 디버그는 철저하게 AXI 기반입니다.

FPGA 및 Zynq™ Adaptive SoC |

AMD Versal Adaptive SoC |

|

통합 로직 분석기(ILA) |

||

시스템 ILA |

||

가상 입/출력(VIO) |

||

BSCAN-JTAG 컨버터 |

- |

|

디버그 허브* |

시스템 디버그 버스(XSDB) – 빌트인 |

*디버그 허브는 JTAG를 통해 디버그 IP 코어와의 통신을 촉진합니다

데이터 케이블 모듈

AMD는 표준 JTAG 디버깅 및 이종 시스템의 고속 디버깅을 위한 다양한 데이터 케이블을 제공합니다. 데이터를 대용량으로 캡처하는 것, 장치 리소스 사용을 최소화하는 것, 또는 더 빠른 디버그 성능을 달성하는 것 중 어떤 것이 우선순위이든, 적절한 데이터 케이블을 선택하는 것은 워크플로의 효율성에 영향을 줄 수 있습니다.

데이터 케이블 모듈 외에도 대부분의 평가 키트는 빌트인 USB-JTAG 디버그 인터페이스를 제공하며, 일부 디바이스 제품군은 이더넷을 통한 디버그 또는 PCI-Express®를 제공합니다. 아래에서 데이터 케이블 모듈에 대해 자세히 알아보세요.

| 디바이스 지원 | 플랫폼 케이블 USB II | SmartLynq | SmartLynq+ |

|---|---|---|---|

| AMD FPGA | ✓ | ✓ | |

| Zynq Adaptive SoC | ✓ | ✓ | |

| Versal Adaptive SoC | ✓ | ✓ |

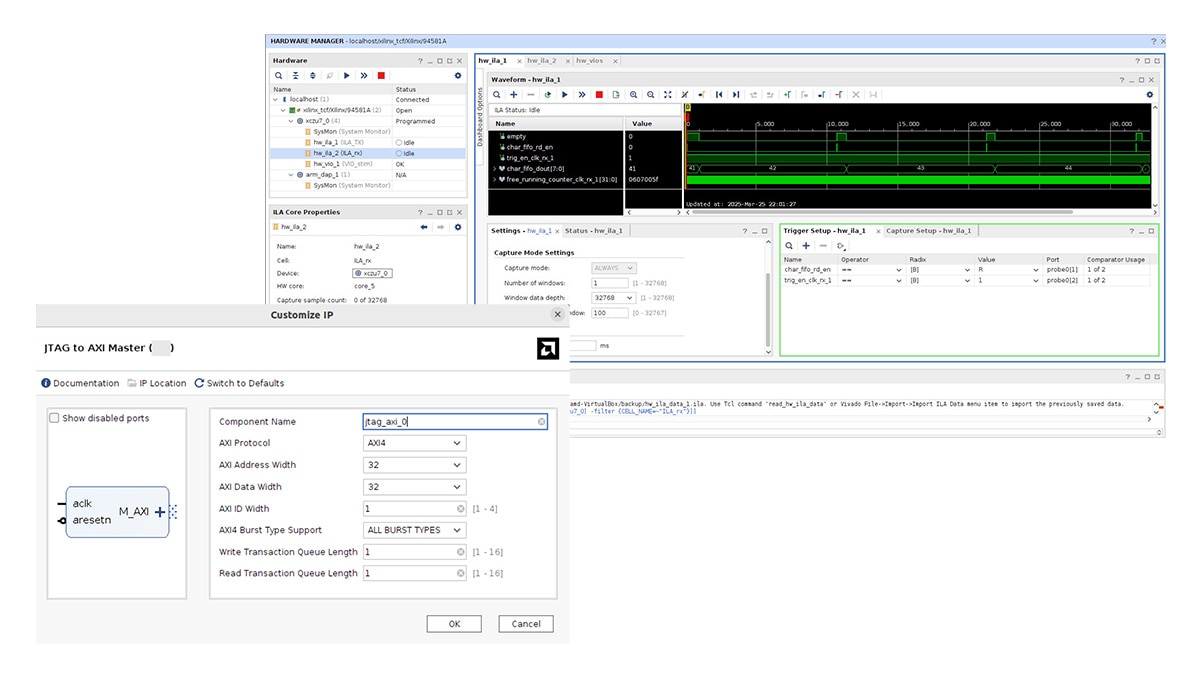

설계 분석

ChipScope는 시스템 내 디버그 및 추적을 위해 다양한 인터페이스와 자동화 방식을 제공합니다. Vivado IDE 내에서 설계자는 높은 수준의 파형과 설계 요소 사이를 원활하게 탐색할 수 있을 뿐만 아니라, TCL 또는 Python을 통한 상호 작용을 자동화할 수 있습니다.

- 복합 트리거링: 복잡한 설계 시나리오를 재현하기 위해 상태 기반 종속성으로 다단계 트리거를 설정합니다.

- 크로스 프로빙: 디버그 출력에서 RTL 또는 넷리스트로 크로스 프로빙하여 설계 버그의 근본 사례를 분석하고 식별할 수 있습니다.

- 파형 분석: 캡처된 신호 전환을 표시하며, 트리거 정보를 주석으로 표시하고 설계 소스까지 추적할 수 있는 기능을 제공합니다.

- 프로토콜 디버그: 트랜잭션 타임라인이 포함된 프로토콜별 분석을 통해 병목 현상을 식별하고 프로토콜 이벤트에서 RTL까지 크로스 프로빙을 수행합니다.

- VIO 인터페이스: 설계를 중지하거나 다시 프로그래밍하지 않고도 대화형 테스트 및 모니터링을 위한 신호를 구동합니다.

빠른 디버그 턴

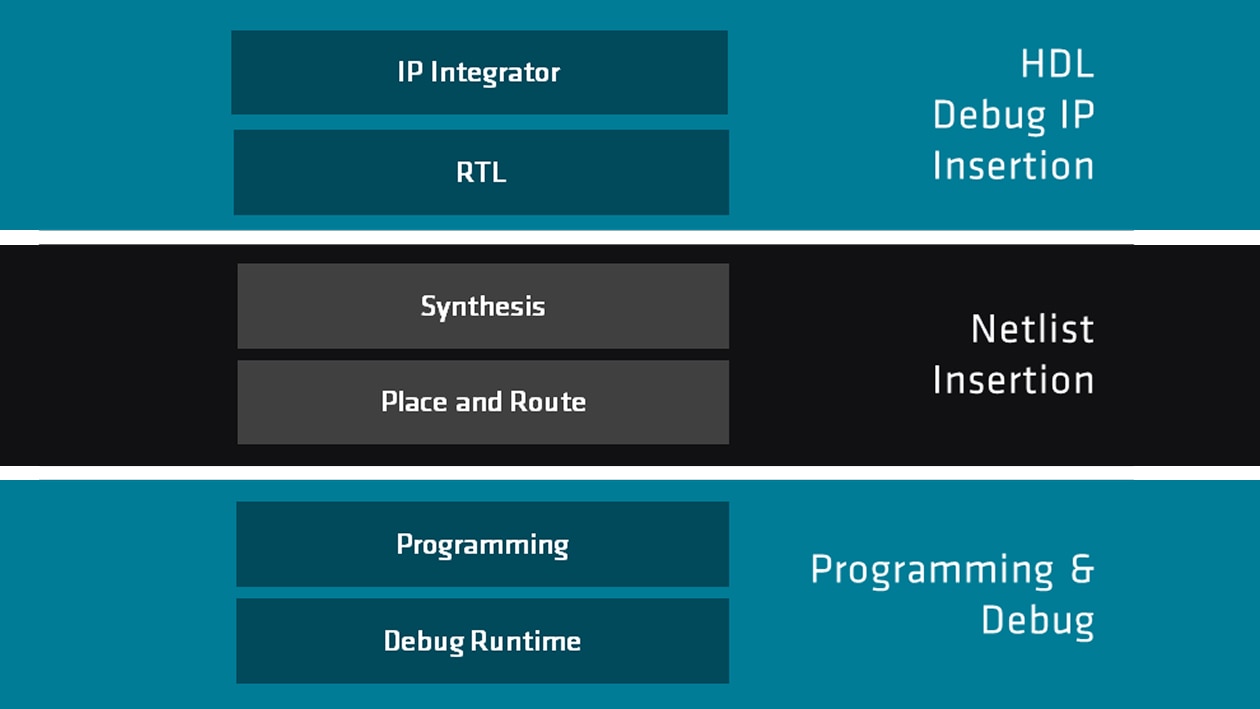

증분 흐름

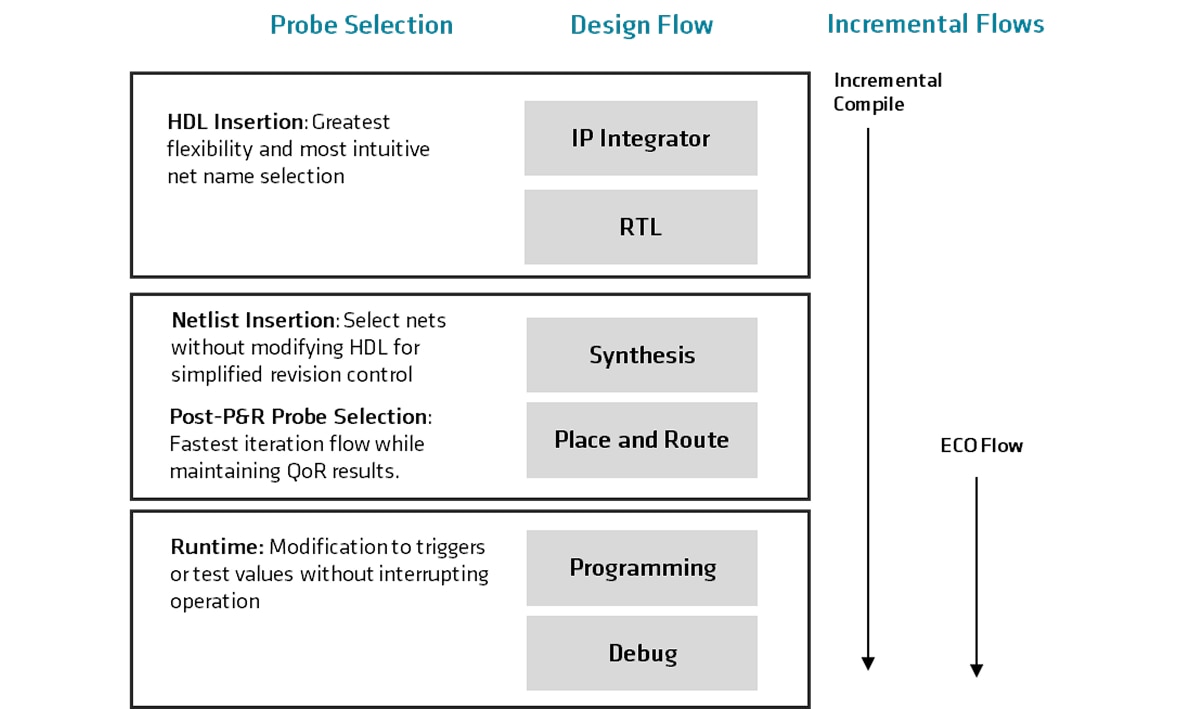

버그가 발견되면 트리거, 프로브, 디버그 코어의 수정이 불가피하며 빠른 반복이 중요해집니다. ChipScope는 여러 유형의 증분 컴파일 흐름을 활용하여 설계에서 변경된 부분만 수정하므로, 디버그 주기 동안 전체 재구축을 방지할 수 있습니다.

디버그 계측 방법에 따라 여러 증분 흐름을 사용할 수 있습니다.

- 증분 컴파일: 설계 변경 부분에 대한 합성 및 P&R을 수행합니다.

- ECO 흐름: 배치 및 배선 후 프로빙을 선택할 수 있으므로 사소한 변경에 적합하며, 설계를 최대한 보존하면서 반복 작업을 가장 빠르게 수행할 수 있는 방법입니다.

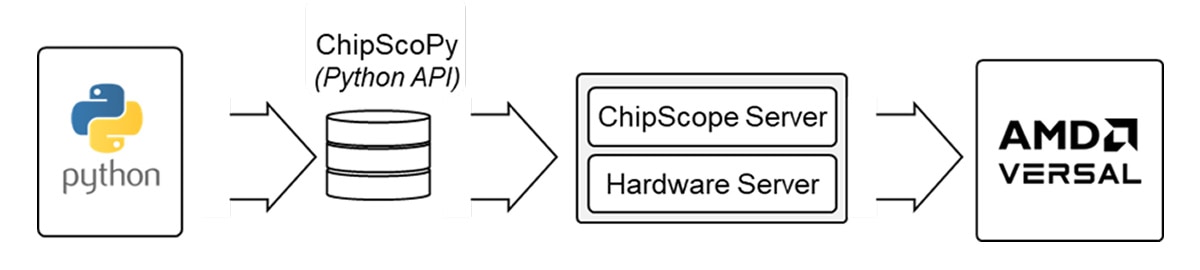

ChipScoPy: 자동화를 위한 Python API

Versal 디바이스의 경우 ChipScoPy는 Vivado IDE 없이 ChipScope 기능을 자동화할 수 있는 간단한 Python 인터페이스로, 프로그래밍 가능 로직 및 다양한 하드 IP에 대한 디버그 자동화 및 제어를 향상합니다.

장점은 다음과 같습니다.

- 완벽하게 스크립팅할 수 있는 유연하고 사용자 지정 가능한 흐름

- 플롯 뷰어와 같은 타사 및 오픈 소스 패키지를 사용할 수 있는 확장 가능한 흐름

- Vivado 툴 설치가 필요하지 않으므로 더 작은 설치 공간 필요