ChipScope の機能と性能

多くの場合、ハードウェアの問題が顕在化するのは、完全に統合されたシステムをリアルタイムで稼働させたときです。Vivado ChipScope は、システム動作中のデザイン デバッグにおいて、プログラマブル ロジックの可視性を最大化する包括的なフローを提供します。

デザインの可視性

内部ノードを数百に拡張して、デザインの内部構造を明確に可視化

詳細な解析

複雑なトリガー条件を実装し、複数のデザイン ビューで解析

高速デバッグ サイクル

インクリメンタル コンパイル フローを活用して反復を高速化し、Python™ でタスクを自動化

Adam Taylor 氏による、ステップバイステップのハードウェア デバッグ説明

Adam Taylor 氏が Vivado ChipScope を使用した実際のハードウェアのデバッグ方法を伝授します。AMD Versal™ と UltraScale+™ デバイス向けに別々のチュートリアルをご用意しました。各チュートリアルでは、デバッグ手法を重点的に説明し、デザインを効果的にインストルメント化する方法を示しています。また、ダウンロード可能なプロジェクトも含まれており、実行して検証できます。

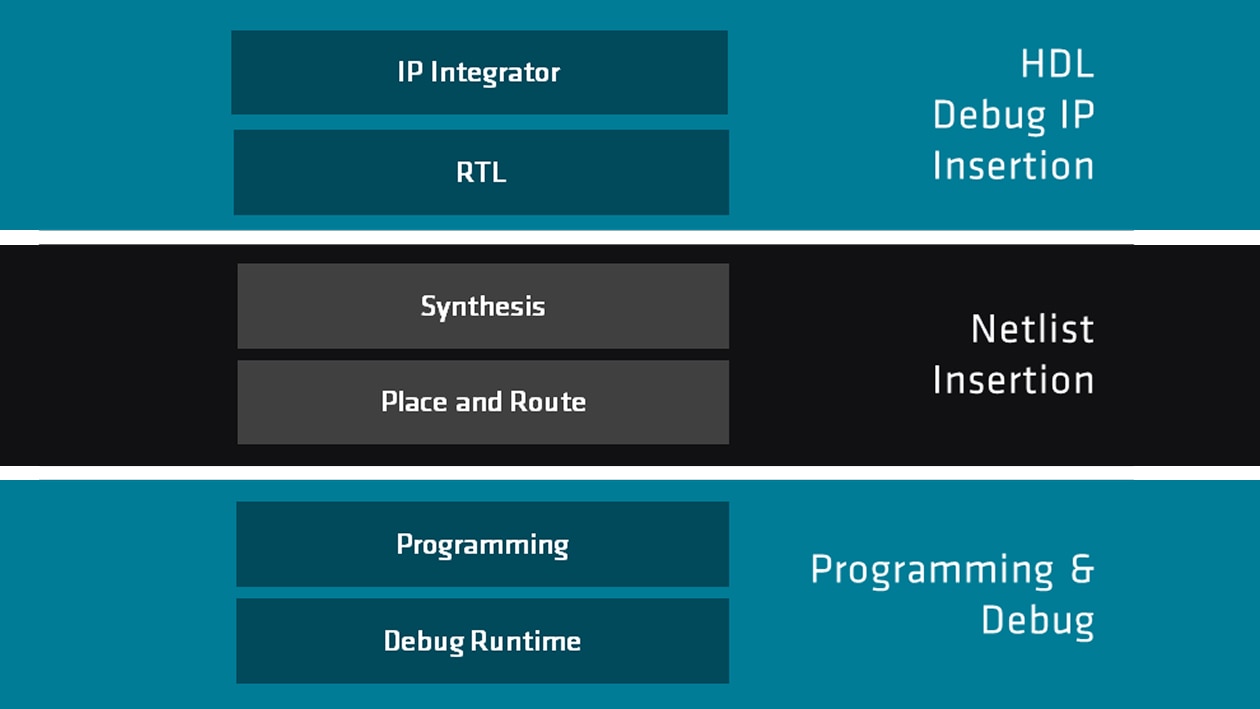

包括的なデバッグ フロー

デバッグ用 IP のインストルメンテーション、デザイン解析、ランタイム構成、インクリメンタル コンパイルなど、柔軟なデバッグ手法により、高速なデバッグを実現します。

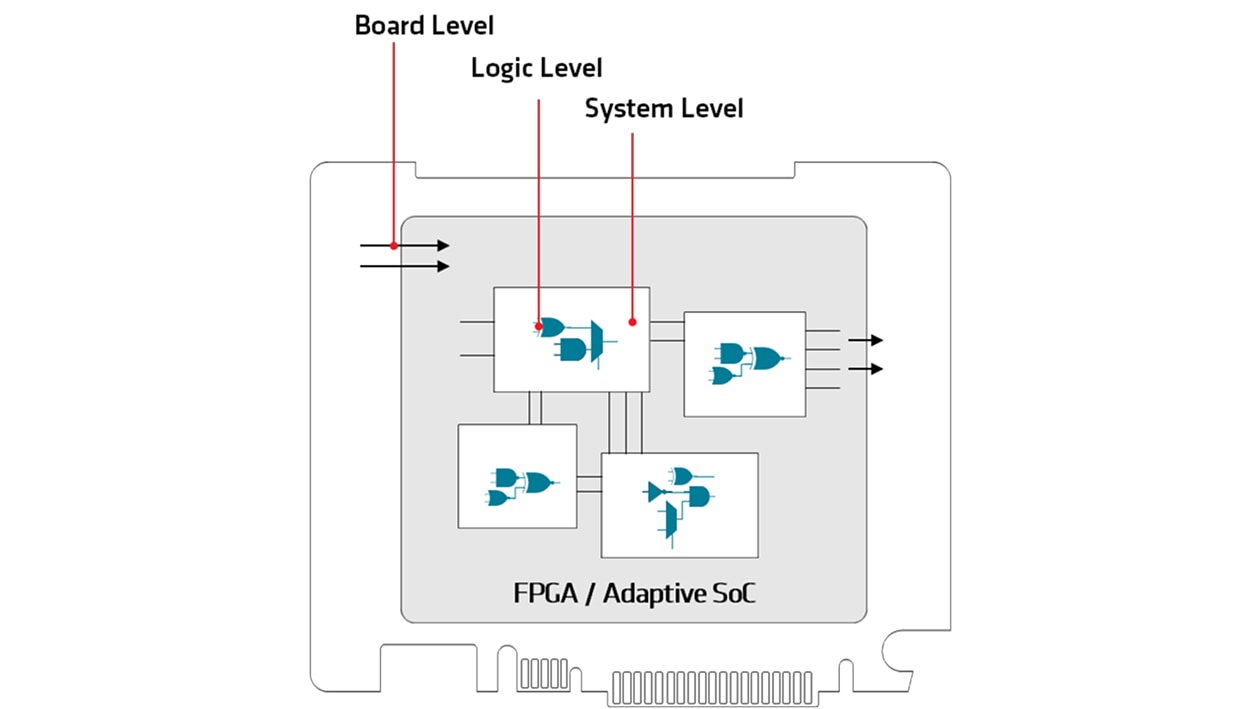

システムの可視性

ChipScope は、可視性を最大限に高める包括的な IP セットを使用してシステムを解析するための、複数の抽象化レベルを提供します。

- ロジック レベルのデバッグ: Integrated Logic Analyzer (ILA) コアは、内部信号の高度なトリガーとキャプチャ機能を持っており、バグをリアルタイムでトラブルシューティングします。

- システム レベルのデバッグ: AXI インターフェイスと I/O プロトコルをサポートし、デザイン ブロック全体でトランザクション レベルの検査を可能にします。

- ボードレベルのデバッグ: 仮想 I/O (VIO) コアを使用してボードレベルの相互作用を調査し、信号のモニタリングやテスト値の注入によりデザインの動作を検証します。

デバッグ IP

ファブリックのデバッグ フローに不可欠な IP コアのセットです。デザイン機能を妨げることなく設計を可視化します。AMD のデバッグ IP はすべて、Vivado Design Suite の IP カタログからオンラインで利用できます。Versal™ アダプティブ SoC のプログラマブル ロジックのデバッグは、厳密に AXI ベースであることに注意してください。

FPGA と Zynq™ アダプティブ SoC |

AMD Versal アダプティブ SoC |

|

Integrated Logic Analyzer (ILA) |

||

System ILA |

||

仮想入出力 VIO |

||

BSCAN-JTAG 間コンバーター |

- |

|

デバッグ ハブ* |

システム デバッグ バス (XSDB) - ビルトイン |

*デバッグ ハブは、JTAG を介したデバッグ IP コアとの通信を容易にします。

データ ケーブル モジュール

AMD は、標準 JTAG デバッグおよび異種システムの高速デバッグ用の各種データ ケーブルを提供しています。大量のデータのキャプチャ、デバイス リソースの使用率の最小化、またはデバッグ パフォーマンスの高速化など、優先事項がどのようなものであっても、適切なデータ ケーブルを選択することで、ワークフローの効率が向上します。

データ ケーブル モジュールに加えて、ほとんどの評価キットにはビルトイン USB-to-JTAG デバッグ インターフェイスが搭載されており、一部のデバイス ファミリでは、イーサネットまたは PCI-Express® を介したデバッグが可能です。データ ケーブル モジュールの詳細については、次をご覧ください。

| デバイス サポート | プラットフォーム ケーブル USB II | SmartLynq | SmartLynq+ |

|---|---|---|---|

| AMD FPGA | ✓ | ✓ | |

| Zynq アダプティブ SoC | ✓ | ✓ | |

| Versal アダプティブ SoC | ✓ | ✓ |

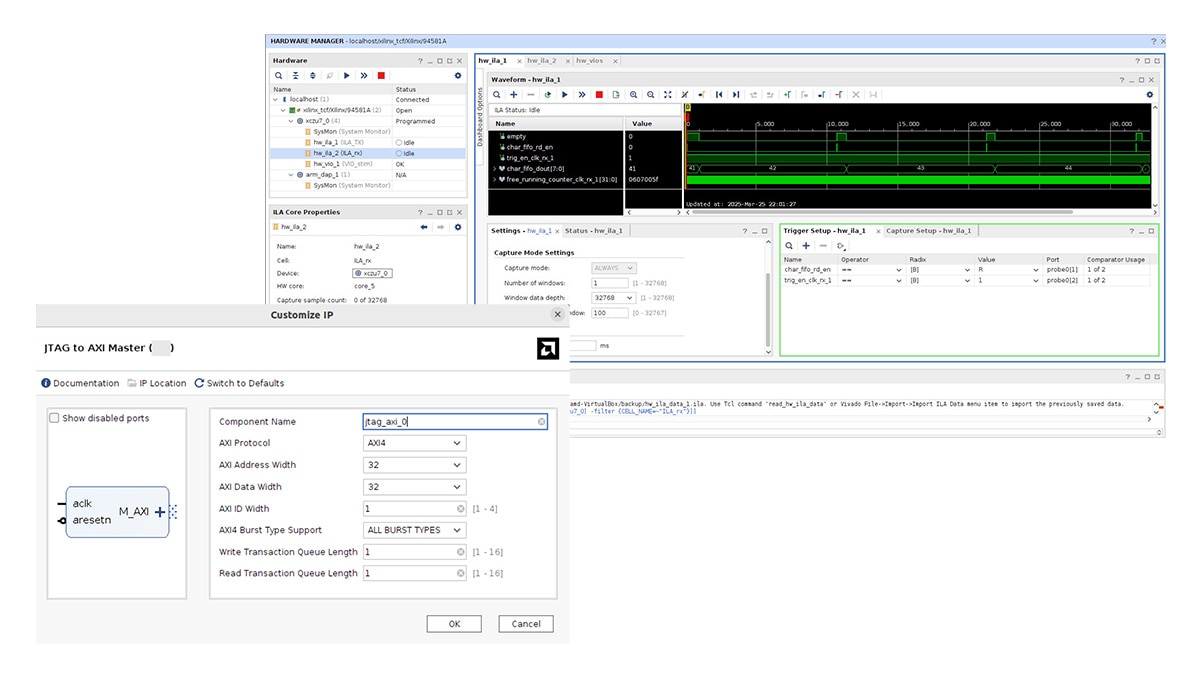

デザイン解析

ChipScope は、システム内デバッグおよびトレース用にさまざまなインターフェイスと自動化手法を提供します。Vivado IDE 内では、設計者は高レベルの波形とデザイン エレメント間をシームレスに移動でき、また、TCL または Python による自動化も可能です。

- 複雑なトリガー: 複雑なデザイン シナリオを再現するために、状態ベースの依存関係を持つマルチ レベルのトリガーを設定します。

- クロスプローブ: デバッグ出力から RTL またはネットリストにクロスプローブし、デザイン バグの根本原因を解析して特定します。

- 波形解析: キャプチャした信号遷移を表示し、デザイン ソースに遡ってトレースする機能により、トリガー情報のアノテーションを追加します。

- プロトコルのデバッグ: トランザクション タイムラインを使用して、ボトルネックを特定し、プロトコル イベントから RTL へのクロスプローブを実行します。

- VIO インターフェイス: デザインを停止または再プログラムすることなく、インタラクティブなテストとモニタリング用の信号を駆動します。

高速デバッグ サイクル

インクリメンタル フロー

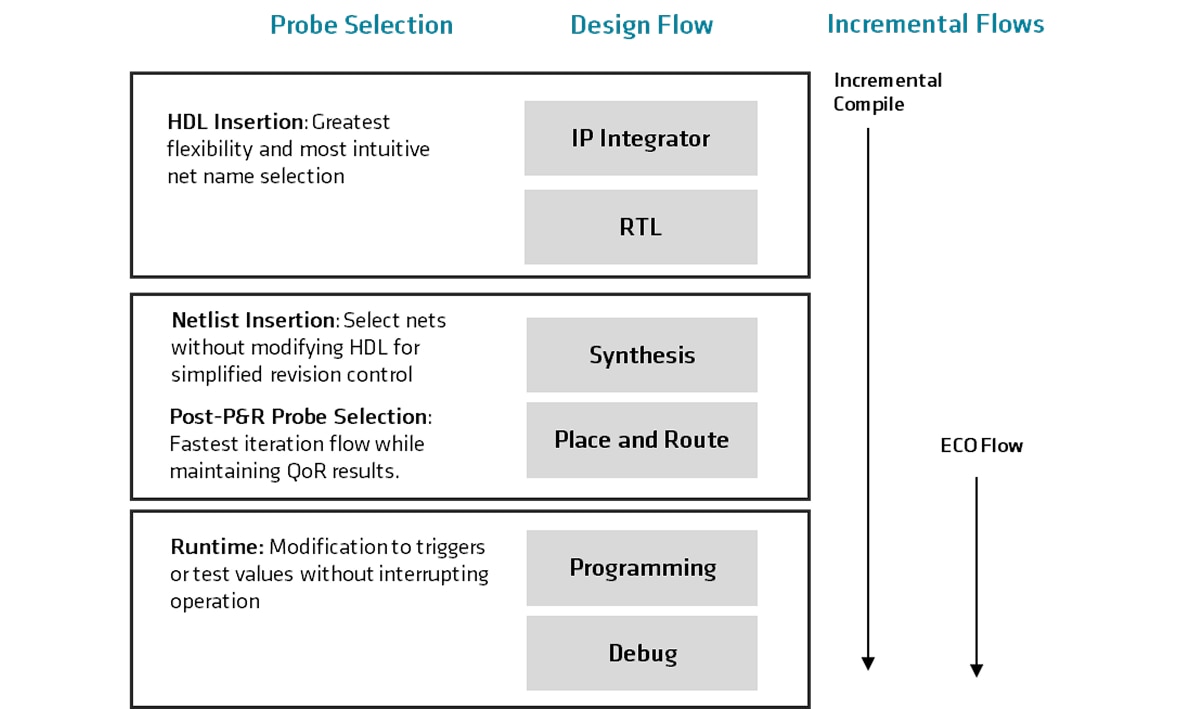

バグが発見された場合、トリガー、プローブ、デバッグ コアの修正は不可避であり、迅速な反復が重要となります。ChipScope は、複数の種類のインクリメンタル コンパイル フローを活用し、デザインの変更された部分のみを修正することで、デバッグ サイクル中のフル リビルドを回避します。

デバッグのインストルメンテーション方法に応じて、複数のインクリメンタル フローが利用可能です。

- インクリメンタル コンパイル: デザインの変更部分について合成と P&R を実施

- ECO フロー: 配置配線後のプローブ選択に最適 – 軽微な変更に最適で、デザインを最大限に保持しながら反復する最速の方法

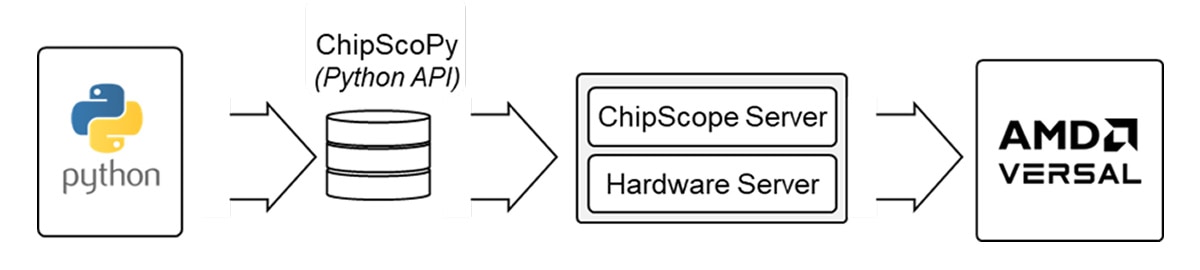

ChipScoPy: 自動化用 Python API

Versal デバイスでは、ChipScoPy は Vivado IDE を必要とせずに ChipScope の機能を自動化するシンプルな Python インターフェイスです。これにより、プログラマブル ロジックやさまざまなハード IP のデバッグの自動化と制御が向上します。

次のような利点があります。

- 柔軟でユーザーがカスタマイズ可能なフローで、完全にスクリプト化が可能

- 拡張可能なフローで、プロット ビューアーなどのサードパーティ製およびオープンソース パッケージを使用可能

- Vivado ツールのインストールが不要なため、インストールに必要な容量が少ない