Fonctionnalités et capacités de ChipScope

De nombreux problèmes hardwares ne deviennent apparents que lorsque le système complet et intégré fonctionne en temps réel. Vivado ChipScope fournit un flux complet afin de maximiser la visibilité de la logique programmable pour le débogage de conception pendant le fonctionnement du système.

Visibilité de la conception

Passez à des centaines de nœuds internes pour obtenir une vue claire du fonctionnement interne de votre conception.

Analyse approfondie

Mettez en œuvre des conditions de déclenchement complexes et faites des analyses sur plusieurs vues d'une conception.

Tours de débogage rapides

Exploitez les flux de compilation incrémentielle pour bénéficier d'une itération rapide et utilisez Python™ pour automatiser les tâches.

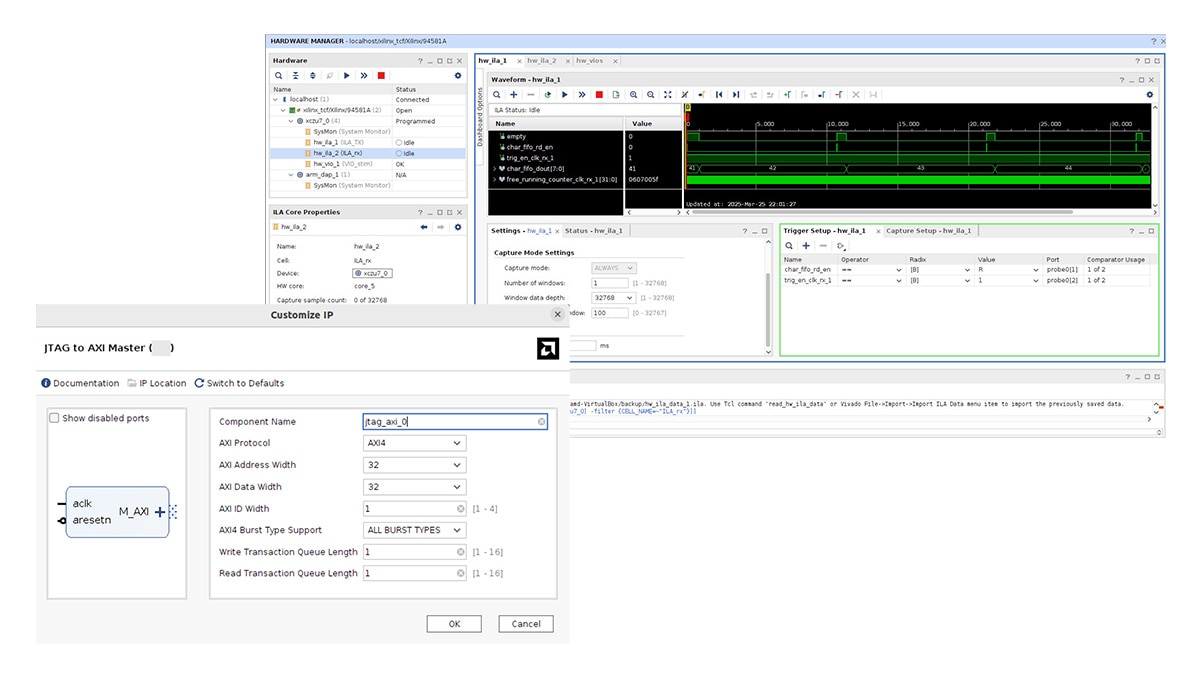

Analyseur ChipScope AMD Vivado™

Cette vidéo fournit une présentation pratique de la mise en œuvre et de l'utilisation de ChipScope pour le débogage hardware. Elle couvre le processus d'intégration de l'analyseur logique interne et des noyaux de débogage dans la logique programmable, la configuration des déclencheurs et l'analyse des données capturées pour l'identification et la résolution rapide des problèmes.

Débogage hardware étape par étape avec Adam Taylor

Découvrez comment déboguer du hardware dans des systèmes réels à l'aide de Vivado ChipScope, grâce à deux didacticiels distincts pour les périphériques AMD Versal™ et UltraScale+™, créés par Adam Taylor. Chaque étape guidée met l'accent sur la méthodologie de débogage, illustre comment utiliser efficacement les conceptions et inclut des projets téléchargeables que vous pouvez exécuter et explorer.

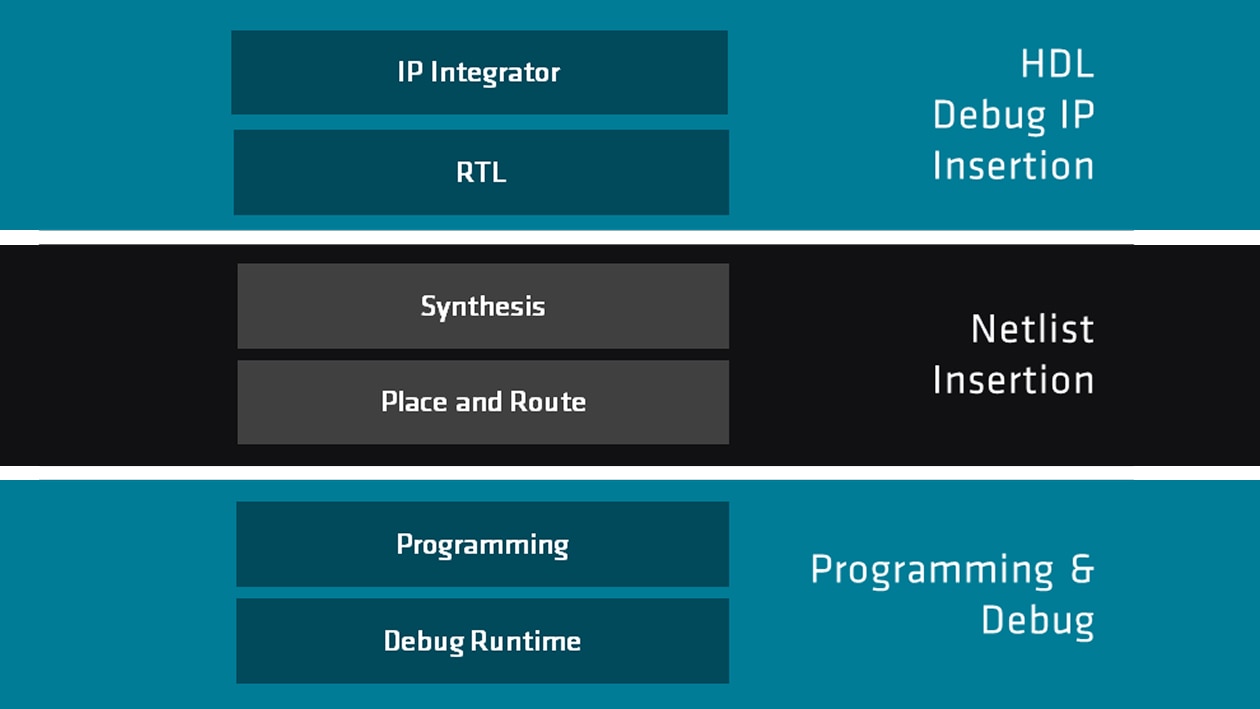

Flux de débogage complet

Méthodologies flexibles pour le débogage de l'instrumentation IP, l'analyse de conception, la configuration d'exécution et la compilation incrémentielle afin d'obtenir des tours de débogage rapides.

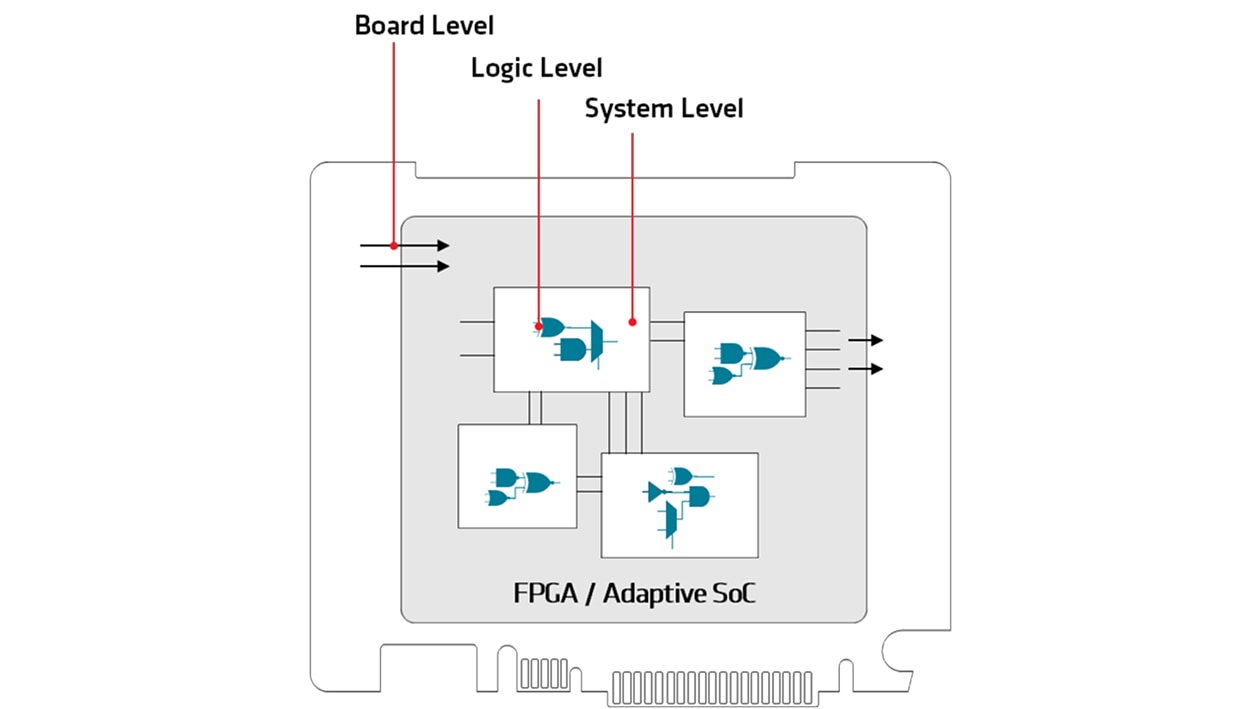

Visibilité du système

ChipScope fournit plusieurs niveaux d'abstraction pour l'analyse de votre système avec un ensemble complet d'IP pour optimiser la visibilité.

- Débogage au niveau de la logique : Les noyaux de l'analyseur logique intégré (Integrated Logic Analyzer - ILA)) permettent le déclenchement avancé des signaux internes et des fonctions de capture pour résoudre les bogues en temps réel.

- Débogage au niveau du système : Prise en charge des interfaces AXI et des protocoles d'E/S, permettant une inspection au niveau de la transaction sur l'ensemble des blocs de conception.

- Débogage au niveau de la carte : Explorez l'interaction au niveau de la carte avec les cœurs d'E/S virtuels, permettant de surveiller les signaux et d'injecter des valeurs de test pour examiner le comportement de la conception.

IP de débogage

Un ensemble de cœurs IP est essentiel au flux de débogage de la structure pour permettre la visibilité de la conception sans entraver les fonctionnalités de conception. Toutes les adresses IP de débogage AMD sont disponibles en ligne et via le catalogue IP de Vivado Design Suite. Notez que le débogage de la logique programmable pour les SoC adaptatifs Versal™ est strictement basé sur les interfaces AXI.

FPGA et SoC adaptatifs Zynq™ |

SoC adaptatifs AMD Versal |

|

Integrated Logic Analyzer (ILA) |

||

ILA du système |

||

Entrée/sortie virtuelle |

||

Convertisseur BSCAN vers JTAG |

- |

|

Debug Hub* |

Bus de débogage système (XSDB) – Intégré |

Debug Hub facilite la communication avec les cœurs IP de débogage sur JTAG

Modules de câble de données

AMD propose une gamme de câbles de données pour le débogage JTAG standard et le débogage haute vitesse de systèmes hétérogènes. Que votre priorité soit la capture de grands volumes de données, la réduction de l'utilisation de ressources des appareils ou l'obtention de performances de débogage plus rapides, le choix d'un câble de données adapté peut avoir un impact sur l'efficacité de votre flux de travail.

En plus des modules de câble de données, la plupart des kits d'évaluation offrent des interfaces de débogage USB vers JTAG intégrées et certaines familles d'appareils offrent un débogage sur Ethernet ou PCI-Express®. En savoir plus sur les modules de câble de données ci-dessous.

| Prise en charge des appareils | Câble de plateforme USB II | SmartLynq | SmartLynq+ |

|---|---|---|---|

| FPGA d'AMD | ✓ | ✓ | |

| SoC adaptatifs Zynq | ✓ | ✓ | |

| SOC adaptatifs Versal | ✓ | ✓ |

Analyse de conception

ChipScope fournit diverses interfaces et méthodes d'automatisation pour le débogage et le traçage dans le système. Dans l'IDE Vivado, les concepteurs peuvent naviguer en toute transparence entre les formes d'onde de haut niveau et les éléments de conception, et automatiser l'interaction via TCL ou Python.

- Déclenchement complexe : définissez des déclencheurs à plusieurs niveaux avec des dépendances basées sur l'état pour reproduire des scénarios de conception complexes.

- Cross-probing : effectuez des cross probe de la sortie de débogage vers RTL ou une liste réseau pour analyser et identifier les causes premières des bogues de conception.

- Analyse de forme d'onde : affiche les transitions de signaux de capture, annote les informations de déclenchement et permet de remonter à la source de la conception.

- Débogage de protocole : analyse spécifique au protocole avec délais de transaction pour identifier les goulots d'étranglement et effectuer des analyses croisées entre les événements du protocole et le RTL.

- Interface d'E/S virtuelle : contrôlez des signaux pour effectuer des tests et une surveillance interactifs sans arrêter ou reprogrammer la conception.

Tours de débogage rapides

Flux incrémentiels

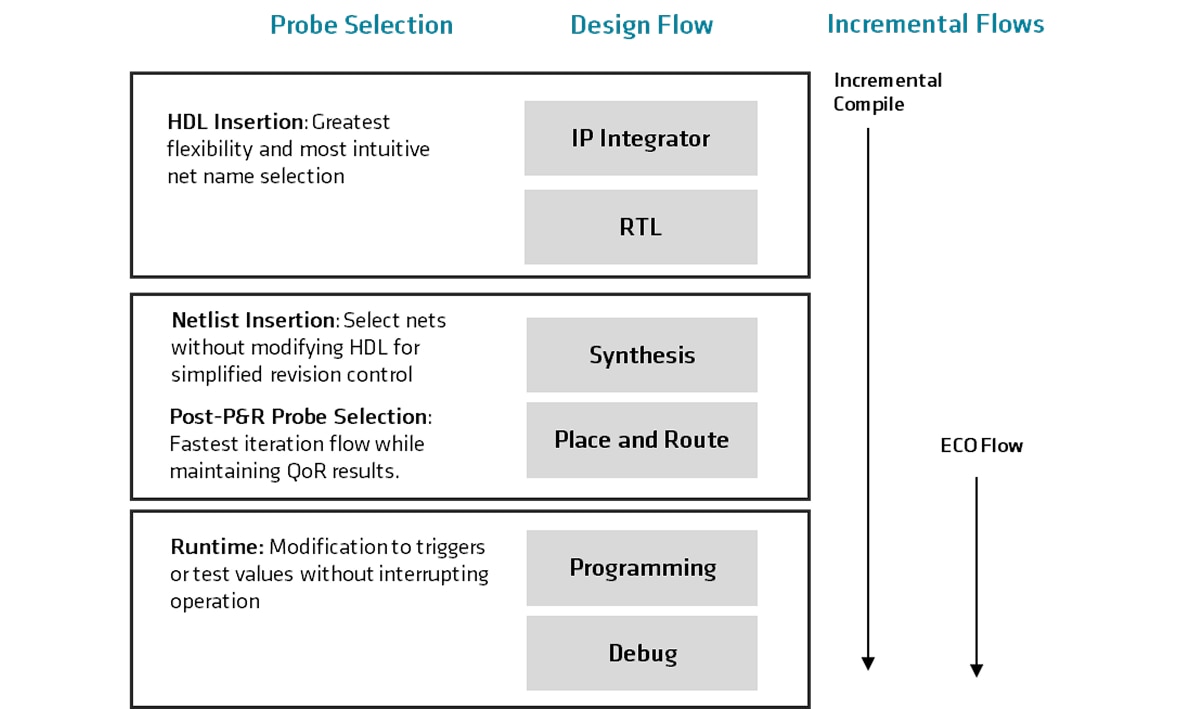

La modification des déclenchements, des sondes et des noyaux de débogage est inévitable lors de la détection des bogues, ce qui rend l'itération rapide critique. ChipScope utilise plusieurs types de flux de compilation incrémentielle pour modifier uniquement les parties changées de la conception, évitant ainsi une reconstruction complète pendant les cycles de débogage.

Plusieurs flux incrémentiels sont disponibles en fonction de la méthode d'instrumentation de débogage :

- Compilation incrémentielle : effectue la synthèse, le placement et le routage sur les parties modifiées de la conception

- Flux ECO : lors de la sélection des sondes après le placement et le routage : idéal pour les changements mineurs et moyen le plus rapide d'itérer en conservant la conception le plus possible

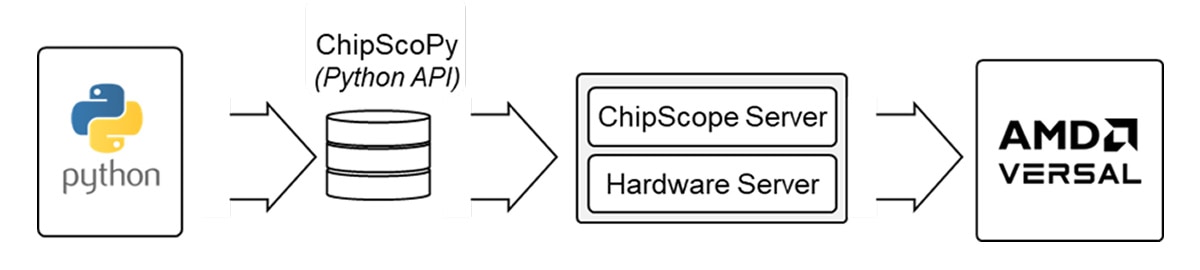

ChipScoPy : API Python pour l'automatisation

Pour les appareils Versal, ChipScoPy est une interface Python simple pour l'automatisation des capacités ChipScope sans avoir besoin de l'IDE Vivado, permettant une automatisation et un contrôle de débogage plus importants pour la logique programmable et diverses IP hardwares.

Les avantages sont les suivants :

- Flux flexible et personnalisable qui peut être entièrement scripté

- Flux extensible pouvant utiliser des packages tiers et open source tels que Plot Viewer

- Encombrement d'installation réduit car l'installation de l'outil Vivado n'est pas nécessaire