ChipScope 的特點與功能

許多硬體問題都只會在完全整合系統即時執行的當下才會顯現。Vivado ChipScope 提供全方位流程,可充分發揮可程式化邏輯的可見度,助您在系統執行期間進行設計除錯。

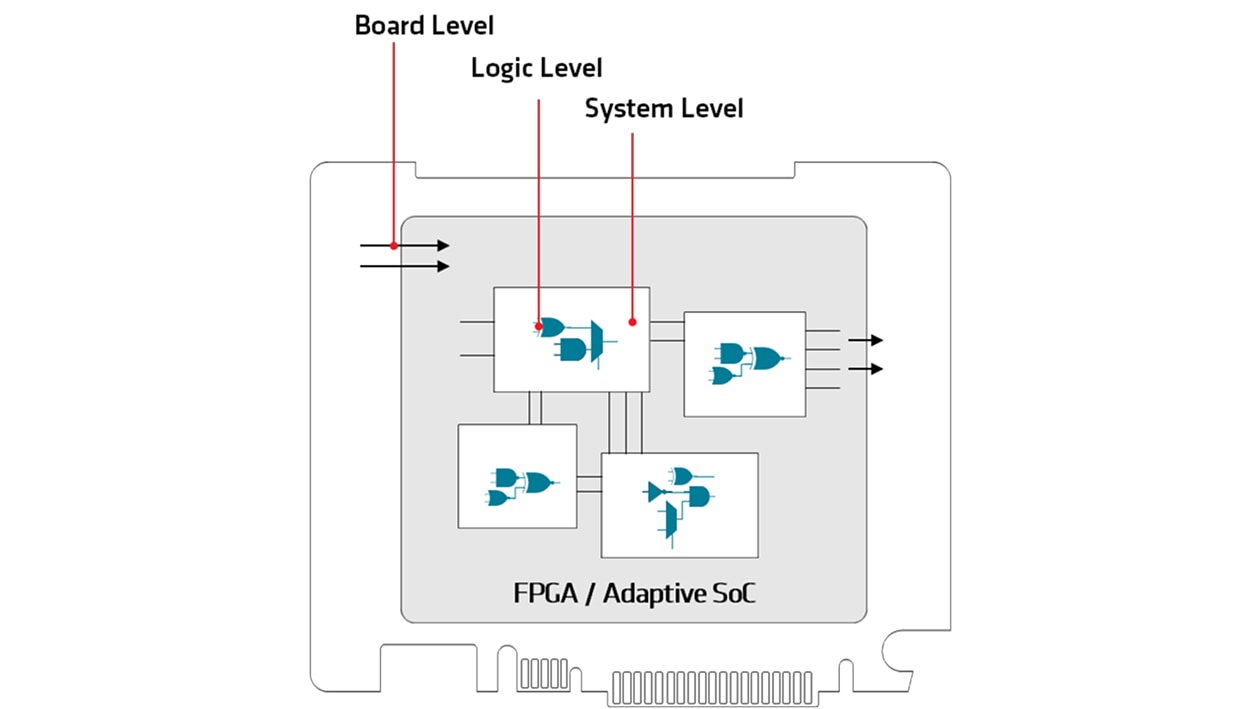

設計可見度

放大到數百個內部節點,清楚呈現設計的內部作業情況。

深入分析

導入複雜的觸發條件並分析多個設計視圖。

快速反覆除錯

運用漸進式編譯流程加快迭代速度,並以 Python™ 將任務自動化。

與 Adam Taylor 一起逐步進行硬體除錯

查看 Adam Taylor 編寫的 AMD Versal™ 和 UltraScale+™ 裝置專屬教學課程,瞭解如何使用 Vivado ChipScope,分別在這兩個實際系統中執行硬體除錯。這兩個課程重點為除錯方法,將逐步說明如何有效設計儀器,且包含可下載的專案供您執行及探索。

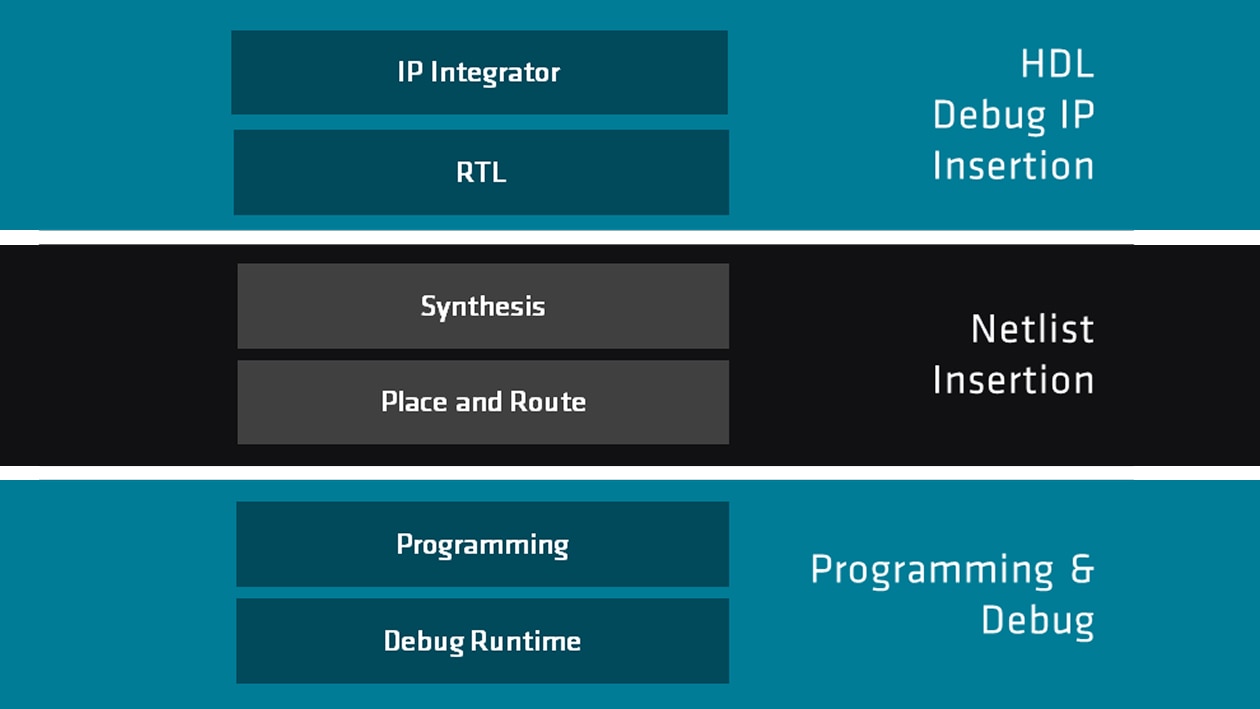

全方位除錯流程

提供除錯 IP 工具使用、設計分析、執行時間設定和漸進式編譯的彈性方法,實現快速反覆除錯。

除錯 IP

網狀架構除錯流程的基本要素為 IP 核心集,可實現設計可見度又不會妨礙設計功能。所有 AMD 除錯 IP 均可在線上取得,也可透過 Vivado Design Suite 中的 IP 目錄取得。請注意,Versal™ 自適應晶片上系統 (System-on-Chip, SoC) 的可程式化邏輯除錯僅限以 AXI 為基礎。

FPGAs 與 Zynq™ 自適應 SoC |

AMD Versal 自適應 SoC |

|

Integrated Logic Analyzer (ILA) |

||

系統 ILA |

||

虛擬輸入/輸出 VIO |

||

BSCAN-to-JTAG 轉換器 |

- |

|

Debug Hub* |

系統除錯匯流排 (XSDB) – 內建 |

*Debug Hub 有助於透過聯合測試工作群組 (Joint Test Action Group, JTAG) 與除錯 IP 核心進行通訊

資料纜線模組

AMD 提供一系列資料纜線,可用於異構系統的標準 JTAG 除錯和高速除錯。無論您的優先要務是擷取大量資料、將裝置資源使用率降至最低,或加快除錯效能,選擇合適的資料纜線都會影響工作流程的效率。

除了資料纜線模組外,大多數評估套件還提供內建 USB 至 JTAG 除錯介面,特定系列裝置甚至可透過乙太網路或 PCI Express® 進行除錯。請在下方深入瞭解資料纜線模組。

| 器件支援 | 平台線 USB II | SmartLynq | SmartLynq+ |

|---|---|---|---|

| AMD FPGA | ✓ | ✓ | |

| Zynq 自適應 SoC | ✓ | ✓ | |

| Versal 自適應 SoC | ✓ | ✓ |

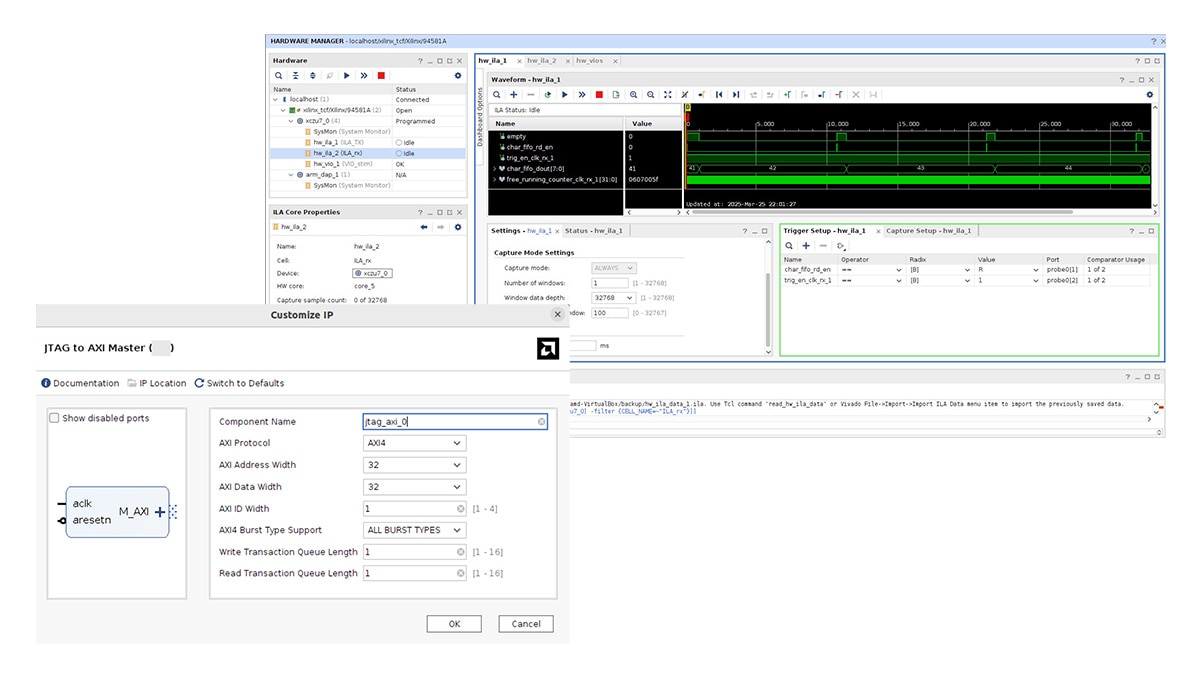

設計分析

ChipScope 提供多種用於系統內除錯及追蹤的介面和自動化方法。在 Vivado IDE 中,設計人員可在高級波形和設計元素之間流暢瀏覽,並透過工具命令語言 (Tool Command Language, TCL) 或 Python 自動化互動。

- 複雜觸發:以狀態式相依性設定多層觸發器,來重現複雜的設計情境。

- 交叉探查:能在除錯輸出至 RTL 或網路連線表的範圍內進行交叉探查,以分析及找出設計錯誤的根本原因。

- 波形分析:顯示擷取的訊號轉換情況,為觸發器資訊加註釋,並能回溯至設計來源。

- 通訊協定除錯:執行通訊協定特定分析並顯示交易時間軸,以找出瓶頸,並在通訊協定事件至 RTL 的範圍內進行交叉探查。

- VIO 介面:驅動交互測試和監測訊號,無須停止或重新編寫設計程式。

快速反覆除錯

漸進式流程

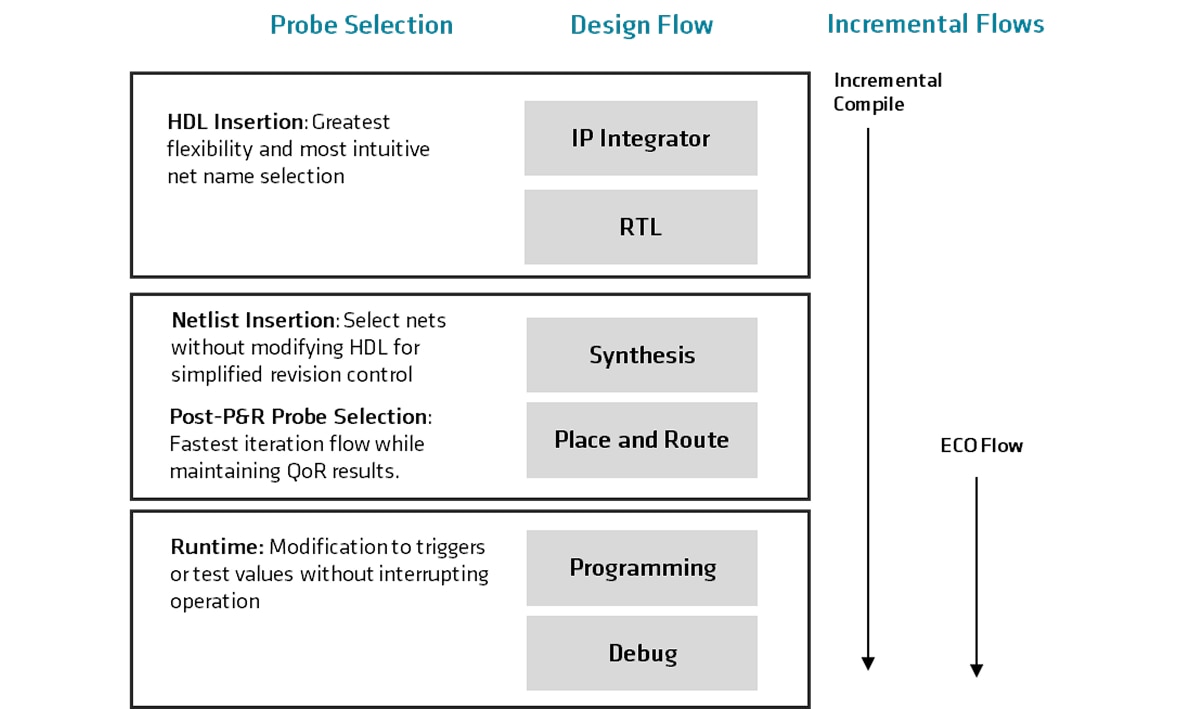

由於發掘錯誤時就必須修改觸發器、探查和除錯核心,因此加快迭代速度極其重要。ChipScope 採用多種漸進式編譯流程,因此在除錯週期內只需修改設計中待變更的部分,不必完全重新建置。

您可以根據除錯工具使用方法,採用多種漸進式流程:

- 漸進式編譯:對設計的已變更部分執行合成和 P&R

- ECO 流程:用於佈局與繞線後的探查選擇,適用於微幅變更,是最快迭代方式,並可盡可能保留設計

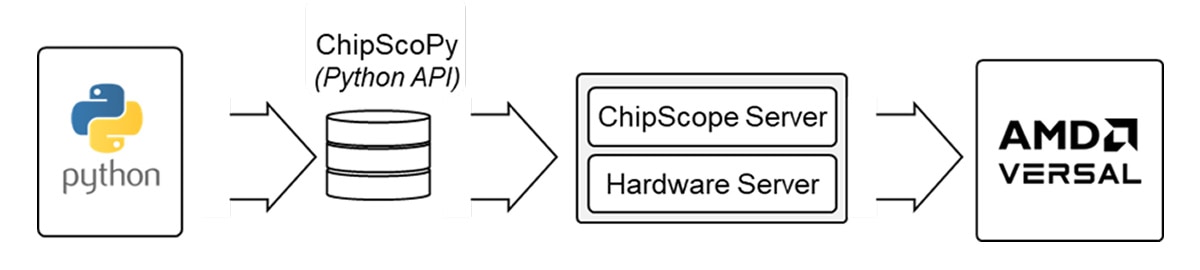

Chipscopy: 適用於自動化的 Python API

Chipscopy 是適用於 Versal 裝置的簡易 Python 介面,無需 Vivado IDE 即可自動執行 ChipScope 功能,能針對可程式化邏輯和多種硬式 IP,提升除錯自動化程度及強化控制。

優點包括:

- 可供使用者自訂的彈性流程,並可進行完整指令碼編寫

- 流程可擴充,並可使用第三方和開放原始碼套件 ,如繪圖檢視器

- 不需安裝 Vivado 工具,因此安裝佔用空間更小