ChipScope – Funktionen und Fähigkeiten

Viele Hardwareprobleme treten erst zutage, wenn das vollständige, integrierte System in Echtzeit ausgeführt wird. Vivado ChipScope bietet einen umfassenden Workflow, um maximale Transparenz der programmierbaren Logik für das Design-Debugging während des Systembetriebs zu erzielen.

Transparenz beim Design

Skalieren Sie auf Hunderte von internen Knoten, um einen klaren Überblick über die Arbeitsabläufe im Inneren Ihres Designs zu erhalten.

Detailanalyse

Implementieren Sie komplexe Triggerbedingungen und analysieren Sie mehrere Ansichten des Designs.

Schnelle Debugging-Läufe

Nutzen Sie inkrementelle Kompilier-Flows für eine schnelle Iteration und Python™ für die Automatisierung von Aufgaben.

AMD Vivado™ ChipScope Analyzer

Dieses Video bietet einen praktischen Überblick über die Implementierung und Verwendung von ChipScope für Hardware-Debugging. Es beschreibt, wie der interne Logic Analyzer und Debugging-Kerne in die programmierbare Logik integriert, Trigger eingerichtet und erfasste Daten analysiert werden, damit Sie Probleme schnell erkennen und beheben.

Hardware-Debugging Schritt für Schritt erklärt mit Adam Taylor

Erfahren Sie in zwei verschiedenen Tutorials für AMD Versal™ und UltraScale+™ Chips, wie Sie Hardware in realen Systemen mit Vivado ChipScope debuggen können. Jeder der Walkthroughs geht insbesondere auf die Debugging-Methoden ein, zeigt, wie Designs effektiv instrumentiert werden, und enthält herunterladbare Projekte, die Sie ausführen und erkunden können.

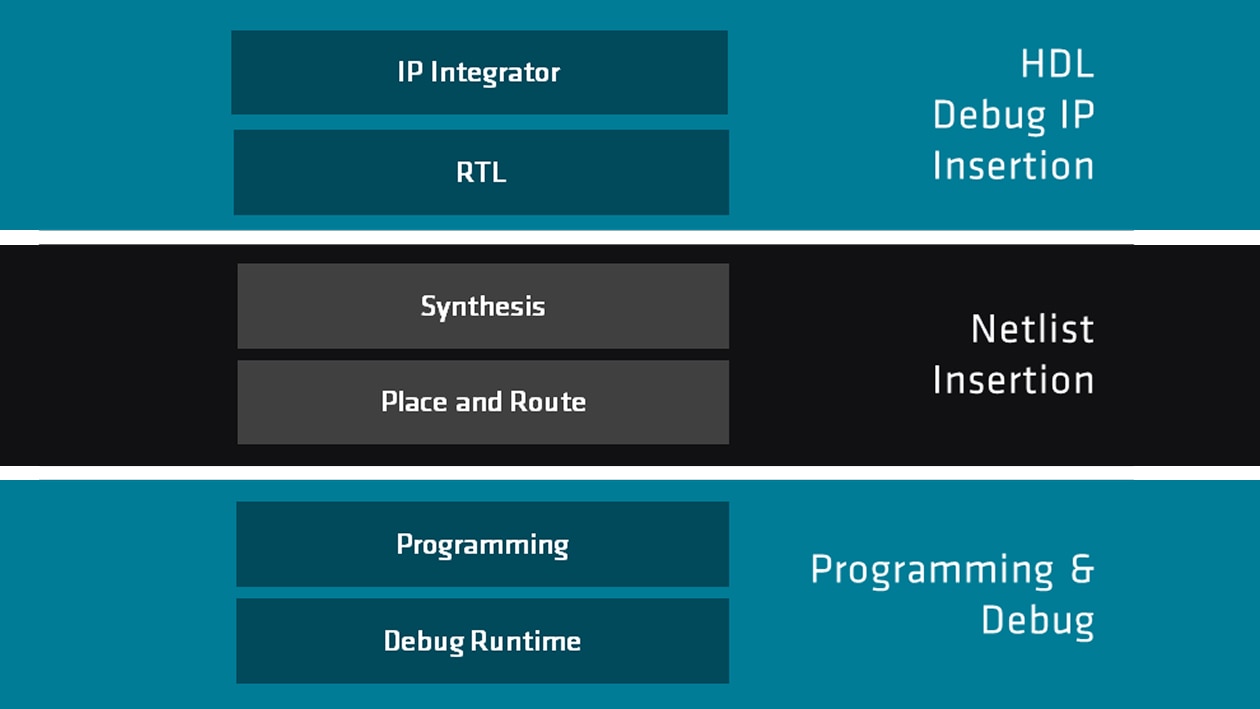

Umfassender Debugging-Flow

Flexible Methoden für die Instrumentierung von Debugging-IP, Designanalyse, Laufzeitkonfiguration und inkrementelles Kompilieren für schnelle Debugging-Läufe.

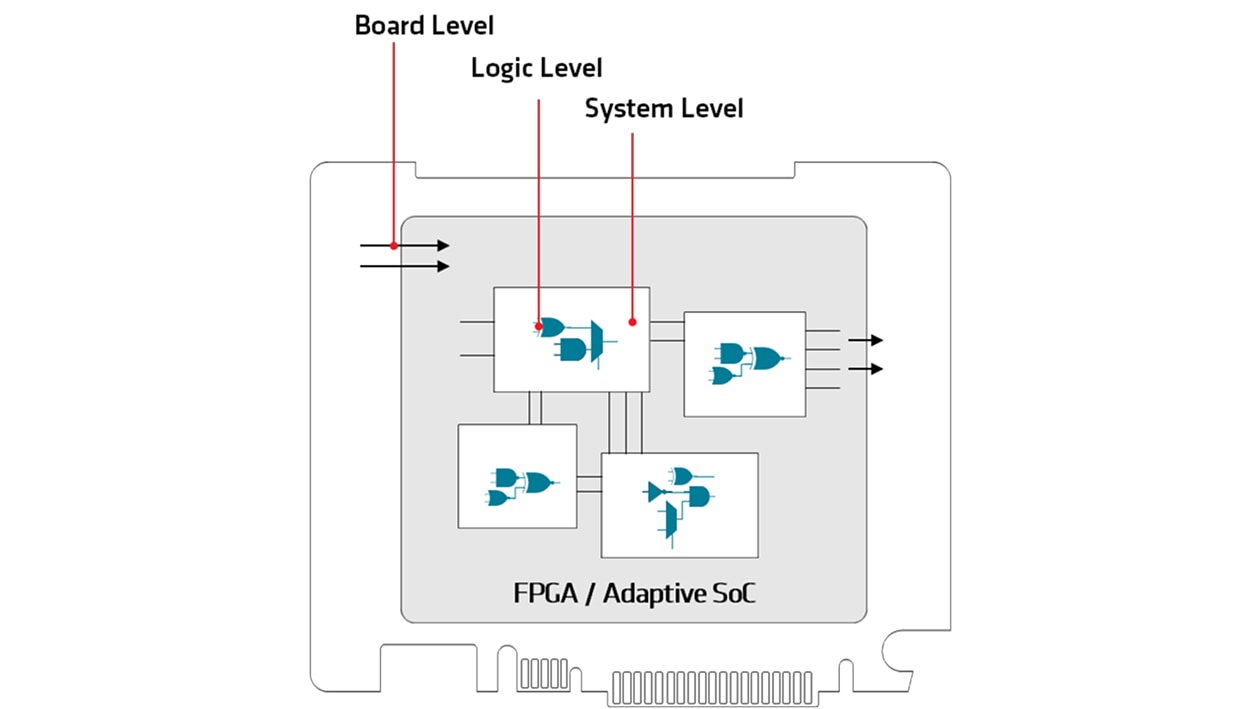

Systemtransparenz

ChipScope bietet mehrere Abstraktionsebenen für die Analyse Ihres Systems mit umfassender IP für maximale Transparenz.

- Debugging auf Logikebene: IPA-Kerne (Integrated Logic Analyzer) bieten erweiterte Triggerung interner Signale und Erfassungsfunktionen zur Fehlerbehebung in Echtzeit.

- Debugging auf Systemebene: Unterstützung von AXI-Schnittstellen und I/O-Protokollen ermöglicht die Prüfung mehrerer Designblöcke auf Transaktionsebene.

- Debugging auf Platinenebene: Untersuchen Sie die Interaktion auf Platinenebene mit virtuellen I/O-Kernen (VIO). Sie ermöglichen Signalüberwachung und die Injektion von Testwerten, um das Verhalten des Designs zu überprüfen.

Debugging-IP

Sehr wichtig für den Fabric-Debug-Flow ist ein Satz von IP-Kernen, die für Transparenz des Designs sorgen, ohne die Designfunktionalität zu beeinträchtigen. Alle AMD Debugging-IP ist sowohl online als auch über den IP-Katalog in der Vivado Design Suite verfügbar. Beachten Sie, dass das Debugging der programmierbaren Logik für adaptive Versal™ SoCs ausschließlich AXI-basiert erfolgt.

FPGAs und adaptive Zynq™ SoCs |

Adaptive AMD Versal SoCs |

|

Integrated Logic Analyzer (ILA) |

||

System-ILA |

||

Virtual Input/Output (VIO) |

||

BSCAN-zu-JTAG-Converter |

– |

|

Debugging Hub* |

System Debug Bus (XSDB) – integriert |

*Debug Hub erleichtert die Kommunikation mit Debug-IP-Kernen über JTAG.

Datenkabelmodule

AMD bietet eine Reihe von Datenkabeln entweder für Standard-JTAG-Debugging und Hochgeschwindigkeits-Debugging heterogener Systeme an. Ganz gleich, ob Sie hauptsächlich große Datenmengen erfassen, die Nutzung von Chipressourcen minimieren oder eine schnellere Debugging-Leistung erzielen möchten, die Wahl des richtigen Datenkabels kann sich auf die Effizienz Ihres Workflows auswirken.

Neben Datenkabelmodulen bieten die meisten Evaluierungskits integrierte USB-zu-JTAG-Debugging-Schnittstellen. Ausgewählte Chipfamilien bieten außerdem Debugging über Ethernet oder PCI-Express®. In der nachstehenden Tabelle finden Sie weitere Informationen zu Datenkabelmodulen.

| Geräteunterstützung | Plattformkabel USB II | SmartLynq | SmartLynq+ |

|---|---|---|---|

| AMD FPGAs | ✓ | ✓ | |

| Adaptive Zynq SoCs | ✓ | ✓ | |

| Adaptive Versal SoCs | ✓ | ✓ |

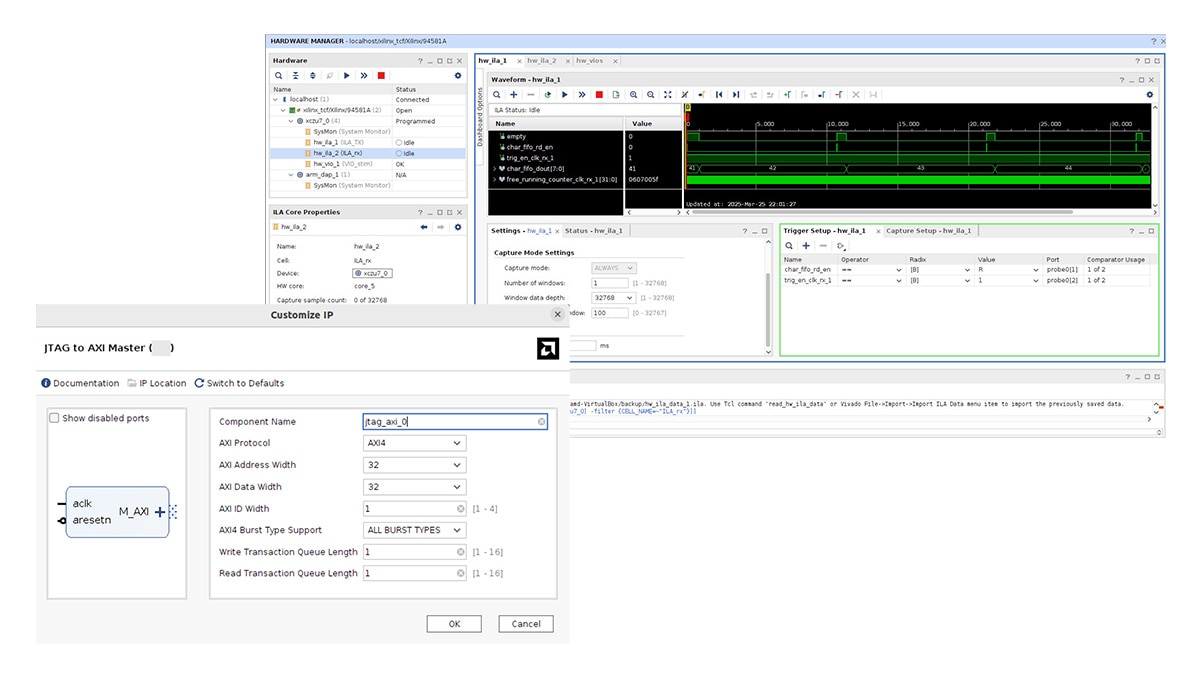

Designanalyse

ChipScope bietet verschiedene Schnittstellen und Automatisierungsmethoden für Debug- und Trace-Funktionen innerhalb des Systems. In der Vivado IDE können Designer nahtlos zwischen High-Level-Wellenformen und Designelementen navigieren und die Interaktion über TCL oder Python automatisieren.

- Komplexe Triggerung: Legen Sie Trigger auf mehreren Ebenen mit zustandsbasierten Abhängigkeiten fest, um komplexe Designszenarien zu reproduzieren.

- Cross-Probing: Die Möglichkeit, Kreuzreferenzen vom Debugging-Output zu RTL oder einer Netzliste zu erstellen, um die Grundursache von Designfehlern zu analysieren und zu identifizieren.

- Wellenformanalyse: Zeigt erfasste Signalübergänge an und bietet die Möglichkeit, Triggerinformationen mit Kommentaren zu versehen und bis zur Designquelle zurückzuverfolgen.

- Protokoll-Debugging: Protokollspezifische Analyse mit Transaktionszeitachsen, um Engpässe zu erkennen und Kreuzreferenzen von Protokollereignissen zu RTL zu erstellen.

- VIO-Schnittstelle: Ansteuerung von Signalen für interaktive Tests und Überwachung ohne das Design stoppen oder neu programmieren zu müssen.

Schnelle Debugging-Läufe

Inkrementelle Flows

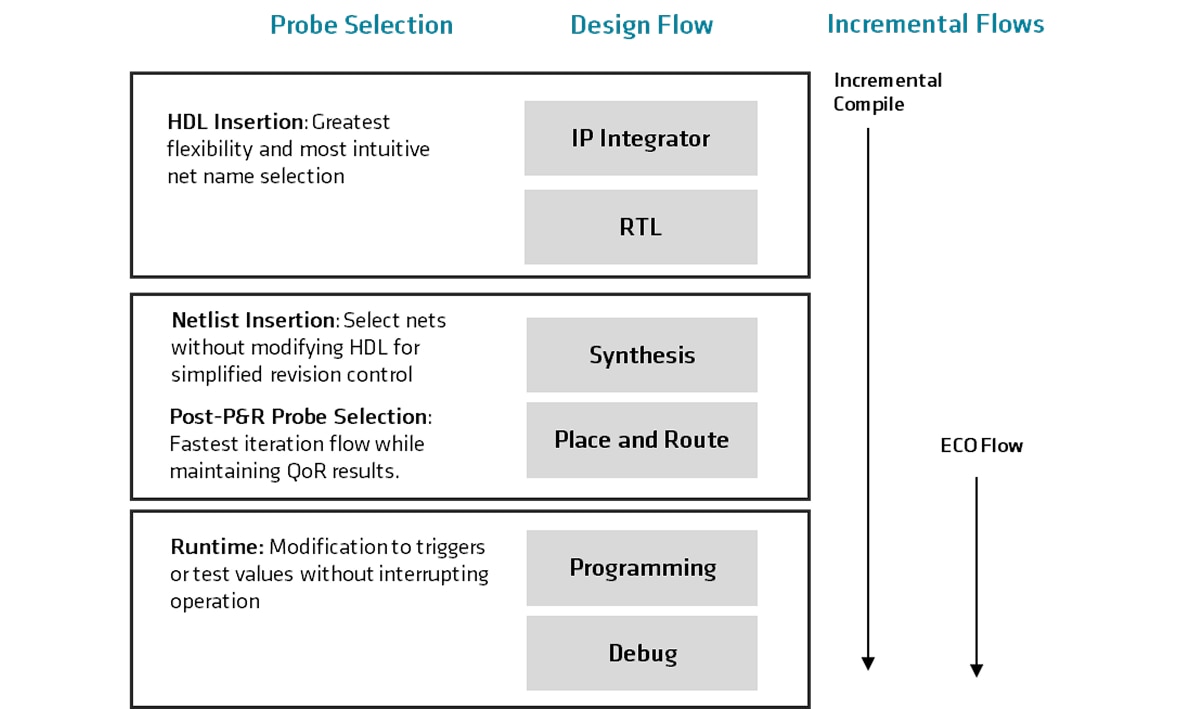

Wenn Fehler entdeckt werden, ist die Änderung von Trigger-, Sonden- und Debugging-Kernen nicht zu vermeiden. Daher ist schnelle Iterationen ein kritischer Faktor. ChipScope nutzt mehrere Arten inkrementeller Kompilier-Flows, damit nur die angepassten Teile des Designs ändert werden. Dadurch wird eine vollständige Neuerstellung bei den Debugging-Zyklen vermieden.

Je nachdem, welche Methode der Debugging-Instrumentierung verwendet wird, stehen mehrere inkrementelle Flows zur Verfügung:

- Incremental Compile: Führt Synthese und P&R für geänderte Teile des Designs durch

- ECO Flow: Für die Probe-Auswahl nach dem Post-and-Route – ideal für kleinere Änderungen und die schnellste Iterationsmethode bei maximaler Erhaltung des vorhandenen Designs

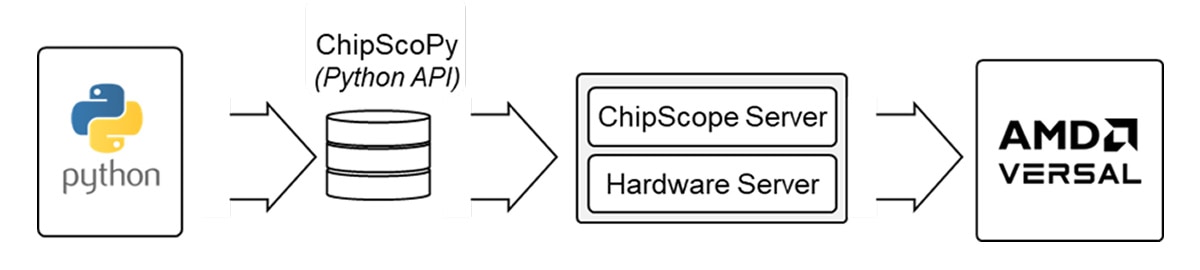

ChipScoPy Python-API für Automatisierung

Für Versal Chips ist ChipScoPy eine einfache Python-Schnittstelle zur Automatisierung von ChipScope-Funktionen ohne Vivado IDE. Dies ermöglicht eine verbesserte Automatisierung und Steuerung des Debuggings für programmierbare Logik und verschiedene Hard-IP.

Dies bietet u. a. folgende Vorteile:

- Flexibler und benutzeranpassbarer Flow, der vollständig skriptfähig ist

- Erweiterbarer Flow, der Drittanbieter- und Open-Source-Pakete wie Plot Viewer verwenden kann

- Geringerer Platzbedarf für die Installation, da Installation des Vivado Tools nicht erforderlich ist