-

Funciones y beneficios clave del integrador de IP Vivado

- Estrecha integración dentro del entorno de diseño integrado Vivado

- Inclusión sin interrupciones de los subsistemas jerárquicos del integrador de IP en el diseño general

- Captura y empaquetado rápidos de diseños del integrador de IP para la reutilización

- Compatibilidad para flujos de diseño gráficos y basados en Tcl

- Rápida simulación y cross-probing (sondeo cruzado) entre múltiples vistas de diseño

- Compatibilidad para todos los dominios de diseño

- Compatibilidad para diseños de procesador o sin procesador

- Integración de algorítmicos (Vitis HLS y Model Composer) e IP de nivel RTL

- Combinación de DSP, video, sistemas analógicos, integración, conectividad y lógica

- Compatibilidad para flujo DFX basado en proyectos

- Enfoque en la productividad del diseñador

- DRC en conexiones complejas de nivel de interfaz durante el ensamblaje del diseño

- Reconocimiento y corrección de errores comunes de diseño

- Propagación automática de parámetros IP a IP interconectada

- Optimizaciones a nivel de sistema

- Asistencia automatizada del diseñador

- Asistencia de colaboración mejorada

- Asistencia de colaboración mejorada

- Los diseños basados en equipos que utilizan el contenedor de diseño de bloques permiten la reutilización y los diseños modulares

- Mejoras de control de revisión que separan los archivos de origen de los archivos generados

- Herramienta de diferencia de diseño de bloques para comparar dos diseños de bloques

Funciones de diseño de alto nivel

Te presentamos una descripción general rápida de las funciones de Vivado™ Design Suite para acelerar el diseño de alto nivel. Haz clic en las otras pestañas para conocer detalles completos de la función.

- HLS de Vitis

- Integrador de IP

- Shell abstracta

- Model Composer Vitis

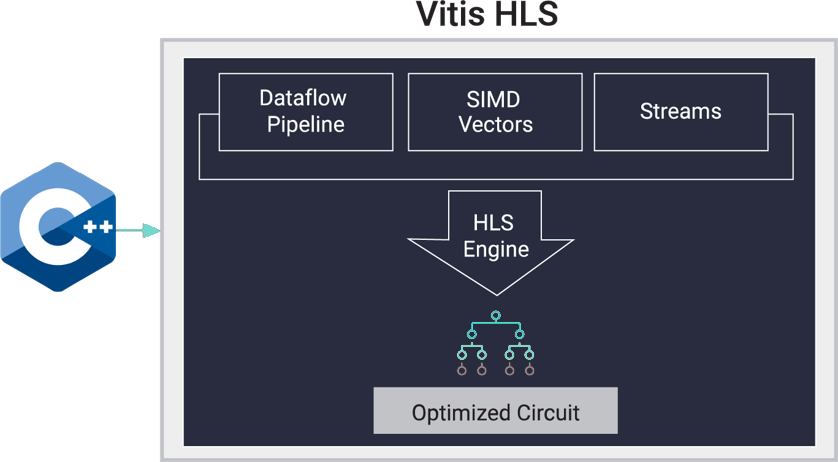

Herramienta de síntesis de alto nivel Vitis

Los algoritmos avanzados utilizados hoy en aplicaciones de IA, inalámbricas, médicas, de defensa y de consumo son más sofisticados que nunca. La herramienta de síntesis de alto nivel Vitis™, incluida como una actualización gratuita en todas las ediciones Vivado™, acelera la creación de IP, ya que permite que las especificaciones de C++ se dirijan de forma directa a dispositivos programables AMD sin la necesidad de crear manualmente diseños RTL equivalentes. La herramienta de HLS (High-Level Synthesis, síntesis de alto nivel) de Vitis es compatible con los entornos de diseño Vitis y Vivado, y permite a los diseñadores de software y hardware acelerar la creación de kernel o IP a través de:

- Abstracción de descripciones algorítmicas, especificaciones de tipo de datos con enteros de punto fijo o de punto flotante, e interfaces (FIFO, memorias y AXI4)

- Amplias bibliotecas a fin de incluir compatibilidad integrada para tipos de datos de precisión arbitraria, streams y tipos de datos vectorizados

- Síntesis impulsada por directivas y consciente de la arquitectura con QoR (Quality of Results, calidad de los resultados) alta

- Tiempo rápido para QoR comparable con RTL codificado a mano

- Verificación acelerada mediante simulación de banco de pruebas C/C++ y simulación automática VHDL o Verilog y generación de bancos de pruebas

- Uso automático de memorias en el chip AMD y elementos de DSP (Digital Signal Processing, procesamiento de señales digitales), incluso para tipos de punto flotante

Bibliotecas

Las siguientes bibliotecas integradas se incluyen en la herramienta Vitis HLS:

| Nombre | Descripción |

|---|---|

Tipos de datos de precisión arbitraria |

Tipos de entero y punto fijo (ap_int.h) |

Streams HLS |

Modelos para estructuras de streaming de datos, diseñados a fin de obtener el mejor rendimiento y área (hls_stream.h) |

Tipos de vectores |

Tipos y operaciones vectorizadas (hls_vector.h), incluso para tipos de precisión arbitraria |

HLS Matemáticas |

Amplia compatibilidad para la síntesis de bibliotecas matemáticas estándar C (math.h) y C++ (cmath.h). La compatibilidad incluye funciones de punto flotante y punto fijo: abs, atan, atanf, atan2, atan2, ceil, ceilf, copysign, copysignf, cos, cosf, coshf, expf, fabs, fabsf, floorf, fmax, fmin, logf, fpclassify, isfinite, isinf, isnan, isnormal, log, log10, modf, modff, recip, recipf, round, rsqrt, rsqrtf, 1/sqrt, signbit, sin, sincos, sincosf, sinf, sinhf, sqrt, tan, tanf, trunc |

La herramienta Vitis HLS también admite las bibliotecas de rendimiento optimizado de Vitis disponibles en GitHub con aceleración lista para usar y cambios de código de mínimos a nulos en las aplicaciones existentes. Estas bibliotecas aceleradas comunes de Vitis incluyen matemáticas avanzadas, estadísticas, álgebra lineal y DSP a fin de ofrecer funcionalidades básicas para una amplia gama de aplicaciones. Estas bibliotecas ofrecen aceleración para cargas de trabajo como procesamiento de imágenes y visión con funciones OpenCV, finanzas cuantitativas, bases de datos, análisis de datos, compresión de datos y más.

Para obtener más información, visita el sitio de Vitis HLS.

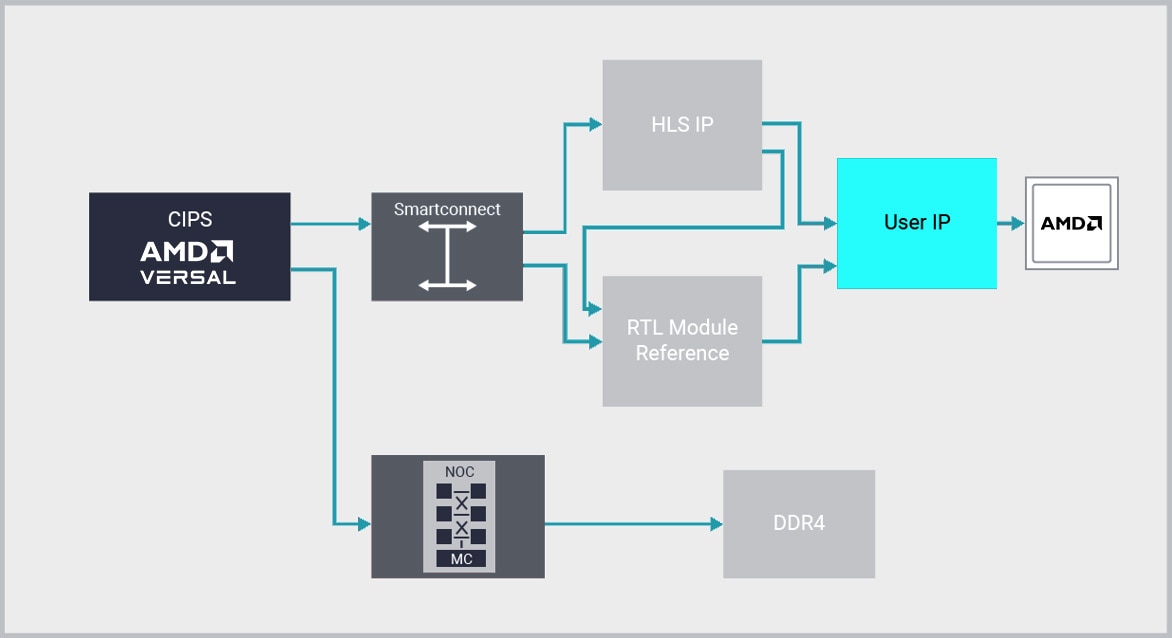

Integrador de IP

Vivado™ Design Suite rompe el estancamiento de la productividad del diseño RTL mediante la entrega del primer entorno de diseño de integración IP de conexión rápida (plug-and-play) de la industria, con su función de integrador de IP.

El integrador de IP Vivado proporciona un flujo de desarrollo de diseño gráfico y basado en Tcl, correcto por construcción. Proporciona un entorno interactivo consciente del dispositivo y la plataforma que admite la conexión automática inteligente de interfaces IP clave, generación de subsistemas IP con un solo clic, DRC en tiempo real y propagación de cambios de interfaz, combinado con una potente capacidad de depuración.

Los diseñadores trabajan en el nivel de abstracción de “interfaz” y no de “señal” cuando hacen conexiones entre IP, lo que aumenta enormemente la productividad. A menudo, utilizan para esto interfaces AXI4 estándar de la industria, pero muchas otras interfaces también son compatibles con el integrador de IP.

Trabajando a nivel de interfaz, los equipos de diseño pueden ensamblar rápidamente sistemas complejos que utilizan la IP creada con Vitis HLS, Model Composer, AMD SmartCore™ y LogiCORE™ IP, la IP de miembro de Alliance, así como tu propia IP. Al aprovechar la combinación de IPI (Inter-Processor Interrupt, interrupciones entre procesadores) y HLS de Vivado, los clientes ahorran hasta 15 veces en costos de desarrollo en comparación con un enfoque RTL.

Generación de IP basada en C con síntesis de alto nivel de Vitis y Vitis Model Composer

Como proveedor líder de herramientas de diseño de nivel de sistema electrónico para soluciones programables, Vivado ofrece síntesis de alto nivel Vitis™ para C, C++ y SystemC, y puedes comprar el complemento Vitis Model Composer para DSP. Estas soluciones permiten sintetizar directamente especificaciones IP de alto nivel en VHDL y Verilog, lo que acelera la verificación IP más de 100 veces y la creación de RTL hasta cuatro veces. Las herramientas altamente integradas se pueden utilizar en forma individual o en combinación, por lo que generan una IP reutilizable para su uso en Vivado ML Suite.

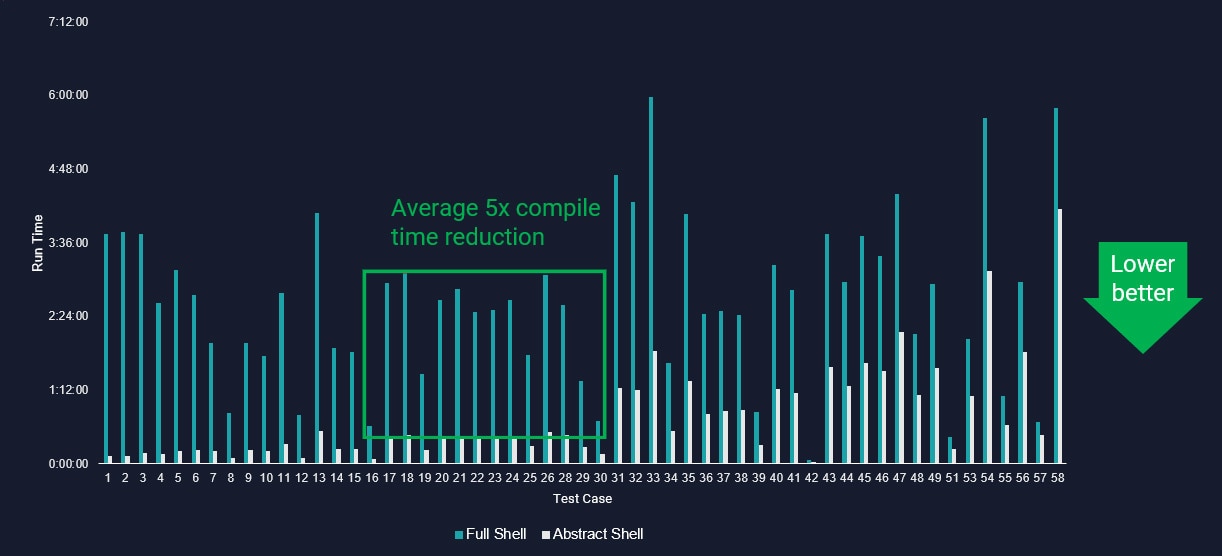

Compilación rápida usando la shell abstracta

La shell abstracta es una nueva tecnología que permite compilar rápidamente diseños complejos y grandes. Permite a los usuarios definir módulos reconfigurables dentro de un diseño para ser compilado de forma independiente. Los usuarios pueden seleccionar partes del diseño para modificar y recompilar sin tener que recompilar todo el diseño.

La shell abstracta permite una reducción media del tiempo de compilación de cinco veces y hasta 17 veces en comparación con una compilación tradicional. Estas funciones también permiten a los usuarios definir múltiples módulos dentro del diseño que se pueden compilar en paralelo.

Características principales

La shell abstracta permite a los usuarios:

- Reducir el tiempo de ejecución y el uso de memoria para cada compilación de módulos reconfigurables

- Implementar todos los módulos reconfigurables en paralelo para múltiples particiones reconfigurables

- Ocultar cualquier información propietaria que exista dentro del diseño estático

- Evitar la comprobación de licencia para cualquier IP que exista en el diseño estático

- Distribuir particiones reconfigurables entre varios equipos para la colaboración de diseño basada en equipos

Testimonios

Model Composer Vitis

Vitis™ Model Composer es una herramienta de diseño basada en modelos que permite una exploración rápida del diseño dentro de los entornos MathWorks MATLAB® y Simulink® y acelera el camino hacia la producción en dispositivos AMD a través de la generación automática de código. Puedes diseñar tus algoritmos e iterar a través de ellos mediante bloques de alto nivel y rendimiento optimizado y validar la corrección funcional a través de simulaciones a nivel del sistema. Vitis Model Composer transforma tu diseño en una implementación de calidad de producción a través de optimizaciones automáticas. La herramienta proporciona una biblioteca de más de 200 bloques de HDL (Hardware Description Language, lenguaje de descripción de hardware), HLS y motor de IA para el diseño e implementación de algoritmos en dispositivos AMD. También permite importar código HDL, HLS y de motor de IA personalizado como bloques en la herramienta. Vitis Model Composer incluye toda la funcionalidad de AMD System Generator for DSP, que ya no se entrega como herramienta independiente desde la versión 2020.2.

En Vitis Model Composer puedes:

- Crear un diseño mediante bloques optimizados dirigidos a motores de IA y lógica programable.

- Visualizar y analizar los resultados de la simulación y comparar la salida con las referencias doradas generadas con MALTAB® y Simulink®.

- Simular de forma conjunta y sin interrupciones los bloques de motores de IA y lógica programable (HLS, HDL).

- Generar automáticamente código (gráfico de flujo de datos de motores de IA, RTL y HLS C++) y banco de pruebas para un diseño.

- Importar código personalizado de HLS, motores de IA y RTL en forma de bloques.

Nota:

Vitis Model Composer se puede comprar como una licencia adicional para cualquier edición de Vivado Design Suite.

Para obtener más información sobre cómo descargar y comprar la herramienta, visita la página Vitis Model Composer.

Características principales

-

Acelera las iteraciones de diseño

- Alto nivel de abstracción:

Los bloques de compilación centrados en algoritmos, con un enfoque en la funcionalidad, proporcionan una facilidad de uso esencial para que los expertos en dominios aceleren la exploración del diseño.

- Compatibilidad para vectores y matrices:

Permite el diseño de algoritmos basados en tramas que ahorra tiempo y esfuerzo a fin de pasar a un modelo intermedio de bajo nivel para la implementación.

- Bibliotecas específicas de la aplicación:

Las bibliotecas de DSP, visión artificial, matemáticas y álgebra lineal de rendimiento optimizado están disponibles como bloques para la simulación y la implementación de alto rendimiento en dispositivos AMD.

- Importa C/C++ sintetizable como bloques personalizados:

La capacidad de crear tus propios bloques personalizados para la simulación y la generación de código proporciona una mayor flexibilidad para diseñar algoritmos diferenciados

- Integración sin interrupciones con Simulink:

La conexión directa con bloques de la familia de productos Simulink permite el modelado y la simulación a nivel de sistema y la capacidad de aprovechar al máximo las capacidades de generación de estímulos y visualización de datos del entorno gráfico de Simulink.

- Compatibilidad con enteros, flotantes y punto fijo:

Admite los tipos de datos nativos flotantes y enteros en Simulink y los tipos de datos de punto fijo y medios compatibles con Vitis HLS.

-

Transforma el algoritmo en arquitectura

- Optimizaciones automáticas:

Analiza la especificación algorítmica en Simulink y realiza optimizaciones automáticas para dirigirse hacia una microarquitectura que optimiza el rendimiento, reduce la utilización de bloques de RAM y permite la ejecución simultánea de bloques.

- Acelera la creación de IP:

Transforma tus diseños simulados en un paquete de IP RTL que puedes usar dentro del integrador de IP Vivado y aprovecha todos los beneficios de su entorno de diseño de integración de IP de conexión rápida (plug-and-play) para diseños complejos.

- Amplía a System Generator for DSP:

Aprovecha los beneficios de la facilidad de uso y la velocidad de simulación de Model Composer para partes del diseño y exporta el RTL sintetizado a los diseños existentes de System Generator for DSP en forma de nuevos bloques personalizados.

- Exporta a Vitis HLS:

Función avanzada que proporciona un enlace entre el entorno gráfico de Simulink para diseñar, simular y validar tus algoritmos y Vitis HLS, lo que genera automáticamente todo lo que necesitarías para optimizar aún más el algoritmo, incluidos los vectores de prueba registrados desde la simulación.

- Interfaz de usuario para mapear interfaces RTL:

Interfaz gráfica fácil de usar para asignar las entradas y salidas en tu diseño a interfaces RTL compatibles (AXI4-Lite, AXI4-Stream, AXI4-Stream Video, FIFO, Block RAM) y formatos de video (AXI4-Stream Video) para la implementación.

Generación automática del banco de prueba: Registro automático de vectores de prueba a partir de la simulación y generación de un banco de prueba para verificar la equivalencia funcional entre el diseño ejecutable y el código generado.

- Compatibilidad con enteros, flotantes y punto fijo:

Admite los tipos de datos nativos flotantes y enteros en Simulink y los tipos de datos de punto fijo y medios compatibles con Vitis HLS.