-

Vivado IP Integrator의 주요 특징 및 이점

- Vivado 통합 설계 환경에서의 긴밀한 통합

- IP Integrator 계층적 하위 시스템을 전체 설계에 원활하게 포함

- 재사용을 위한 IP Integrator 설계의 신속한 캡처 및 패키징

- 그래픽 및 Tcl 기반 설계 흐름 지원

- 여러 설계 뷰 간의 빠른 시뮬레이션 및 크로스 프로빙

- 모든 설계 도메인 지원

- 프로세서 또는 비프로세서 설계 지원

- 알고리즘(Vitis HLS 및 모델 컴포저) 및 RTL 수준 IP 통합

- DSP, 비디오, 아날로그, 내장형, 연결, 로직의 조합

- 프로젝트 기반 DFX 흐름 지원

- 설계자 생산성에 집중

- 설계 결합 중 복잡한 인터페이스 수준 연결에 대한 DRC

- 일반적인 설계 오류 인식 및 수정

- 상호 연결된 IP로 IP 매개변수 자동 전파

- 시스템 수준 최적화

- 자동화된 설계 지원

- 강화된 협업 지원

- 강화된 협업 지원

- 블록 디자인 컨테이너를 사용한 팀 기반 설계로 재사용성과 모듈식 설계 가능

- 소스 파일과 생성된 파일을 분리하는 개정 제어 개선

- 두 블록 디자인을 비교하는 블록 디자인 차이 도구

고급 설계 기능

다음은 고급 설계 가속화를 위한 Vivado™ Design Suite 기능에 대한 간략한 개요입니다. 전체 기능에 대한 세부 정보를 보려면 다른 탭을 클릭하세요.

- Vitis HLS

- IP Integrator

- 추상 셸

- Vitis 모델 컴포저

Vitis High-Level Synthesis 도구

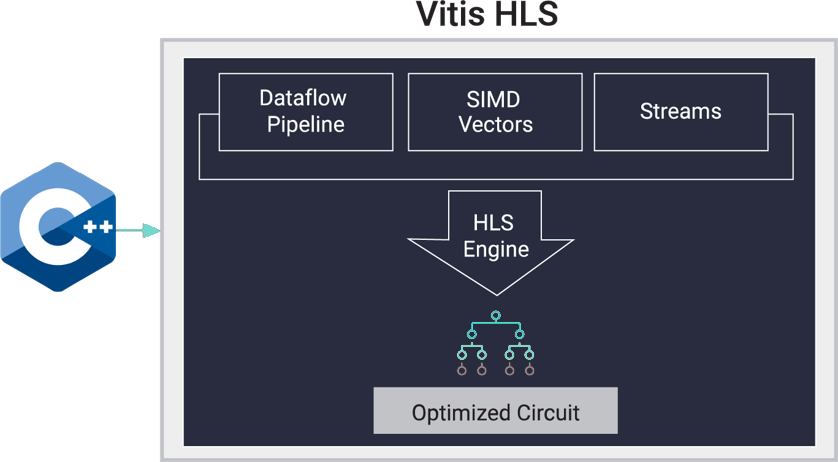

오늘날 AI, 무선, 의료, 국방, 소비자 응용 분야에서 사용되는 고급 알고리즘은 그 어느 때보다 정교해졌습니다. 모든 Vivado™ 에디션에 무료 업그레이드로 포함된 Vitis™ High-Level Synthesis 도구는 동등한 RTL 설계를 수동으로 만들 필요 없이 C++ 사양을 AMD 프로그래밍 가능 디바이스에 직접 타겟팅할 수 있도록 하여 IP 생성을 가속화합니다. Vitis HLS 도구는 Vitis 및 Vivado 설계 환경을 모두 지원하며, 이 도구를 사용하면 소프트웨어 및 하드웨어 설계자 모두 다음을 통해 커널 또는 IP 생성을 가속화할 수 있습니다.

- 알고리즘 설명의 추상화, 고정 소수점 또는 부동 소수점 정수를 사용한 데이터 유형 사양, 인터페이스(FIFO, 메모리, AXI4)

- 임의 정밀도 데이터 유형, 스트림, 벡터화된 데이터 유형에 대한 기본 제공 지원을 포함하는 광범위한 라이브러리

- 높은 QoR의 지시문 기반 아키텍처 인식 합성

- 직접 코딩된 RTL에 필적하는 빠른 QoR 시간

- C/C++ 테스트 벤치 시뮬레이션과 자동 VHDL 또는 Verilog 시뮬레이션 및 테스트 벤치 생성을 사용한 가속화된 검증

- 부동 소수점 유형을 포함한 AMD 온칩 메모리 및 DSP(Digital Signal Processing) 요소의 자동 사용

라이브러리

Vitis HLS 도구에는 다음과 같은 기본 제공 라이브러리가 포함되어 있습니다.

| 이름 | 설명 |

|---|---|

임의 정밀도 데이터 유형 |

정수 및 고정 소수점(ap_int.h) 유형 |

HLS 스트림 |

최상의 성능과 영역(hls_stream.h)을 얻도록 설계된 스트리밍 데이터 구조용 모델 |

벡터 유형 |

임의 정밀도 유형을 포함한 벡터화된 유형 및 연산(hls_vector.h) |

HLS 수학 |

표준 C(math.h) 및 C++(cmath.h) 수학 라이브러리의 합성에 대한 광범위한 지원. 지원에 포함되는 부동 소수점 및 고정 소수점 함수: abs, atan, atanf, atan2, atan2, ceil, ceilf, copysign, copysignf, cos, cosf, coshf, expf, fabs, fabsf, floorf, fmax, fmin, logf, fpclassify, isfinite, isinf, isnan, isnormal, log, log10, modf, modff, recip, recipf, round, rsqrt, rsqrtf, 1/sqrt, signbit, sin, sincos, sincosf, sinf, sinhf, sqrt, tan, tanf, trunc |

또한 Vitis HLS 도구는 GitHub에서 사용 가능한 Vitis 성능 최적화 라이브러리를 지원하며, 이 라이브러리를 사용하면 즉각적인 가속화가 가능하고 기존 애플리케이션의 코드 변경이 최소한만 필요하거나 전혀 필요하지 않습니다. 이러한 공통 Vitis 가속 라이브러리는 고급 수학, 통계, 선형 대수학, DSP를 포함하여 광범위한 응용 분야에 핵심 기능을 제공합니다. 이러한 라이브러리는 OpenCV 함수, 정량 금융, 데이터베이스, 데이터 분석, 데이터 압축 등을 통해 비전 및 이미지 처리와 같은 워크로드를 위한 가속화를 제공합니다.

자세한 내용은 Vitis HLS 사이트를 참조하세요.

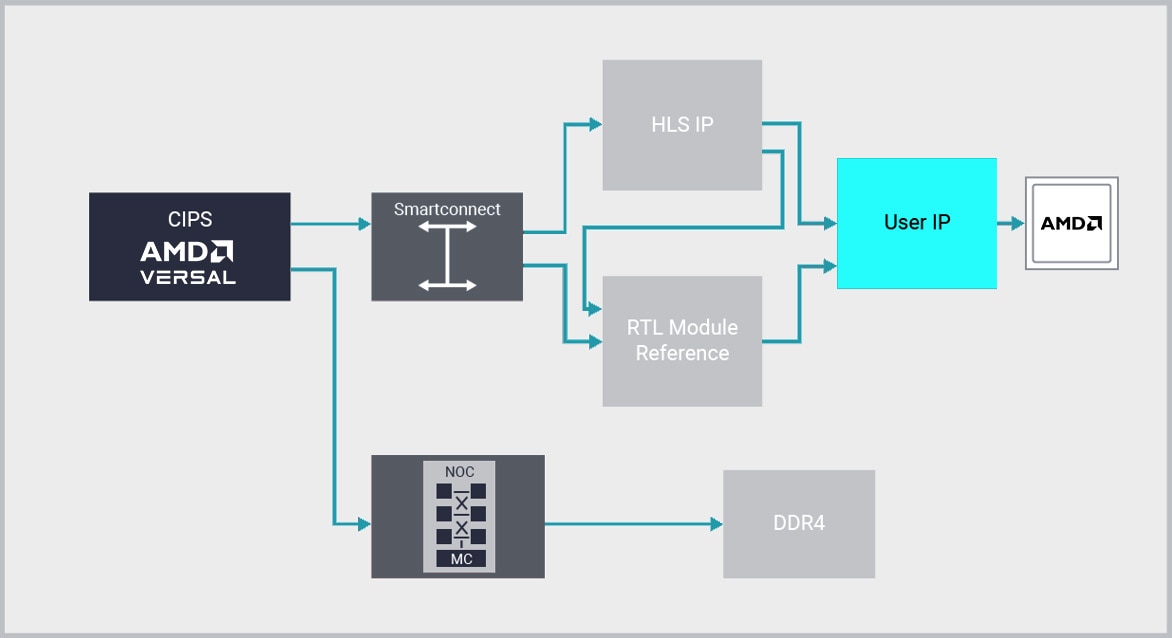

IP Integrator

Vivado™ Design Suite는 IP Integrator 기능을 통해 업계 최초의 플러그 앤 플레이 IP 통합 설계 환경을 제공함으로써 RTL 설계 생산성 수준을 한층 높여줍니다.

Vivado IP Integrator는 그래픽 및 Tcl 기반의 CbC(Correct-by-Construction) 설계 개발 흐름을 제공합니다. 주요 IP 인터페이스의 지능형 자동 연결, 원클릭 IP 하위 시스템 생성, 실시간 DRC, 인터페이스 변경 전파를 지원하며 강력한 디버그 기능이 결합된 디바이스 및 플랫폼 인식 대화형 환경을 제공합니다.

설계자가 IP 간 연결을 만들 때 추상화의 "신호" 수준이 아닌 "인터페이스"에서 작업하므로 생산성이 크게 향상됩니다. 산업 표준 AXI4 인터페이스를 사용하는 경우가 많지만 IP Integrator는 기타 수십 가지의 인터페이스도 지원합니다.

인터페이스 수준에서 작업하는 설계 팀은 자체 IP뿐만 아니라 Vitis HLS, 모델 컴포저, AMD SmartCore™, LogiCORE™ IP, Alliance Member IP로 만든 IP도 활용하여 복잡한 시스템을 빠르게 조립할 수 있습니다. Vivado IPI와 HLS의 조합을 활용함으로써 고객은 RTL 접근 방식에 비해 개발 비용을 최대 15배 절감할 수 있습니다.

Vitis High-Level Synthesis 및 Vitis 모델 컴포저를 사용한 C 기반 IP 생성

프로그래밍 가능한 솔루션을 위한 전자 시스템 수준 설계 도구의 선도적인 제공업체인 Vivado는 C, C++ 및 SystemC를 위한 Vitis™ High-Level Synthesis를 제공하며, DSP용 애드온 Vitis 모델 컴포저를 구매할 수 있습니다. 이러한 솔루션을 통해 고급 IP 사양을 VHDL 및 Verilog로 직접 합성하여 100배 이상의 IP 검증 및 RTL 생성 속도를 최대 4배 높일 수 있습니다. 고도로 통합된 도구는 개별적으로 또는 조합하여 사용할 수 있으며, 그 결과 Vivado ML 제품군에서 사용할 수 있는 재사용 가능한 IP가 생성됩니다.

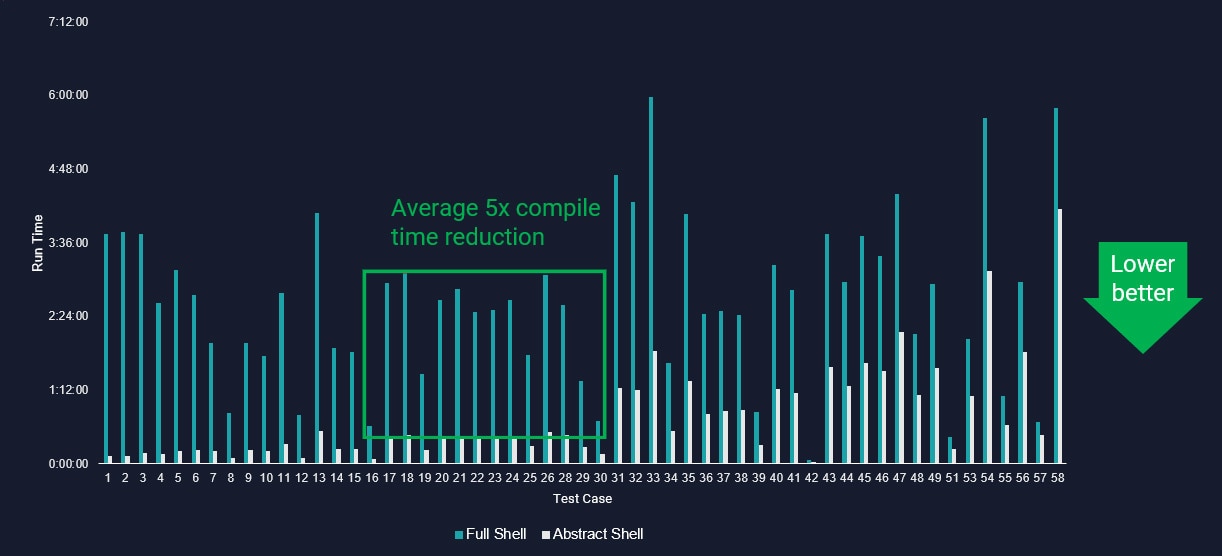

추상 셸을 사용한 빠른 컴파일

주요 특징

이용 후기

Vitis 모델 컴포저

Vitis™ 모델 컴포저는 MathWorks MATLAB® 및 Simulink® 환경 내에서 신속한 설계 탐색을 지원하고 자동 코드 생성을 통해 AMD 디바이스에서 생산 과정을 가속화하는 모델 기반 설계 도구입니다. 높은 수준의 성능 최적화 블록을 사용하여 알고리즘을 설계하고 반복할 수 있으며, 시스템 수준 시뮬레이션을 통해 기능적 정확성을 검증할 수 있습니다. Vitis 모델 컴포저는 자동 최적화를 통해 설계를 생산 수준의 구현으로 변환합니다. 이 도구는 AMD 디바이스에서 알고리즘의 설계 및 구현을 위한 200여 개 HDL, HLS, AI 엔진 블록의 라이브러리를 제공합니다. 이 도구를 통해 맞춤형 HDL, HLS, AI 엔진 코드를 블록으로 도구에 가져올 수도 있습니다. Vitis 모델 컴포저는 DSP용 AMD System Generator의 모든 기능을 포함하고 있으며, 버전 2020.2 이후에는 더 이상 독립형 도구로 제공되지 않습니다.

Vitis 모델 컴포저에서 수행할 수 있는 작업은 다음과 같습니다.

- AI 엔진 및 프로그래밍 가능 로직을 대상으로 최적화된 블록을 사용하여 설계 생성

- 시뮬레이션 결과를 시각화 및 분석하고 MALTAB® 및 Simulink®를 사용하여 생성된 골든 레퍼런스와 결과 비교

- AI 엔진 및 프로그래밍 가능 로직(HLS, HDL) 블록을 원활하게 공동 시뮬레이션

- 설계를 위한 코드(AI 엔진 데이터 흐름 그래프, RTL, HLS C++) 및 테스트 벤치 자동 생성

- 맞춤형 HLS, AI 엔진, RTL 코드를 블록으로 가져오기

참고:

Vitis 모델 컴포저는 모든 Vivado Design Suite 에디션의 애드온 라이선스로 구매할 수 있습니다.

다운로드 및 구매 방법에 대한 자세한 내용은 Vitis 모델 컴포저 페이지를 참조하세요.

주요 특징

-

설계 반복 가속화

- 높은 수준의 추상화:

기능에 중점을 둔 알고리즘 중심의 빌딩 블록은 도메인 전문가가 설계 탐색을 가속화하는 데 필수적인 사용 편의성을 제공합니다.

- 벡터 및 행렬 지원:

프레임 기반 알고리즘 설계가 가능하므로 구현을 위해 중급 저수준 모델로 이동하는 데 드는 시간과 노력을 절약할 수 있습니다.

- 애플리케이션별 라이브러리:

AMD 디바이스에서 시뮬레이션 및 고성능 구현을 위한 블록으로 사용할 수 있는 성능 최적화 DSP, 컴퓨터 비전, 수학, 선형 대수학 라이브러리입니다.

- 합성 가능한 C/C++를 맞춤형 블록으로 가져오기:

시뮬레이션 및 코드 생성을 위한 맞춤형 블록을 만들 수 있으므로 차별화된 알고리즘을 설계할 수 있는 유연성이 향상됩니다.

- Simulink와의 원활한 통합:

Simulink 제품군의 블록과 직접 연결하면 시스템 수준 모델링 및 시뮬레이션이 가능하며 Simulink 그래픽 환경의 자극 생성 및 데이터 시각화 기능을 완전히 활용할 수 있습니다.

- 정수, 부동 소수점 및 고정 소수점 지원:

Simulink의 네이티브 부동 및 정수 데이터 형식과 Vitis HLS에서 지원하는 고정 소수점 및 half 데이터 형식을 지원합니다.

-

알고리즘을 아키텍처로 변환

- 자동 최적화:

Simulink 내에서 알고리즘 사양을 분석하고 자동 최적화를 수행하여 처리율을 최적화하고 블록 RAM 사용률을 줄이며 블록의 동시 실행을 가능하게 하는 마이크로 아키텍처로 전환합니다.

- IP 생성 가속화:

시뮬레이션 가능한 설계를 Vivado IP Integrator 내에서 사용할 수 있는 RTL IP 패키지로 변환하고 플러그 앤 플레이 IP 통합 설계 환경의 모든 이점을 복잡한 설계에 활용할 수 있습니다.

- DSP용 System Generator로 확장:

모델 컴포저의 사용 편의성 및 시뮬레이션 속도 이점을 설계의 일부에 활용하고, 합성된 RTL을 DSP 설계용 기존 System Generator에 새로운 맞춤형 블록으로 내보낼 수 있습니다.

- Vitis HLS로 내보내기:

시뮬레이션에서 기록된 테스트 벡터를 포함하여 알고리즘을 더욱 최적화하는 데 필요한 모든 것을 자동으로 생성함으로써, 알고리즘을 설계, 시뮬레이션, 검증하기 위한 Simulink의 그래픽 환경과 Vitis HLS를 연결하는 고급 기능입니다.

- RTL 인터페이스를 매핑하기 위한 사용자 인터페이스:

구현을 위해 설계의 입력 및 출력을 지원되는 RTL 인터페이스(AXI4-Lite, AXI4-Stream, AXI4-Stream Video, FIFO, 블록 RAM) 및 비디오 형식(AXI4-Stream Video)에 매핑하기 위한 그래픽 인터페이스를 간편하게 사용할 수 있습니다.

자동 테스트 벤치 생성: 시뮬레이션에서 테스트 벡터를 자동으로 기록하고 테스트 벤치를 생성하여 실행 가능한 설계와 생성된 코드 간의 기능적 동등성을 검증합니다.

- 정수, 부동 소수점 및 고정 소수점 지원:

Simulink의 네이티브 부동 및 정수 데이터 형식과 Vitis HLS에서 지원하는 고정 소수점 및 half 데이터 형식을 지원합니다.