-

Principais recursos e benefícios do Vivado IP Integrator

- Perfeita integração dentro do ambiente de projeto incorporado do Vivado

- Inclusão contínua de subsistemas hierárquicos do IP Integrator no projeto geral

- Captura e empacotamento rápidos de projetos do IP Integrator para reutilização

- Suporte para fluxos de projeto gráficos e baseados em Tcl

- Simulação rápida e teste cruzado entre várias visualizações de projeto

- Suporte para todos os domínios de projeto

- Suporte para projetos com e sem processador

- Integração de IP algorítmico (Vitis HLS e Compositor de modelos) e de nível RTL

- Combinação de DSP, vídeo, analógico, incorporado, conectividade e lógica

- Suporte para fluxo de DFX baseado em projeto

- Foco na produtividade do projetista

- DRCs em conexões complexas no nível de interface durante a montagem do projeto

- Reconhecimento e correção de erros comuns de projeto

- Propagação automática de parâmetros de IP para IP interconectado

- Otimizações no nível de sistema

- Assistência ao designer automatizada

- Suporte à colaboração avançada

- Suporte à colaboração avançada

- Os projetos baseados em equipe que usam o Block Design Container possibilitam a reutilização e projetos modulares

- Melhorias no controle de revisão que separam os arquivos de origem dos arquivos gerados

- Ferramenta Block Design Diff para comparar dois projetos de bloco

Recursos do projeto de alto nível

Aqui está uma visão geral rápida dos recursos do Vivado™ Design Suite para acelerar o projeto de alto nível. Clique nas outras guias para obter detalhes completos do recurso.

- Vitis HLS

- IP Integrator

- Abstract Shell

- Vitis Model Composer

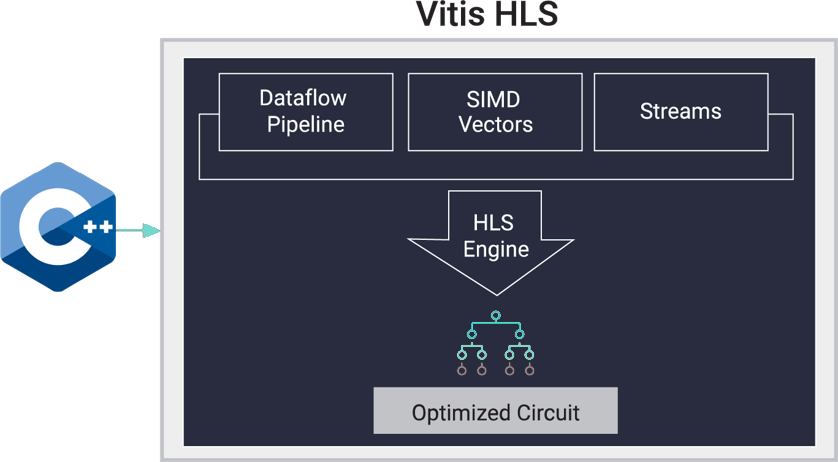

Ferramenta de síntese de alto nível Vitis

Os algoritmos avançados usados atualmente em aplicativos de IA, sem fio, médicos, de defesa e de consumo estão mais sofisticados do que nunca. A ferramenta de síntese de alto nível Vitis™, incluída como uma atualização sem custo em todas as edições do Vivado™, acelera a criação de IP, permitindo que as especificações de C++ sejam direcionadas diretamente para dispositivos programáveis da AMD sem a necessidade de criar manualmente projetos de RTL equivalentes. A ferramenta Vitis HLS é compatível com os ambientes de projeto Vitis e Vivado, e possibilita aos designers de software e hardware acelerar a criação de kernel ou IP por meio de:

- Abstração de descrições algorítmicas, especificações de tipo de dados com números inteiros de ponto fixo ou ponto de flutuação e interfaces (FIFO, memórias, AXI4)

- Bibliotecas extensas para incluir suporte incorporado para tipos de dados de precisão arbitrária, fluxos e tipos de dados vetorizados

- Síntese orientada por diretiva e com reconhecimento de arquitetura com alta QoR

- Tempo rápido para QoR que compete com RTL codificado manualmente

- Verificação acelerada usando simulação de test bench C/C++ e simulação automática de VHDL ou Verilog e geração de test bench

- Uso automático de memórias no chip AMD e elementos de DSP, incluindo tipos de ponto de flutuação

Bibliotecas

As seguintes bibliotecas incorporadas estão incluídas na ferramenta Vitis HLS:

| Nome | Descrição |

|---|---|

Tipos de dados de precisão arbitrária |

Tipos de número inteiro e de ponto fixo (ap_int.h) |

Fluxos de HLS |

Modelos para estruturas de dados de streaming, projetados para obter o melhor desempenho e área (hls_stream.h) |

Tipos de vetor |

Tipos e operações vetorizados (hls_vector.h), incluindo tipos de precisão arbitrária |

HLS Math |

Suporte extensivo para a síntese de bibliotecas matemáticas padrão C (math.h) e C++ (cmath.h). O suporte inclui funções de ponto de flutuação e de ponto fixo: abs, atan, atanf, atan2, atan2, ceil, ceilf, copysign, copysignf, cos, cosf, coshf, expf, fabs, fabsf, floorf, fmax, fmin, logf, fpclassify, isfinite, isinf, isnan, isnormal, log, log10, modf, modff, recip, recipf, round, rsqrt, rsqrtf, 1/sqrt, signbit, sin, sincos, sincosf, sinf, sinhf, sqrt, tan, tanf, trunc |

A ferramenta Vitis HLS também é compatível com as bibliotecas otimizadas para desempenho do Vitis disponíveis no GitHub com aceleração pronta e alterações mínimas ou nulas no código dos aplicativos existentes. Essas bibliotecas aceleradas comuns do Vitis incluem matemática avançada, estatísticas, álgebra linear e DSP para oferecer funcionalidades essenciais para uma ampla variedade de aplicativos. Essas bibliotecas oferecem aceleração para cargas de trabalho, como processamento de imagem e visão com funções OpenCV, finanças quantitativas, banco de dados, análise de dados, compactação de dados e muito mais.

Para obter mais informações, visite o site do Vitis HLS.

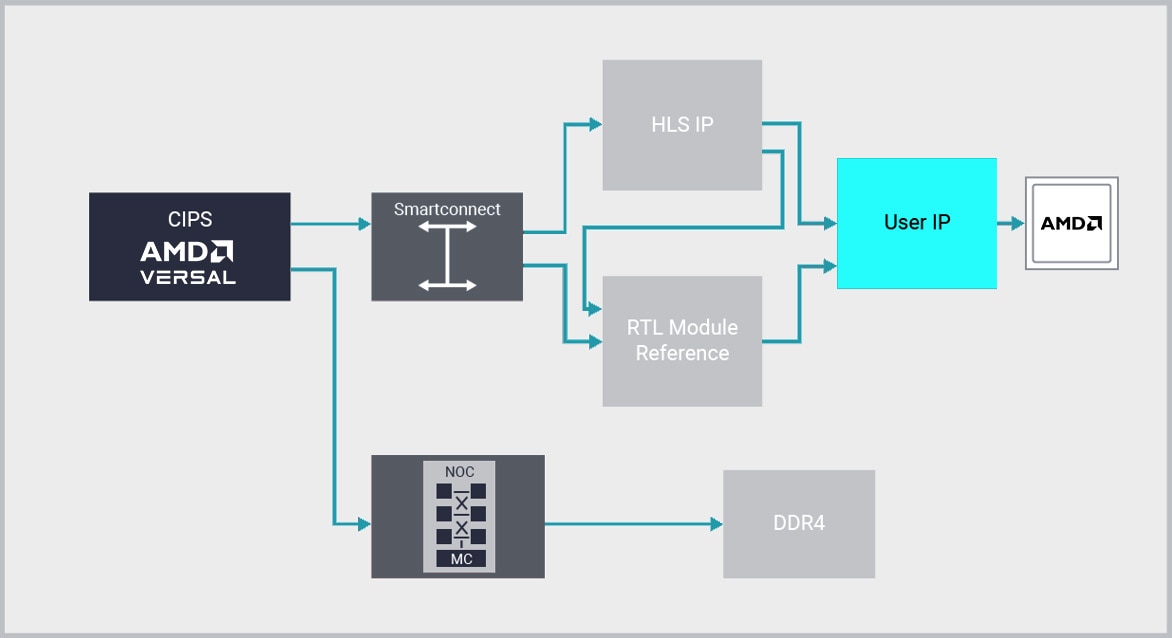

IP Integrator

O Vivado™ Design Suite rompe a estagnação da produtividade de projeto de RTL fornecendo o primeiro ambiente de projeto de integração de IP plug-and-play da indústria, com seu recurso IP Integrator.

O Vivado IP Integrator fornece um fluxo de desenvolvimento de projeto gráfico e baseado em Tcl, correto por construção. Ele fornece um ambiente interativo com reconhecimento de dispositivo e plataforma que oferece suporte à conexão automática inteligente das principais interfaces de IP, geração de subsistema IP com um clique, DRCs em tempo real e propagação de alterações de interface, combinados com uma poderosa capacidade de depuração.

Os projetistas trabalham no nível de abstração de "interface" e não de "sinal" ao fazer conexões entre IP, aumentando muito a produtividade. Muitas vezes, isso é feito usando interfaces padrão da indústria AXI4, mas dezenas de outras interfaces também são compatíveis com o IP Integrator.

Trabalhando no nível de interface, as equipes de projeto podem montar rapidamente sistemas complexos que aproveitam o IP criado com o Vitis HLS, Compositor de modelos, AMD SmartCore™ e LogiCORE™ IP, Alliance Member IP, bem como seu próprio IP. Ao aproveitar a combinação de Vivado IPI e HLS, os clientes estão economizando até 15X em custos de desenvolvimento em comparação com uma abordagem de RTL.

Geração de IP baseada em C com síntese de alto nível Vitis e Compositor de modelos Vitis

Como fornecedora líder de ferramentas de Projeto no nível de sistemas eletrônicos para soluções programáveis, o Vivado fornece síntese de alto nível Vitis™ para C, C++ e SystemC, e é possível comprar um Compositor de modelos Vitis adicional para DSP. Essas soluções possibilitam que as especificações de IP de alto nível sejam sintetizadas diretamente em VHDL e Verilog, acelerando a verificação de IP em 100X e a criação de RTL em até 4X. As ferramentas altamente integradas podem ser usadas individualmente ou em combinação, resultando em IP reutilizável para uso no Vivado Suíte ML.

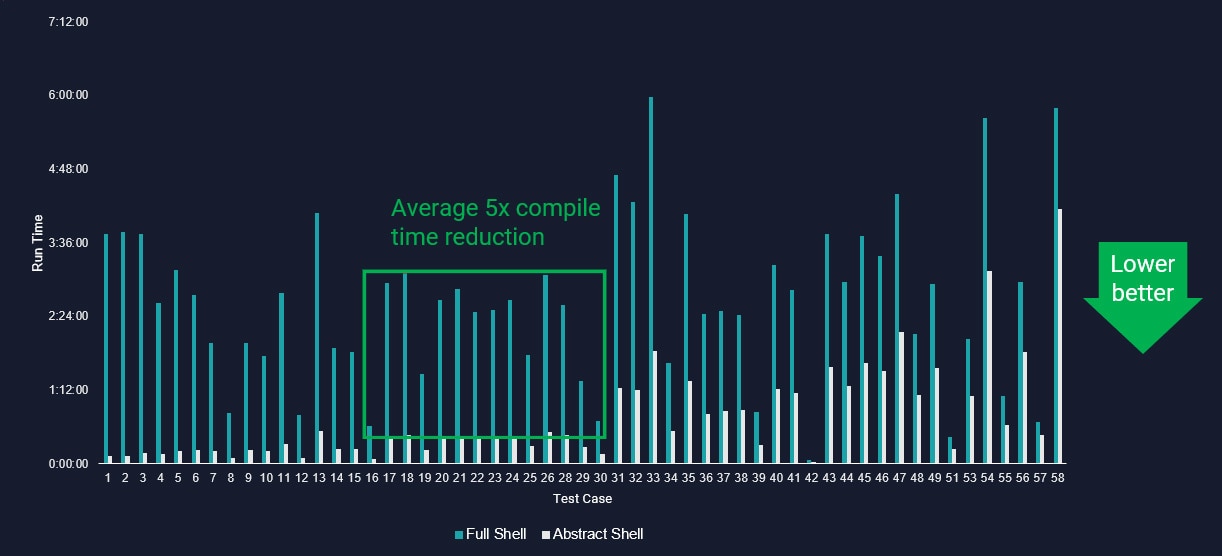

Compilação rápida usando Abstract Shell

O Abstract Shell é uma nova tecnologia que possibilita a compilação rápida para projetos complexos e grandes. Ele permite que os usuários definam módulos reconfiguráveis dentro de um projeto para serem compilados de forma independente. Os usuários podem selecionar partes do projeto para serem modificadas e recompiladas sem precisar recompilar todo o projeto.

O Abstract Shell possibilita uma redução média do tempo de compilação de 5x e até 17x em comparação com uma compilação tradicional. Esses recursos também permitem que os usuários definam vários módulos no projeto que podem ser compilados em paralelo.

Principais recursos

O Abstract Shell possibilita aos usuários:

- Reduzir o tempo de execução e o uso de memória para cada compilação de módulo reconfigurável

- Implementar todos os módulos reconfiguráveis em paralelo para várias partições reconfiguráveis

- Ocultar qualquer informação proprietária existente no projeto estático

- Evitar a verificação de licença para qualquer IP existente no projeto estático

- Distribuir partições reconfiguráveis entre várias equipes para colaboração de projeto baseada em equipe

Depoimentos

Vitis Model Composer

O Compositor de modelos Vitis™ é uma ferramenta de projeto baseada em modelos que possibilita a rápida exploração do projeto no ambiente MathWorks MATLAB® e Simulink® e acelera o caminho para a produção em dispositivos AMD por meio da geração automática de códigos. Você pode projetar seus algoritmos e iterar através deles usando blocos de alto nível com desempenho otimizado e validar a correção funcional por meio de simulações no nível do sistema. O Compositor de modelos Vitis transforma seu projeto em uma implementação com qualidade de produção por meio de otimizações automáticas. A ferramenta fornece uma biblioteca de mais de 200 blocos de mecanismo de IA, HLS e HDL para o projeto e a implementação de algoritmos em dispositivos AMD. Também possibilita a importação do código de mecanismo de IA, HLS e HDL personalizado como blocos para a ferramenta. O Compositor de modelos Vitis inclui todas as funcionalidades do AMD System Generator for DSP, que não é mais fornecido como uma ferramenta independente desde 2020.2.

No Compositor de modelos Vitis, você pode:

- Criar um projeto usando blocos otimizados visando mecanismos de IA e lógica programável.

- Visualizar e analisar os resultados da simulação e comparar a saída com referências de ouro geradas usando MALPAB® e Simulink®.

- Co-simular continuamente os blocos de mecanismo de IA e lógica programável (HLS, HDL).

- Gerar automaticamente o código (gráfico de fluxo de dados de mecanismos de IA, RTL, HLS C++) e testbench para um projeto.

- Importar o código de HLS, mecanismos de IA e RTL personalizado como blocos.

Nota:

O Compositor de modelos Vitis pode ser adquirido como uma licença complementar para qualquer Vivado Design Suite Edition.

Para obter mais informações sobre como baixar e comprar, visite a página do Compositor de modelos Vitis.

Principais recursos

-

Acelere as iterações de projeto

- Alto nível de abstração:

Os blocos de construção centrados em algoritmos, com foco na funcionalidade, fornecem facilidade de uso essencial para especialistas em domínio acelerarem a exploração do projeto.

- Suporte para vetores e matrizes:

Possibilita o projeto de algoritmos baseado em frames que economiza tempo e esforço para mudar para um modelo intermediário de baixo nível para implementação.

- Bibliotecas específicas de aplicativos:

Bibliotecas de DSP, visão computacional, matemática e álgebra linear otimizadas para desempenho disponíveis como blocos para simulação e implementação de alto desempenho em dispositivos AMD.

- Importe C/C++ sintetizável como blocos personalizados:

A capacidade de criar seus próprios blocos personalizados para simulação e geração de código fornece maior flexibilidade para projetar seus algoritmos diferenciados

- Integração perfeita com o Simulink:

A conexão direta com blocos da família de produtos Simulink® possibilita a modelagem e a simulação no nível do sistema e a capacidade de aproveitar totalmente as capacidades de geração de estímulo e visualização de dados do ambiente gráfico do Simulink®.

- Suporte a números inteiros, de ponto de flutuação e ponto fixo:

Suporta os tipos de dados nativos de ponto flutuante e inteiros no Simulink, além dos tipos de dados de ponto fixo e meio compatíveis com o Vitis HLS.

-

Transforme o algoritmo em arquitetura

- Otimizações automáticas:

Analisa sua especificação algorítmica no Simulink e desempenha otimizações automáticas para direcionar para uma microarquitetura que otimiza a produtividade, reduz a utilização da RAM de bloco e possibilita a execução simultânea de blocos.

- Acelere a criação de IP:

Transforme seus projetos simulados em um pacote IP RTL que você pode usar dentro do Vivado IP Integrator e aproveite todos os benefícios do seu ambiente de projeto de integração de IP plug-and-play para projetos complexos.

- Estenda para o System Generator for DSP:

Aproveite os benefícios da facilidade de uso e da velocidade de simulação do Compositor de modelos para partes do seu projeto e exporte o RTL sintetizado para seus projetos existentes do System Generator for DSP como novos blocos personalizados.

- Exporte para o Vitis HLS:

Recurso avançado que fornece um link entre o ambiente gráfico do Simulink para projetar, simular e validar seus algoritmos e o Vitis HLS, gerando automaticamente tudo o que você precisar para otimizar ainda mais seu algoritmo, incluindo vetores de teste registrados da simulação.

- Interface do usuário para mapear interfaces RTL:

Interface gráfica fácil de usar para mapear as entradas e saídas em seu projeto para interfaces RTL compatíveis (AXI4-Lite, AXI4-Stream, AXI4-Stream Video, FIFO, RAM de bloco) e formatos de vídeo (AXI4-Stream Video) para implementação.

Geração automática de test bench: Registro automático de vetores de teste da simulação e geração de uma test bench para verificar a equivalência funcional entre o projeto executável e o código gerado.

- Suporte a números inteiros, de ponto de flutuação e ponto fixo:

Suporta os tipos de dados nativos de ponto flutuante e inteiros no Simulink, além dos tipos de dados de ponto fixo e meio compatíveis com o Vitis HLS.