-

Vivado IP Integrator 主要功能與優點

- Vivado 整合設計環境中的緊密整合

- 將 IP integrator 階層式子系統無縫整合到整體設計中

- 快速擷取和打包 IP Integrator 設計,以供重複使用

- 支援圖形化和 TCL 式的設計流程

- 多個設計視圖之間的快速模擬和交互定位

- 支援所有設計領域

- 支援處理器或無處理器設計

- 整合演算法(Vitis HLS 和模型編輯器)和 RTL 層級 IP

- 結合 DSP、影片、類比、嵌入式、連線能力和邏輯

- 支援以專案為基礎的動態功能交換 (Dynamic Function eXchange, DFX) 流程

- 專為設計人員的工作效率打造

- 支援在設計組裝過程中,對複雜介面層級連線進行 DRC

- 識別和修正常見設計錯誤

- 將 IP 參數自動同步套用到互連的 IP

- 系統層級最佳化

- 自動化設計者協助

- 增強的協作支援

- 增強的協作支援

- 使用 Block Design Container 的跨團隊協作式設計,實現了可重複使用性和模組化設計

- 改善修訂版控制,將來源檔案與生成的檔案分開

- 提供 Block Design Diff 工具,用以比較兩款區塊設計

高階設計功能

以下為加速高階設計的 Vivado™ Design Suite 功能快速概覽。按一下其他索引標籤,以查看完整的功能詳細資料。

- Vitis HLS

- IP Integrator

- Abstract Shell

- Vitis 模型編輯器

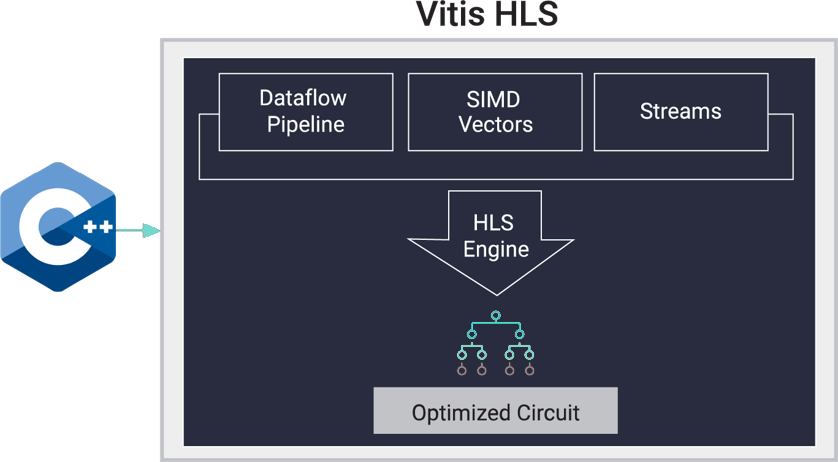

Vitis 高階合成工具

現今在 AI、無線、醫療、國防和消費性應用中使用的進階演算法,比以往任何時候都更加複雜。透過 Vitis™ 高階合成 (High-Level Synthesis, HLS) 工具這套所有 Vivado™ 版本都可經由免費升級取得的產品,設計人員可直接將 C++ 規格指定到 AMD 可程式化器件中,以此加快 IP 建立的速度,無須手動建立等效的暫存器傳輸層 (Register Transfer Level, RTL) 設計。Vitis HLS 工具支援 Vitis 和 Vivado 設計環境,並讓軟體和硬體設計人員同樣都能透過以下功能,加速內核或 IP 建立:

- 演算法描述的抽象化、固定點或浮點整數的資料類型指定,以及介面(先進先出 (First-In First-Out, FIFO)、記憶體、AXI4)

- 齊備多樣的程式庫,針對任意精度資料類型、串流和向量化資料類型提供內建支援.0

- 高成果品質 (quality of results, QoR) 的指示驅動、架構感知合成

- 快速取得理想的 QoR,可與手動編碼 RTL 媲美

- 使用 C/C++ 測試平台模擬,以及自動超高速積體電路硬體描述語言 (Very High-Speed Integrated Circuit Hardware Description Language, VHDL) 或 Verilog 模擬和測試平台生成,達到加速驗證的成效

- 自動使用 AMD 晶片上記憶體和數位訊號處理 (Digital Signal Processing, DSP) 元件,包括用於浮點類型

程式庫

Vitis HLS 工具內建以下程式庫:

| 名稱 | 描述 |

|---|---|

任意精度資料類型 |

整數和固定點 (ap_int.h) 類型 |

HLS 串流 |

串流資料結構模型 — 旨在獲得最佳效能和區域 (hls_stream.h) |

向量類型 |

向量化類型和運算 (hls_vector.h),包括用於任意精度類型 |

HLS 數學庫 |

廣泛支援標準 C (math.h) 和 C++ (cmath.h) 數學函數庫的合成。 支援浮點和固定點函數:abs、atan、atanf、atan2、ceil、ceilf、copysign、copysignf、cos、cosf、coshf、expf、fabs、fabsf、floorf、fmax、fmin、logf、fpclassify、isfinite、isinf、isnan、isnormal、log、log10、modf、modff、recip、recipf、round、rsqrt、rsqrtf、1/sqrt、signbit、sin、sincos、sincosf、sinf、sinhf、sqrt、tan、tanf、trunc |

Vitis HLS 工具還支援可在 GitHub 上取得的 Vitis 效能最佳化程式庫,不僅具備現成可用的加速功能,還能將對於現有應用程式程式碼的變動控制在最低限度,甚至完全沒有。這些常見的 Vitis 加速程式庫包括高階數學、統計、線性代數和 DSP,可為各種應用程式提供核心功能。這些程式庫可加速執行各式各樣的工作負載,包括用 OpenCV 函數加速視覺與影像處理,還有量化金融、資料庫、資料分析、資料壓縮等。

如需更多資訊,請造訪 Vitis HLS 網站。

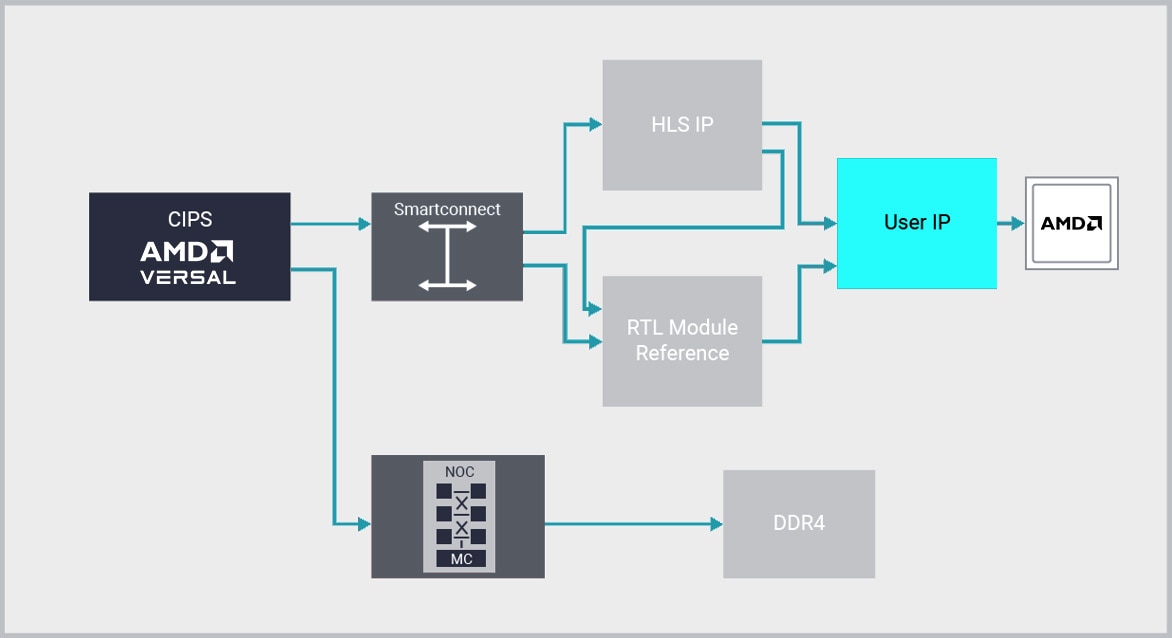

IP Integrator

Vivado™ Design Suite 以其 IP Integrator 功能,提供業界第一個即插即用的 IP 整合設計環境,,突破 RTL 設計工作效率屏障。

Vivado IP Integrator 提供圖形化和以工具命令語言 (Tool Command Language, TCL) 為基礎、設計修正並行的設計開發流程。它提供一個器件和平台感知的互動式環境,支援關鍵 IP 介面的智慧型自動連接、一鍵式 IP 子系統生成、即時設計規則檢查 (Design Rule Checking, DRC),以及介面變更同步套用,並結合強大的除錯功能。

連接不同 IP 時,設計人員是在「介面」而不是「訊號」抽象化層級進行作業,可大幅提高工作效率。通常,這種方法是使用業界標準的 AXI4 介面,但 IP Integrator 也支援許多其他介面。

設計團隊在介面層級上進行作業的優點是可以快速組裝使用 IP 的複雜系統,無論是運用 Vitis HLS 或模型編輯器建立而成的 IP、AMD SmartCore™ 或 LogiCORE™ IP、第三方合作廠商的 IP,還是團隊自行開發的 IP。透過 Vivado IP Integrator (IP Integrator, IPI) 和高階合成 (High-level synthesis, HLS) 的搭配使用,在與 RTL 方法相較之下,客戶可節省高達 15 倍的開發成本。

使用 Vitis 高階合成與 Vitis 模型編輯器生成 C 語言 IP

作為可程式化解決方案的電子系統層級設計工具的一流軟體,Vivado 可為 C、C++ 和 SystemC 提供 Vitis™ 高階合成,如果有 DSP 方面的開發需求,也可以購買附加的 Vitis 模型編輯器。這些解決方案可將高階 IP 規格直接合成至 VHDL 和 Verilog,進而加快 IP 驗證速度逾 100 倍,同時更可加快 RTL 建立速度高達 4 倍。高度整合的工具可以單獨使用,也能夠與可重複使用的 IP 開發成果,在 Vivado ML Suite 中搭配使用。

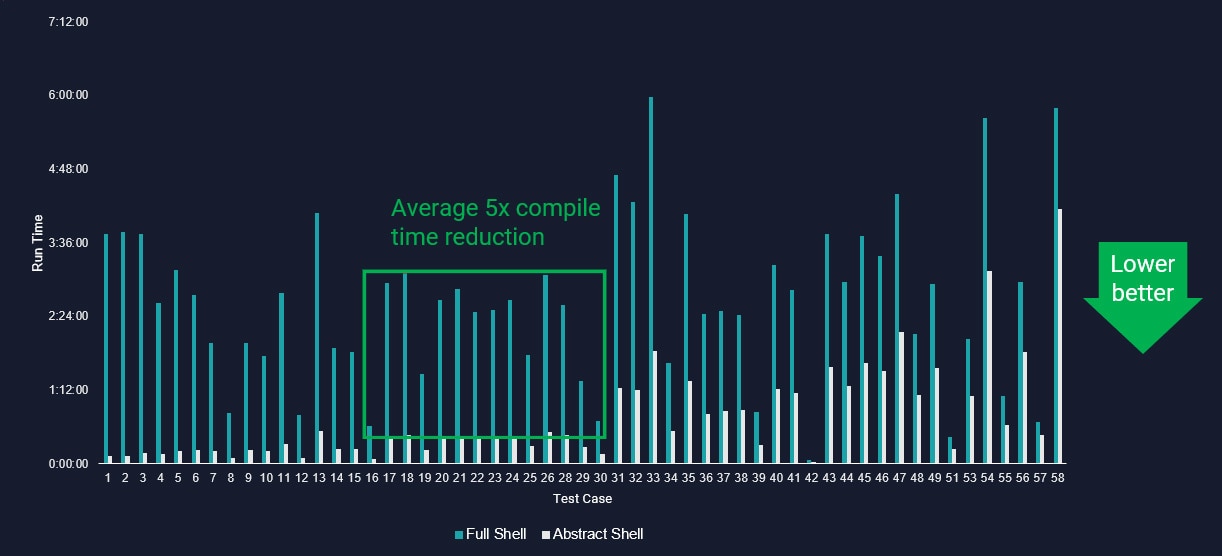

使用 Abstract Shell 快速編譯

主要功能

客戶感言

Vitis 模型編輯器

Vitis™ 模型編輯器是以模型為基礎的設計工具,能在 MathWorks MATLAB® 與 Simulink® 環境中快速進行設計探索,並透過自動產生程式碼,加速 AMD 裝置正式投產的時程。您可以使用效能最佳化的高階區塊來設計演算法並進行迭代作業,同時透過系統級模擬來驗證功能正確性。Vitis 模型編輯器透過自動最佳化功能,將您的設計轉化為量產品品質的實作結果。本工具提供一個含納超過 200 個硬體描述語言 (Hardware Description Language, HDL)、HLS 和 AI 引擎區塊的程式庫,可用於在 AMD 裝置上設計和實作演算法。此外,本工具也支援將客製 HDL、HLS 和 AI 引擎代碼,作為區塊匯入到工具中。Vitis 模型編輯器含括 AMD System Generator for DSP 的所有功能,該軟體自 2020 年 2 月起不再作為獨立工具提供。

在 Vitis 模型編輯器中,您可以:

- 使用針對 AI 引擎和可程式化邏輯的最佳化區塊來建立設計。

- 將模擬結果視覺化並進行分析,然後將相關輸出與使用 MALTAB® 和 Simulink® 生成的黃金參考值進行比較。

- 順暢地共同模擬 AI 引擎和可程式化邏輯(HLS、HDL)區塊。

- 針對設計自動生成代碼(AI 引擎資料流圖、RTL、HLS C++)和測試平台。

- 將客製 HLS、AI 引擎和 RTL 代碼匯入為區塊。

附註:

任何版本的 Vivado Design Suite 都能夠以附加授權形式,購買 Vitis 模型編輯器。

更多有關如何下載和購買的資訊,請造訪 Vitis 模型編輯器頁面。

主要功能

-

加速設計迭代

- 高階抽象化:

建構區塊以演算法為中心並著重於功能性,為領域專家提供加速設計探索所需的易用性。

- 對向量和矩陣的支援:

實現分框式演算法設計,為您節省遷移到中段低階模型進行實作所需的時間和精力。

- 特定應用程式庫:

效能最佳化的 DSP、電腦視覺、數學和線性代數程式庫,可作為區塊使用,在 AMD 裝置上進行模擬和高效能實作。

- 將可合成的 C/C++ 匯入作為客製區塊:

可建立自己的客製區塊以進行模擬和代碼生成,為設計差異化演算法提供更大的彈性

- 與 Simulink 順暢整合:

與 Simulink 產品系列的區塊直接連接,可實現系統層級建模和模擬,並能夠充分利用 Simulink 圖形環境的刺激生成和資料視覺化功能。

- 整數、浮點和固定點支援:

支援 Simulink 中的原生浮點和整數資料類型,以及 Vitis HLS 所支援的固定點和半資料類型。

-

將演算法轉換為架構

- 自動最佳化:

在 Simulink 中分析演算法規格並執行自動最佳化,以向下引導出可最佳化輸送量、降低區塊 RAM 使用率,並實現區塊平行執行的微架構。

- 加速 IP 建立:

將可模擬設計轉換為 RTL IP 套件,供您在 Vivado IP Integrator 中使用,並利用其即插即用 IP 整合設計環境的所有優勢,來進行複雜設計。

- 擴展至 System Generator for DSP:

將模型編輯器的易用性和模擬速度優勢用於設計部分,並將合成的 RTL 匯出到您現有的 System Generator for DSP 設計中,以作為新的客製區塊。

- 匯出至 Vitis HLS:

此進階功能會透過自動生成進一步最佳化演算法所需的一切內容(包括從模擬中記錄下來的測試向量),在 Simulink 的圖形環境與 Vitis HLS 之間提供演算法設計、模擬和驗證方面的連結。

- 用於對映 RTL 介面的使用者介面:

圖形介面易於使用,可將設計中的輸入和輸出對映到支援的 RTL 介面(AXI4-Lite、AXI4-Stream、AXI4-Stream Video、FIFO、區塊 RAM)和影片格式 (AXI4-Stream Video),以便進行實作。

自動生成測試平台:自動記錄模擬中的測試向量,並生成測試平台,以驗證可執行設計和所生成代碼之間的功能等效性。

- 整數、浮點和固定點支援:

支援 Simulink 中的原生浮點和整數資料類型,以及 Vitis HLS 所支援的固定點和半資料類型。