-

Vivado IP Integrator 的主要特性和优势

- 紧密集成在 Vivado 集成型设计环境中

- 将 IP Integrator 分层子系统无缝纳入整个设计中

- 快速捕获和封装 IP Integrator 设计,以实现重复使用

- 支持图形和基于 Tcl 的设计流

- 快速仿真和多个设计视图间交叉探测

- 支持所有设计域

- 支持处理器或无处理器设计

- 算法集成(Vitis HLS 和 Model Composer)和 RTL 级 IP

- 融 DSP、视频、模拟、嵌入式、连接功能和逻辑为一体

- 支持基于项目的 DFX 流

- 专注于提高设计人员生产力

- 在设计装配过程中,对复杂接口级连接进行 DRC

- 常见设计错误的识别和纠正

- 将 IP 参数自动传播到互连 IP

- 系统级优化

- 自动设计辅助

- 增强型协作支持

- 增强型协作支持

- 使用 Block Design Container 的基于团队的设计可实现可重用性和模块化设计

- 版本控制方面的改进,将源文件与生成的文件分开

- 用于比较两个块设计的块设计差异工具

高层次设计功能

下面简要介绍了用于加速高层次设计的 Vivado™ Design Suite 功能。点击其他标签,了解完整的功能详情。

- Vitis HLS

- IP Integrator

- Abstract Shell

- Vitis Model Composer

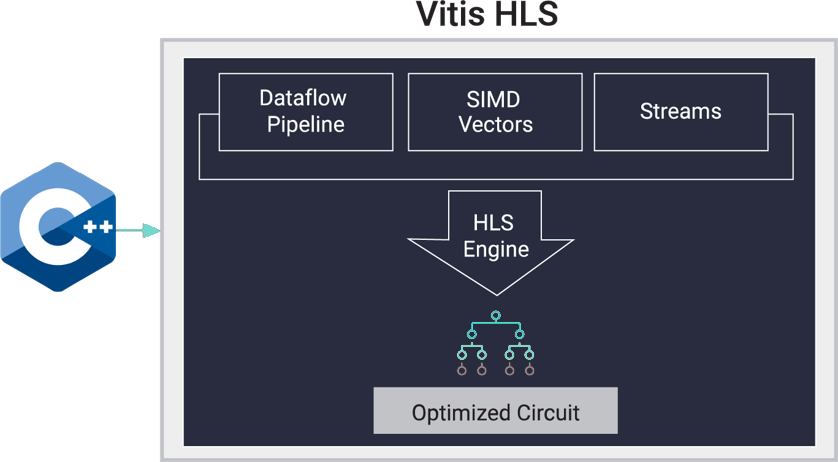

Vitis 高层次综合工具

当今 AI、无线、医疗和消费类应用中使用的高级算法比以往更加复杂。Vitis™ 高层次综合工具在所有 Vivado™ 版本中以免费升级形式提供,可以实现直接使用 C++ 规范对 AMD 可编程器件进行编程,无需手动创建等效的 RTL 设计,从而可加速 IP 创建。Vitis HLS 工具同时支持 Vitis 和 Vivado 设计环境,并使软件和硬件设计者能够通过以下方式加速内核或 IP 创建:

- 算法描述摘要、数据类型规格(定点或浮点整数)以及接口(FIFO、存储器、AXI4)

- 提供丰富的库,包括对任意精度数据类型、流和矢量化数据类型的内置支持

- 具有高 QoR 的指令驱动、架构感知综合

- 在竞争对手还在手动开发 RTL 时快速实现 QoR

- 使用 C/C++ 测试平台仿真、自动 VHDL 或 Verilog 仿真和测试平台生成加速验证

- 自动使用 AMD 片上存储器、DSP 元素,包括浮点类型

库

Vitis HLS 工具包含以下内置库:

| 名称 | 描述 |

|---|---|

任意精度的数据类型 |

整数和定点 (ap_int.h) 类型 |

HLS 流 |

面向流数据结构的模型 - 旨在实现所需性能和面积 (hls_stream.h) |

矢量类型 |

矢量化类型和运算 (hls_vector.h),包括任意精度类型 |

HLS 数学 |

广泛支持标准 C (math.h) 和 C++ (cmath.h) 数学库的综合。 支持浮点和定点函数:abs、atan、atanf、atan2、atan2、ceil、ceilf、copysign、copysignf、cos、cosf、coshf、expf、fabs、fabsf、floorf、fmax、fmin、logf、fpclassify、isfinite、isinf、isnan、isnormal、log、log10、modf、modff、recip、recipf、round、rsqrt、rsqrtf、1/sqrt、signbit、sin、sincos、sincosf、sinf、sinhf、sqrt、tan、tanf、trunc |

Vitis HLS 工具还支持 GitHub 上提供的 Vitis 性能优化库,这些库可实现开箱即用的加速,只需对现有应用进行极少的代码更改,甚至无需进行代码更改。这些常见的 Vitis 加速库涵盖高阶数学、统计、线性代数和 DSP,可为各种应用提供各种核心功能。这些库可为各种工作负载(例如使用 OpenCV 函数进行的视觉和图像处理、定量财务、数据库、数据分析、数据压缩等)提供加速。

有关更多信息,请访问 Vitis HLS 网站。

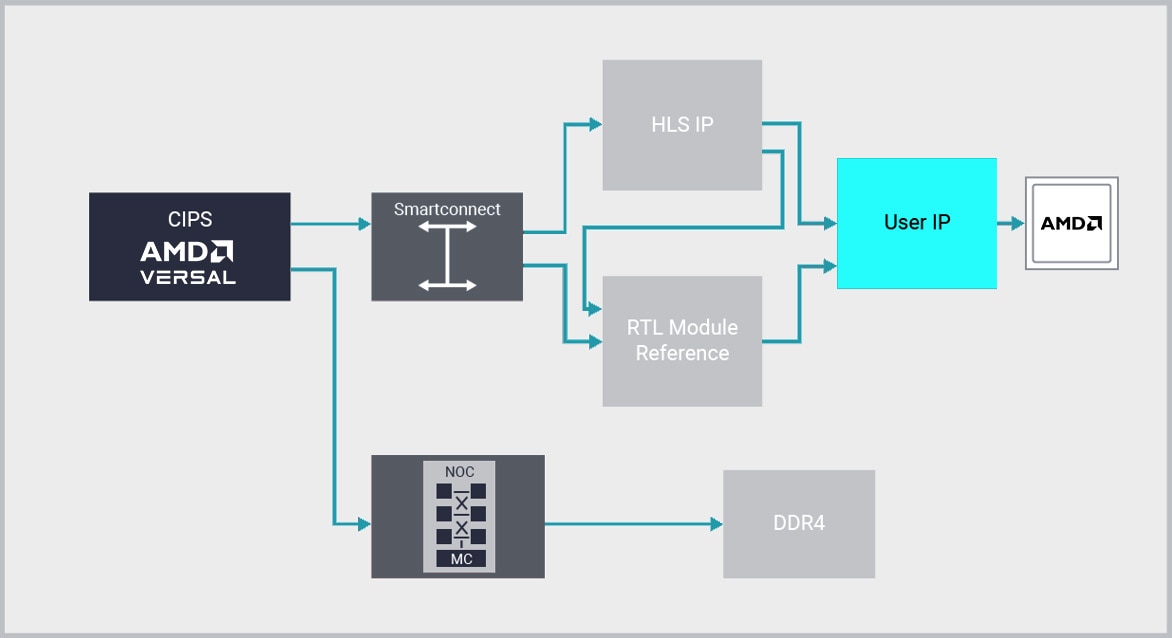

IP Integrator

Vivado™ Design Suite 在业内率先提供即插即用型 IP 集成设计环境,打破了 RTL 设计生产力的瓶颈,其核心功能是 IP Integrator。

Vivado IP Integrator 提供基于 Tcl 的自动建构校正图形化设计开发流程。它可提供具有器件和平台意识的互动环境,能支持关键 IP 接口的智能自动连接、一键式 IP 子系统生成、实时 DRC 和接口修改传递等功能,此外还提供强大的调试功能。

在 IP 之间建立连接时,设计人员工作在“接口”(而不是“信号”)抽象层面上,从而大幅提高了生产力。这通常采用业界标准的 AXI4 接口,不过 IP Integrator 也支持数十个其他接口。

设计团队在接口层面上工作,能快速组装复杂系统,这些系统采用通过 Vitis HLS 和 Model Composer 生成的 IP、AMD SmartCore™ 和 LogiCORE™ IP、联盟成员 IP 以及您自己的 IP。通过结合利用 Vivado IPI 和 HLS,客户可节省高达 15 倍的开发成本(与 RTL 方法相比)。

使用 Vitis 高层次综合和 Vitis Model Composer 生成基于 C 的 IP

作为可编程解决方案电子系统级设计工具的领先供应商,Vivado 提供 Vitis™ 高层次综合,支持使用 C、C++ 和 SystemC 进行设计。此外,您可以购买 Vitis Model Composer 插件,用于 DSP 开发。这些解决方案支持将高层次 IP 规范直接合成到 VHDL 和 Verilog 中,从而将 IP 验证速度提高 100 倍以上,将 RTL 创建速度最多提高 4 倍。这些高度集成的工具可以单独使用,也可以组合使用,最终生成可在 Vivado ML Suite 中重复使用的 IP。

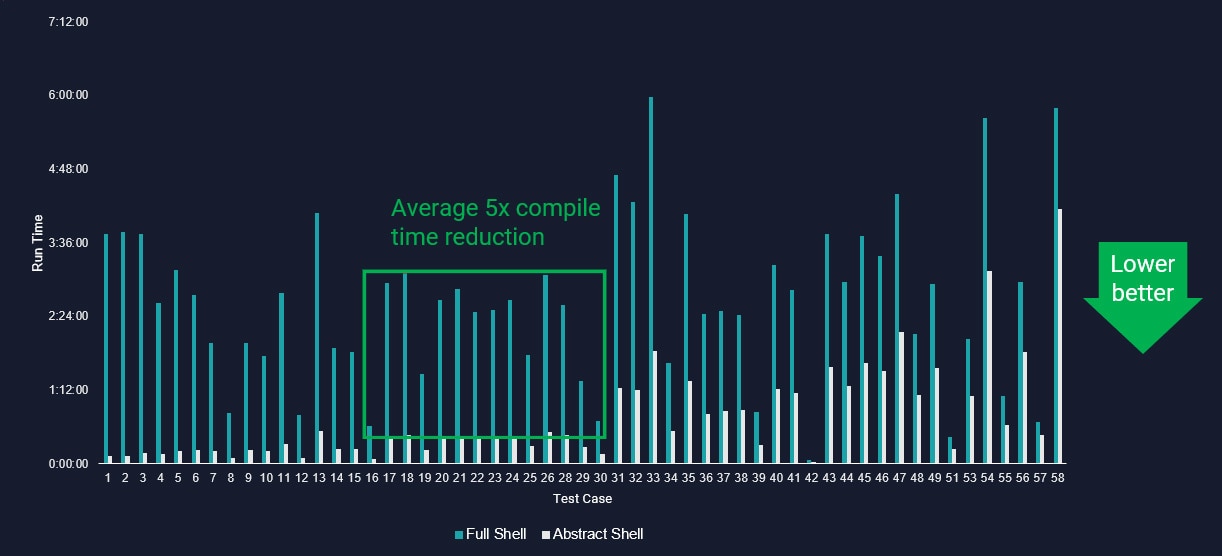

使用 Abstract Shell 快速编译

主要功能特性

客户评价

Vitis Model Composer

Vitis™ Model Composer 是一款基于模型的设计工具,不仅可在 MathWorks MATLAB® 和 Simulink® 环境中实现快速设计探索,而且还可通过自动生成代码在 AMD 器件上加速投产进程。您可以设计自己的算法,并使用高层次性能优化块对其进行迭代,还可通过系统级仿真验证功能的正确性。Vitis Model Composer 可通过自动优化将您的设计转换为达到生产质量的实施方案。该工具提供一个具有 200 多个 HDL、HLS 和 AI 引擎模块的库,用于在 AMD 器件上设计和执行算法。此外,它还允许将自定义 HDL、HLS 和 AI 引擎代码以块形式导入工具中。Vitis Model Composer 包含 AMD System Generator for DSP 的所有功能性,自 2020.2 版起,System Generator for DSP 不再作为独立工具提供。

在 Vitis Model Composer 中,您可以:

- 使用针对 AI 引擎和可编程逻辑的优化块创建设计。

- 可视化和分析仿真结果,并将输出与使用 MALTAB® 和 Simulink® 生成的黄金参考进行比较。

- 无缝协同仿真 AI 引擎和可编程逻辑(HLS、HDL)块。

- 为设计自动生成代码(AI 引擎数据流图,RTL,HLS C++)和测试激励文件。

- 以块形式导入自定义 HLS、AI 引擎和 RTL 代码。

注意:

Vitis Model Composer 可作为任何 Vivado Design Suite Edition 的附加许可证购买。

有关如何下载和购买的更多信息,请访问 Vitis Model Composer 页面。

主要功能特性

-

加速设计迭代

- 高层次抽象:

算法主导型构建块以功能性为重点,可为域专家加速设计探索提供至关重要的易用特性。

- 支持矢量和矩阵:

支持基于帧的算法设计,节省了迁移到中级低层次模型进行实现的时间和精力。

- 应用专用库:

性能优化 DSP、计算机视觉、数学和线性代数库可作为块在 AMD 器件上进行仿真和实现高性能。

- 以自定义块形式导入可综合 C/C++:

能够创建您自己的自定义块,以进行仿真和生成代码,这可为设计差异化算法提供更大的灵活性

- 与 Simulink 无缝集成:

与 Simulink 产品系列的块直接连接,不仅可实现系统级建模和仿真,而且还能够充分利用 Simulink 图形环境的激励生成和数据可视化功能。

- 整数、浮点和定点支持:

支持 Simulink 中的本机浮点和整数数据类型以及 Vitis HLS 支持的定点和半数据类型。

-

将算法转换为架构

- 自动优化:

不仅可在 Simulink 中分析算法规范,以及执行自动优化,以转向针对吞吐量进行优化的微架构,还可降低块 RAM 利用率并实现块的并发执行。

- 加速 IP 创建:

将支持仿真的设计变成您可在 Vivado IP Integrator 中使用的 RTL IP 封装,并将即插即用 IP 集成设计环境的所有优势运用到复杂设计中。

- 扩展到 System Generator for DSP:

利用 Model Composer 的易用性和仿真速度优势,针对设计的部分内容进行开发,并将综合后的 RTL 作为新的自定义块导出到现有的 System Generator for DSP 中。

- 导出到 Vitis HLS:

这种高级特性可自动生成您在进一步优化算法时将会用到的一切(包括从仿真中记录的测试矢量),从而在用以设计、仿真和验证算法的 Simulink 图形环境与 Vivado HLS 之间建立关联。

- 映射 RTL 接口的用户界面:

通过易于使用的图形界面,将设计中的输入和输出映射至所支持的 RTL 接口(AXI4-Lite、AXI4-Stream、AXI4-Stream 视频、FIFO 和块 RAM)和视频格式(AXI4-Stream 视频),以便于实现。

自动生成测试激励文件:自动从仿真中记录测试矢量并生成测试激励文件,以验证可执行设计和所生成代码之间的功能对等性。

- 整数、浮点和定点支持:

支持 Simulink 中的本机浮点和整数数据类型以及 Vitis HLS 支持的定点和半数据类型。